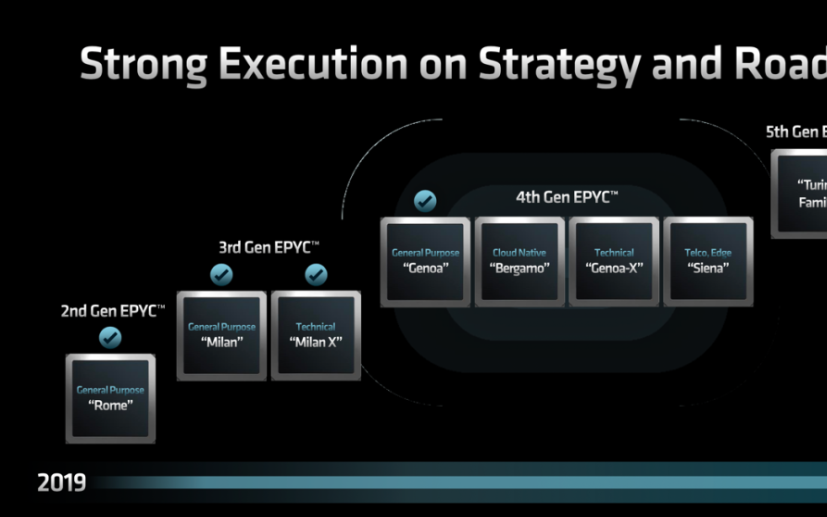

AMD在上周举行的EPYC Horizon Event上重点发布了全新的第二代EPYC 7002 系列处理器,采用Zen2架构的 Ryzen和EPYC 两大产品系列都完整发布了,此后就开始转向新一代架构,发布会上 AMD虽然没有公布新的路线图,但却对外透露了少部分的发展方向,确认Zen3 架构已经开发完成,代表AMD 下一代 CPU 架构进入最终阶段,预计 Zen3 的产品最快在 2020 年就会问世。目前AMD凭借Ryzen 3000系列处理器,在市场竞争中对于Intel已经处于优势地位,但英特尔的10nm处理器马上就要上市了,所以AMD依然不敢掉以轻心,通过加快新处理器的研发进度来持续压制Intel。

AMD对Zen 架构的改进及发展已经非常熟练,Zen3 将会升级采用7nm EUV 工艺,相比目前的Zen 2架构的 7nm DUV 工艺,可将电晶体密度提升20%,同频率下功耗最多可下降 10%,AMD 官方表示 Zen3 的设计目标就是优异的能耗比,与Zen 2架构相比会有适度的IPC性能提升,对于Zen2 架构采用的Chiplets设计,Zen 3 架构仍会继续使用,实际上两代设计变化不会太大,所以流片失败的风险是非常小的。

对于普通的电脑用户而言,比较关心的当然是桌面级的Ryzen处理器,根据之前的消息,下一代 Ryzen 4000 系列升级为Zen 3 架构、代号为Vermeer,将会用上7nm+ CPU 与 12nm I/O设计,最高端型号会采用16 核32 线程设计,并会沿用 AM4 接口和DDR4内存。 在 Zen 3 之后,再下一代的 Zen 4 架构就会正式接手,目前我们只知道 EPYC 系列的架构代号为「Genoa」,更多其他的细节没有披露,目测很有希望上5nm工艺,发布时间则至少在 2021 年。

需要注意的是,AMD曾经承诺过AM4 接口会用到2020年,因此 Zen4 架构的这一代处理器很可能开始更换处理器的接口,同时内存应该会换上新一代,可能就会升级支持DDR5 及 PCIe 5.0 等新技术了。

-

amd

+关注

关注

25文章

5705浏览量

140393

发布评论请先 登录

汇编器在 CodeWarrior 中不合法是怎么回事?

马斯克宣布: A15完成设计,未来芯片迭代快过AMD和英伟达

新品上市!AMD Zynq UltraScale+MPSoC EG异构多处理开发平台

AMD 推出锐龙 AI 嵌入式处理器产品组合,为汽车、工业和物理 AI 领域提供 AI 驱动的沉浸式体验

应用开发准备工作

那么龙芯CPU性能如何呢?

DDR200T中DDR的使用与时序介绍

请问rt-thread studio可以开发完整的mcu程序吗?

如何在AMD Vitis Unified 2024.2中连接到QEMU

江波龙企业级DDR5 RDIMM率先完成AMD Threadripper PRO 9000WX系列兼容性认证

适用于Versal的AMD Vivado 加快FPGA开发完成Versal自适应SoC设计

AMD ZEN3开发完成 ZEN4准备中

AMD ZEN3开发完成 ZEN4准备中

评论