技巧1:“新”技能 hierarchies警告寻找

在编译之后,警告中“hierarchies”这个单词大家估计都很熟悉了,一看到这个警告,基本上就是例化时出现的问题。一般例化时,要是哪个连线没引出,没接上,或者是位宽不匹配就会出这个警告。而我们一般就会定位到例化文件,或者是观察RTL视图去寻找,但是工程一大可不是那么好找的啊!

Warning: 1 hierarchies have connectivity warnings - see the Connectivity Checks report folder

解决方法如下:

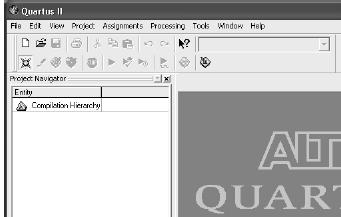

点击图6.1中的图标,然后在Analysis & Synthesis 文件中找到 connectivity checks,如图6.2所示,点击即可查看到说明例化时哪里出现问题。

图6.1 操作(一)

图6.2 操作(二)

技巧2:位宽不匹配

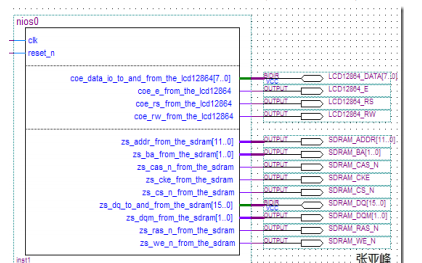

在很多对reg变量进行赋值时,往往会遇到位宽不匹配的情况,如图6.3所示。其中前面括号中的数字代表在程序中所在的行标,说明赋值是32位宽,被赋值为1位宽,也就是将32位宽进行截断去匹配1位宽。若是在程序中知道确实是赋值reg类型变量是一位一位传送的,可以不用关注此警告,如图6.4所示的程序。可以看到确实需要赋值reg变量中的一位即可。若是想消除此警告,可以利用图6.5所示的修改程序。即将0改成1’b0即可,Quartus中若是对变量不进行赋位数,按32位处理。编译后的结果如图6.6所示。

图6.3 位宽不匹配

图6.4 源程序

图6.5修改后的程序

图6.6编译后的结果

技巧3:tcl文件的利用

在引脚分配时,往往对于一个浩大的工程来说,引脚数量是很多的,若是一个一个去分配,费时费力,劳民劳财,其实可以利用tcl文件,只需更改几个信号说明就可以。如图6.7所示,图中标注的更改成模块中所用的信号名字即可。图6.8是quartus ii中的操作步骤,点击Tcl scripts,再点击图6.9中所出现的位置,即可。图6.10是pin planner中分配情况。

图6.7 tcl文件

图6.8 quartus ii中的操作(一)

图6.9 quartus ii中的操作(二)

图6.10 pin planner分配情况

技巧4:jic固化文件的生成

点击file ---- convert programming file,出现如图6.11所示的界面。在programming file type中选择.jic,在configuration device中选择 EPCS4(这个根据你使用板卡的配置芯片选择,笔者设计的是EPCS4),然后在选择图6.12中的flash loader,点击device,然后选择器件类型,笔者设计的是EP3C5芯片。在选择 sof data,将sof文件加载过来,点击 generate出现生成成功界面。然后打开工程目录下中的output files就可以看到所生成的jic文件,如图6.14所示。然后再进入到编程下载界面,如图6.15所示,点击add file,将刚才生成的jic文件加载过来,如图6.16所示,将原sof文件删掉,并选择 program/configure,点击start即可,然后重新上电观察效果。

图6.11 配置界面(一)

图6.12 配置界面(二)

图6.13 配置界面(三)

图6.14 生成的jic文件

图6.15 下载界面

图6.16 添加jic文件

-

引脚

+关注

关注

16文章

1197浏览量

50579 -

quartus

+关注

关注

16文章

171浏览量

74647

发布评论请先 登录

相关推荐

quartus ii使用教程,中文教程

Quartus II 11.0 软件的安装指南

如何制作一个方便在Quartus II和Nios II中使用的简单IP

使用Quartus II编程CPLD和FPGA设备的教程说明

4个Quartus II使用技巧

4个Quartus II使用技巧

评论