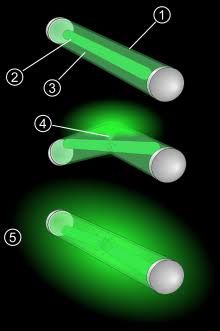

第1步:什么是自发光元素?

简单的自发光元素将能量存储在光线中,并且由于PHOSPHORE而将能量暴露在黑暗中。 。

在黑暗中发光也被称为“LUMINESC ENE“

实例; act,钚,镭,氡,氚和一些生物发光

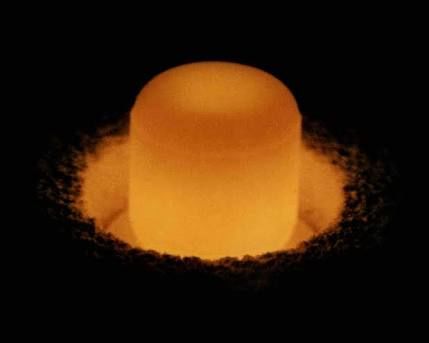

第2步:为什么选择镭?!

》》 RADIUM是一种放射性元素,当它下降时会发出淡蓝色。..。

》》并且它也会发出绿色PHOSPHORE在黑暗中的颜色。..。

》》 RADIUM的名称为RA,原子序数为88,位于元素周期表第2族的第六元素中。

》》镭是一种高放射性元素,可能是非常危险的。..。所以请不要试图让它回家

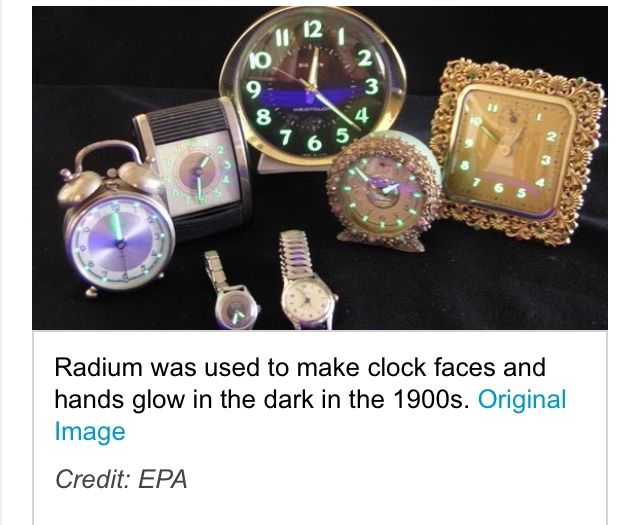

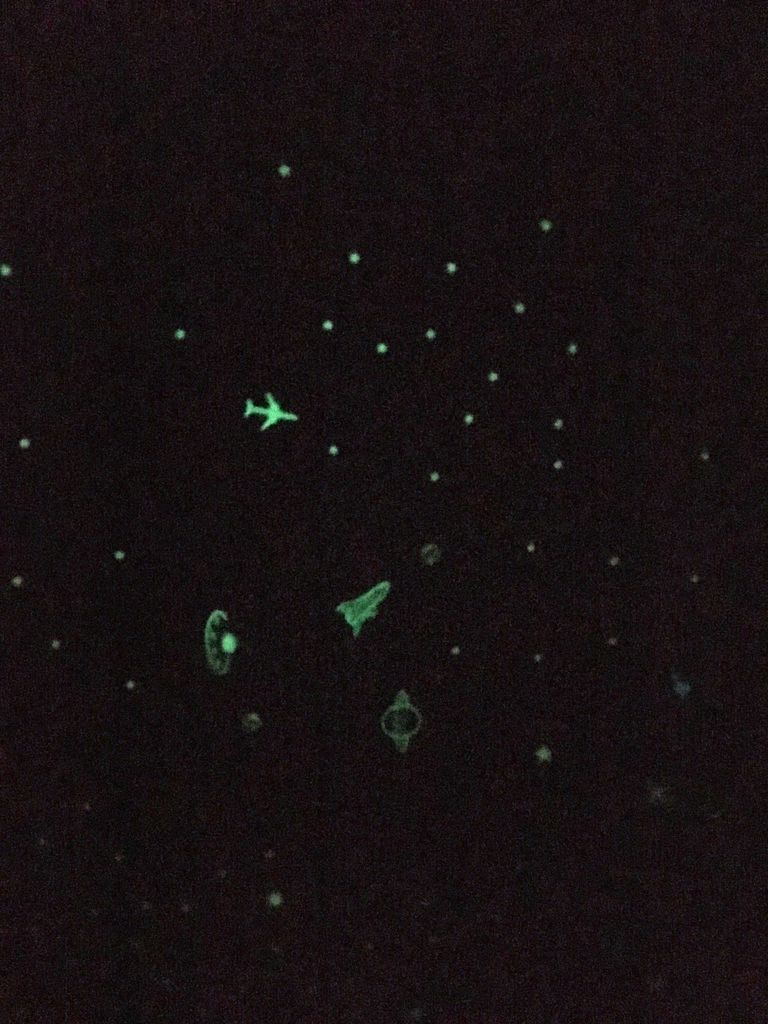

第3步:在哪里找到这些元素?

$$无论是作为我们孩子卧室天花板上的一颗星星,我们周围的黑暗元素都会发光,,, $$腕带,在玩具中常见。

由于极度危险我不会在家里进一步使用镭壁装饰贴纸让时光焕然一新。.

在尝试这个想法之前,我尝试了3种不同类型的RADIUM风味元素,即RADIUM胶带,RADIUM油漆(在线商店)和RADIUM手腕带(本地商店),这些都与想象的最终结果不符,因此我决定使用RADIUM墙壁装饰贴纸。 。.

步骤4:所需的工具

无需特殊工具即可完成此任务。..您家中可用的工具足以完成此任务。 。

+镭墙装饰贴

+锋利的刀或剪刀

+铅笔

+刻度

+螺丝刀(解锁时钟背上的螺丝) + Glu

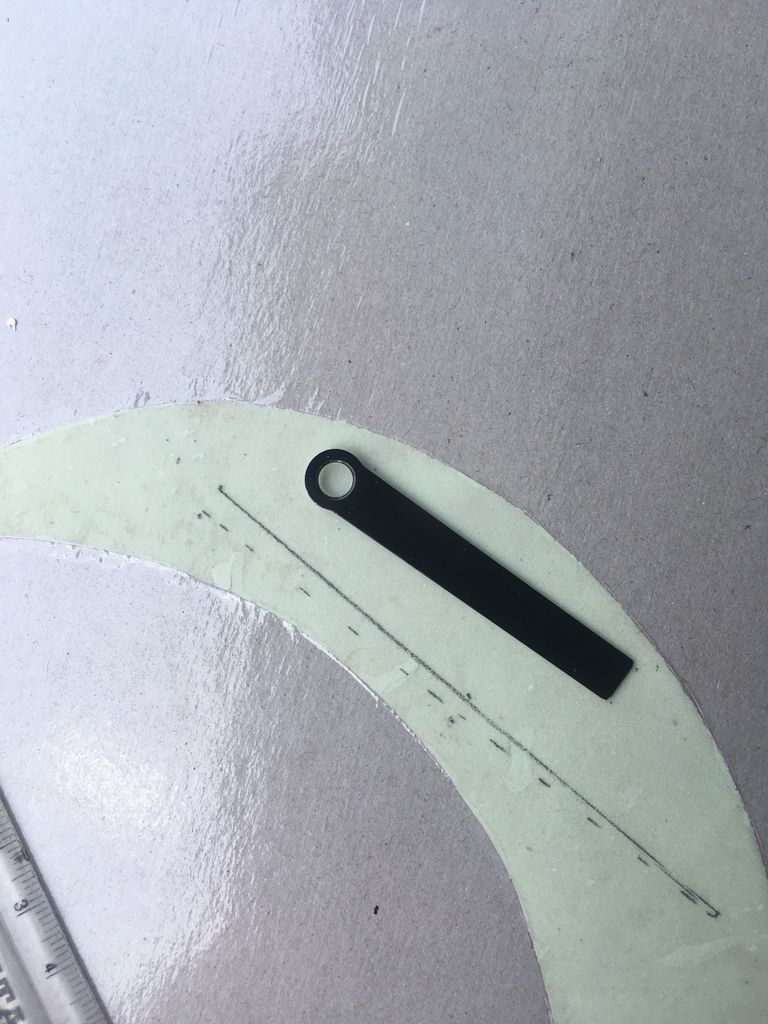

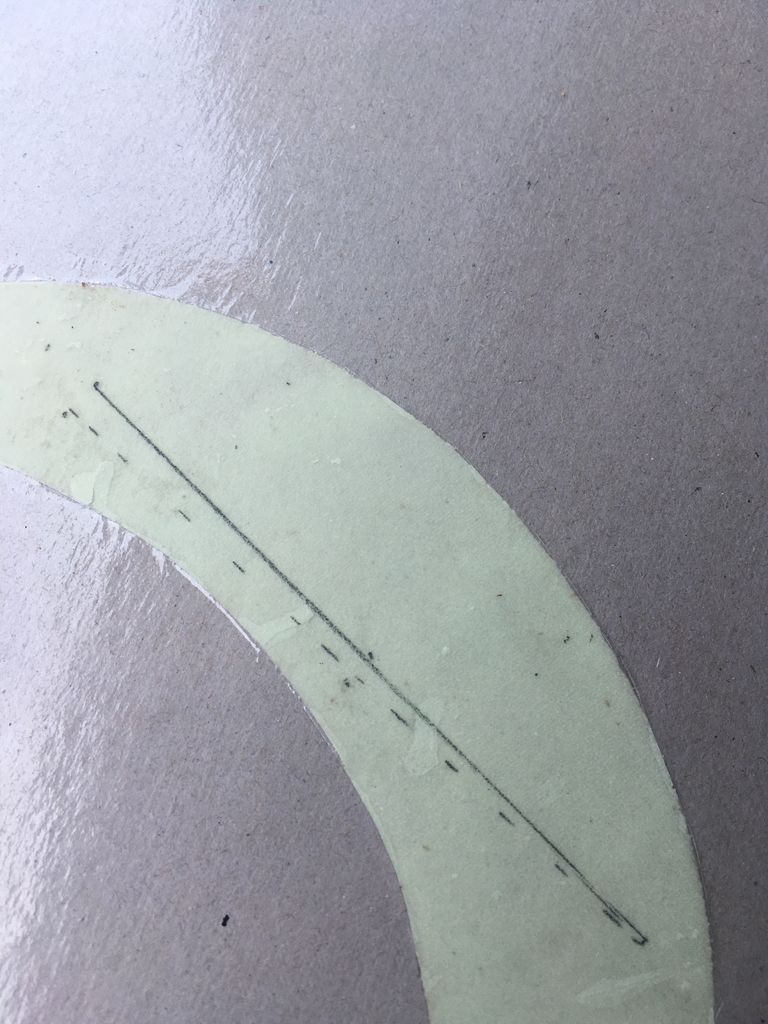

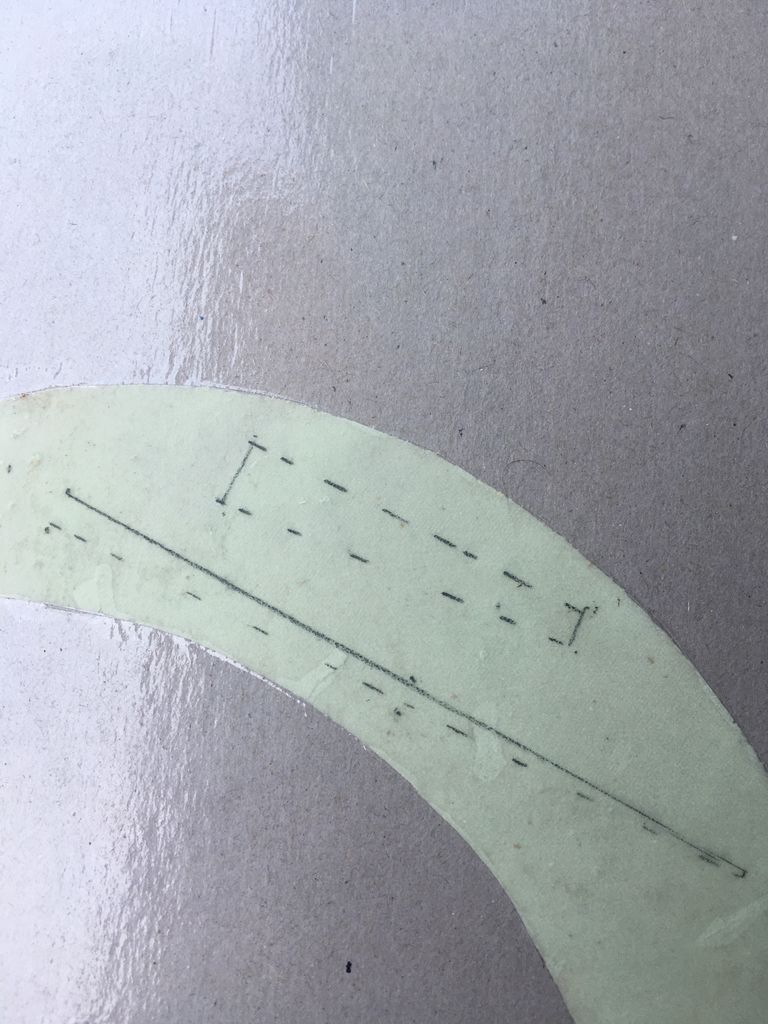

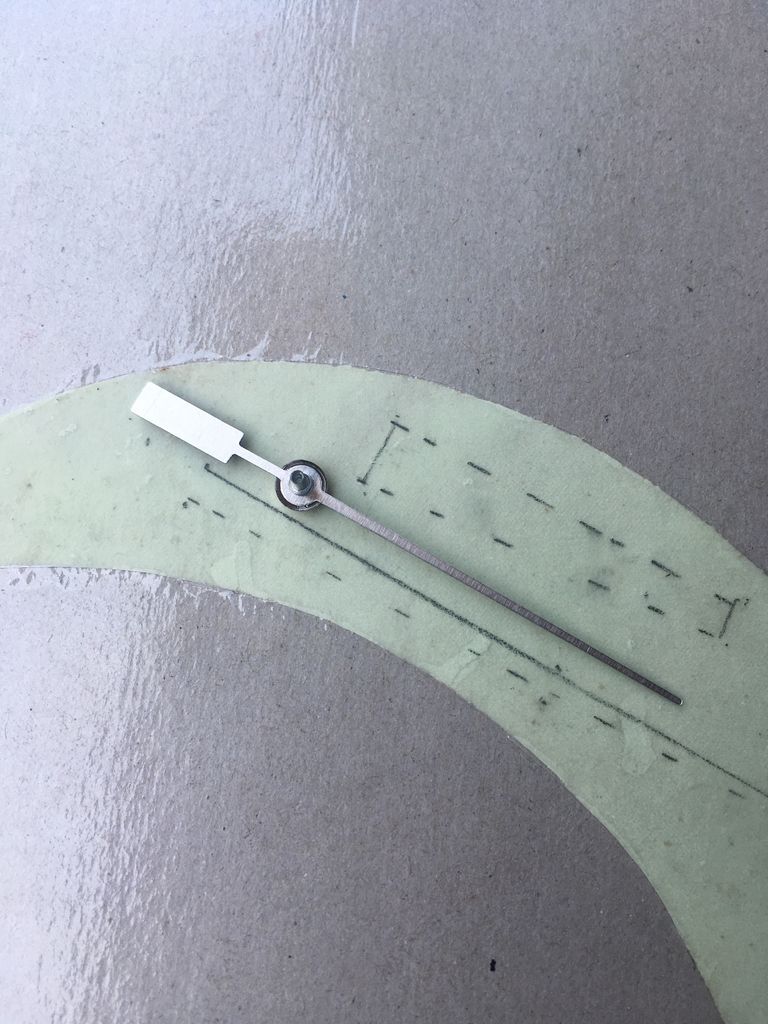

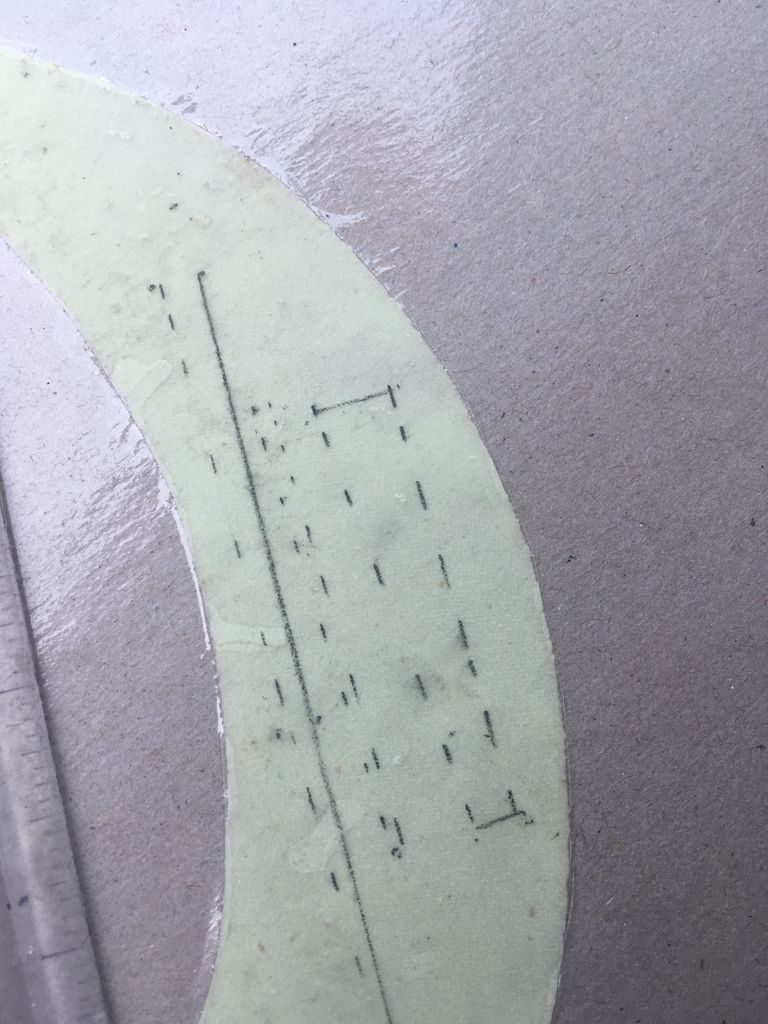

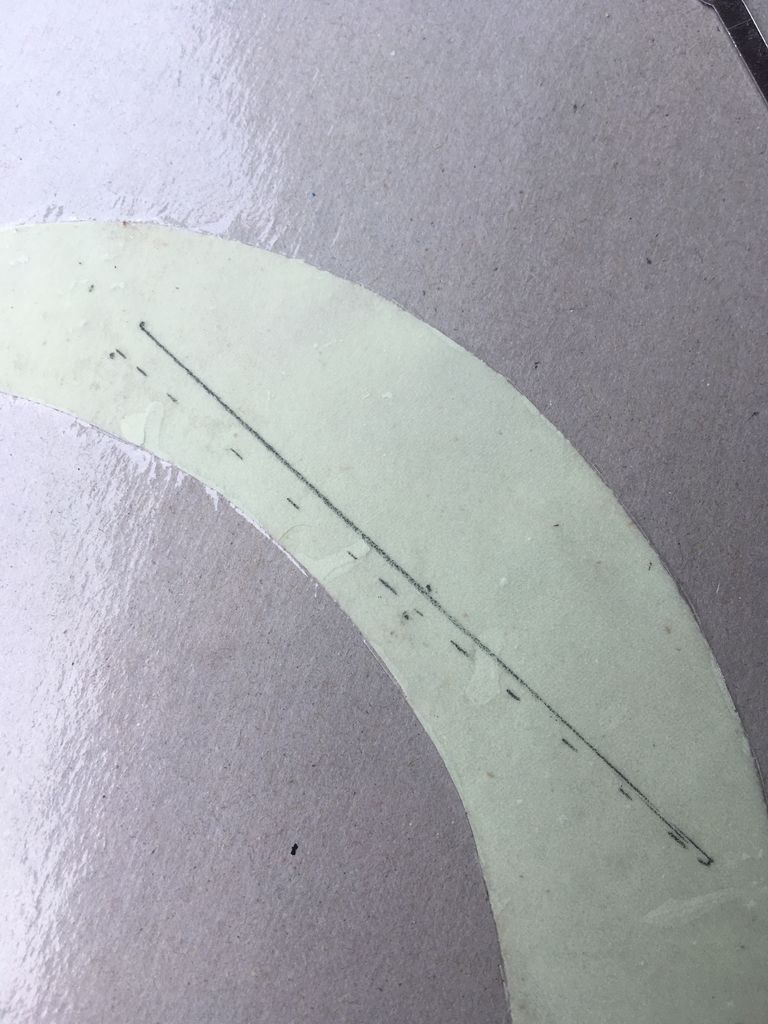

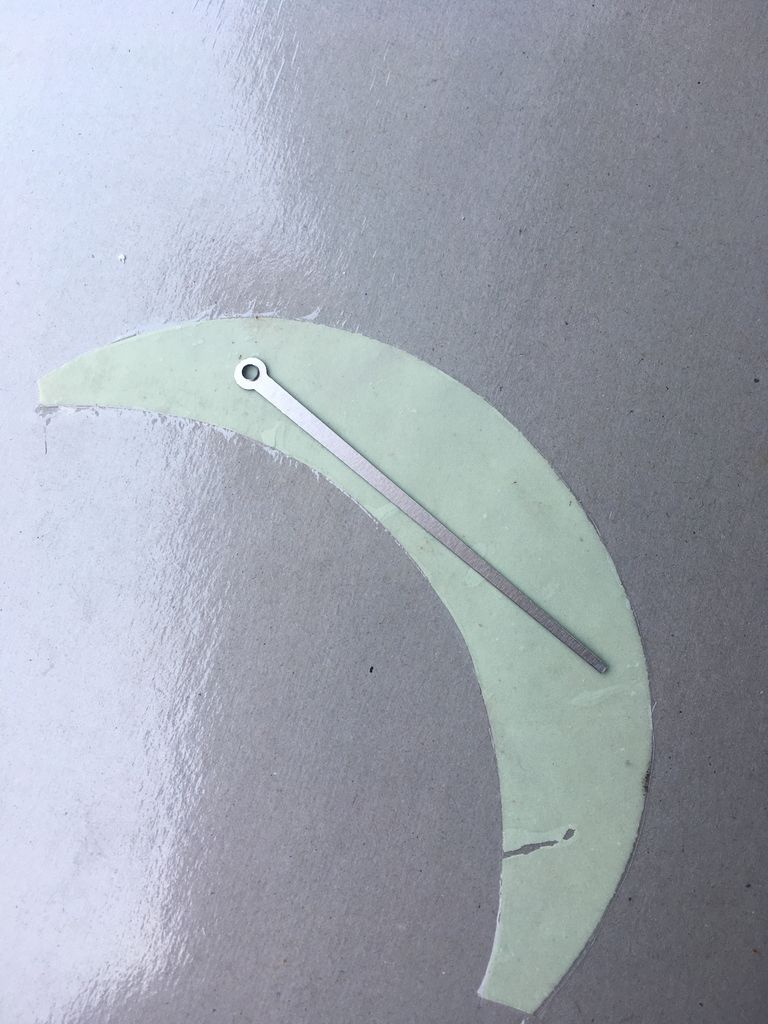

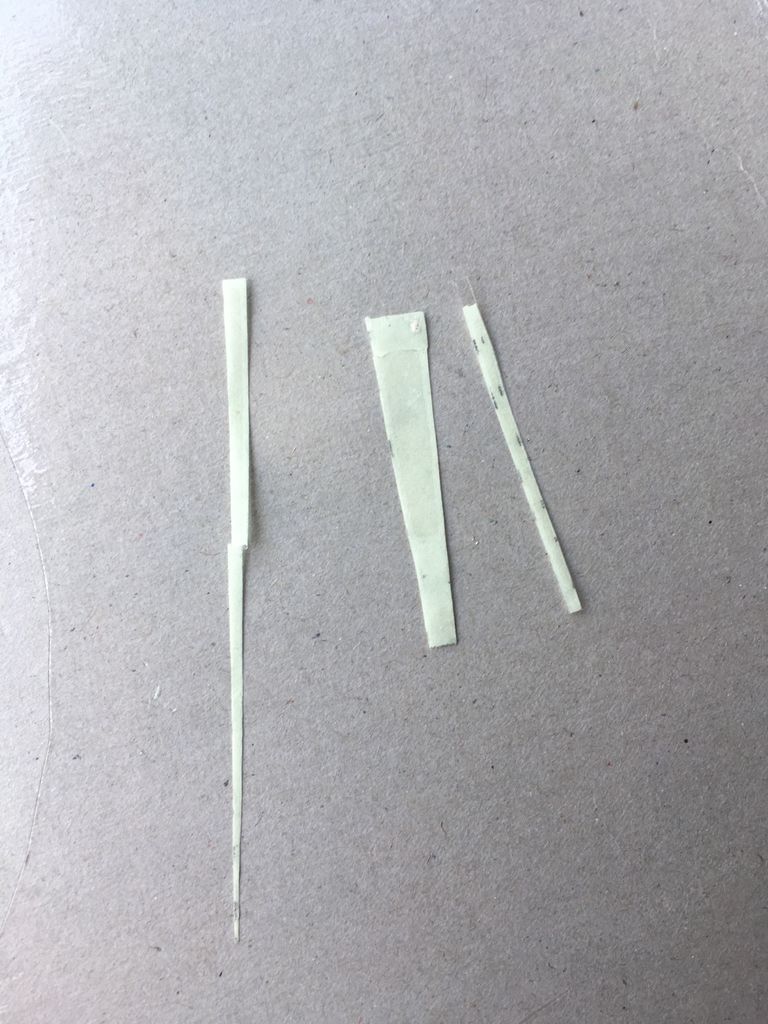

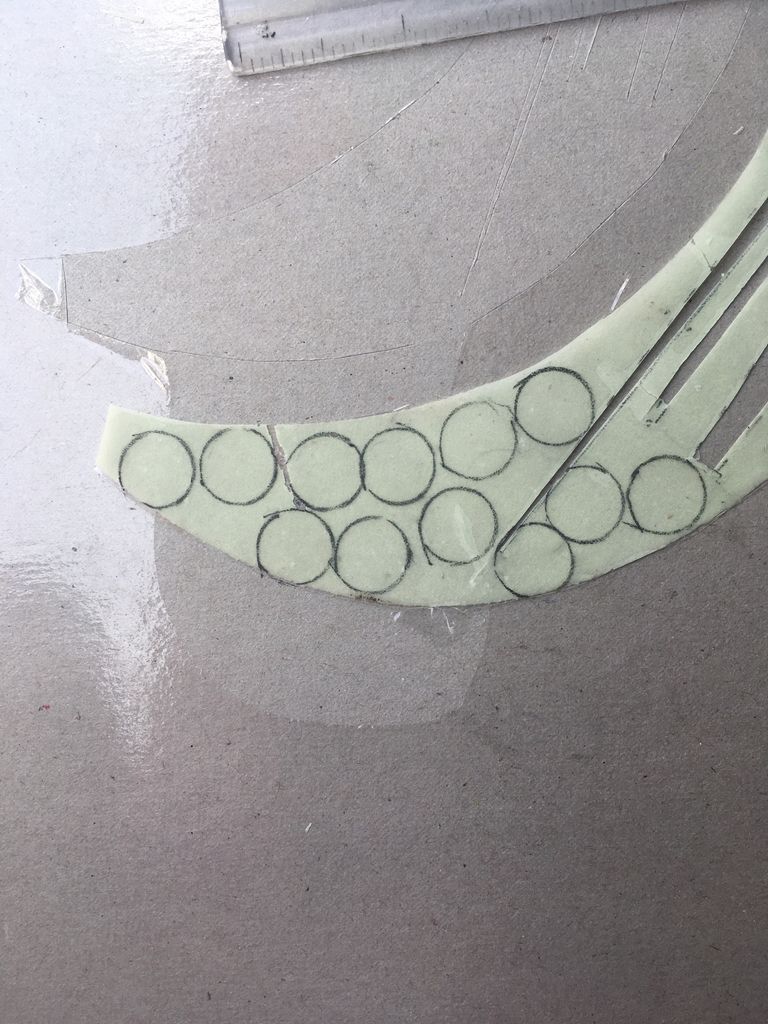

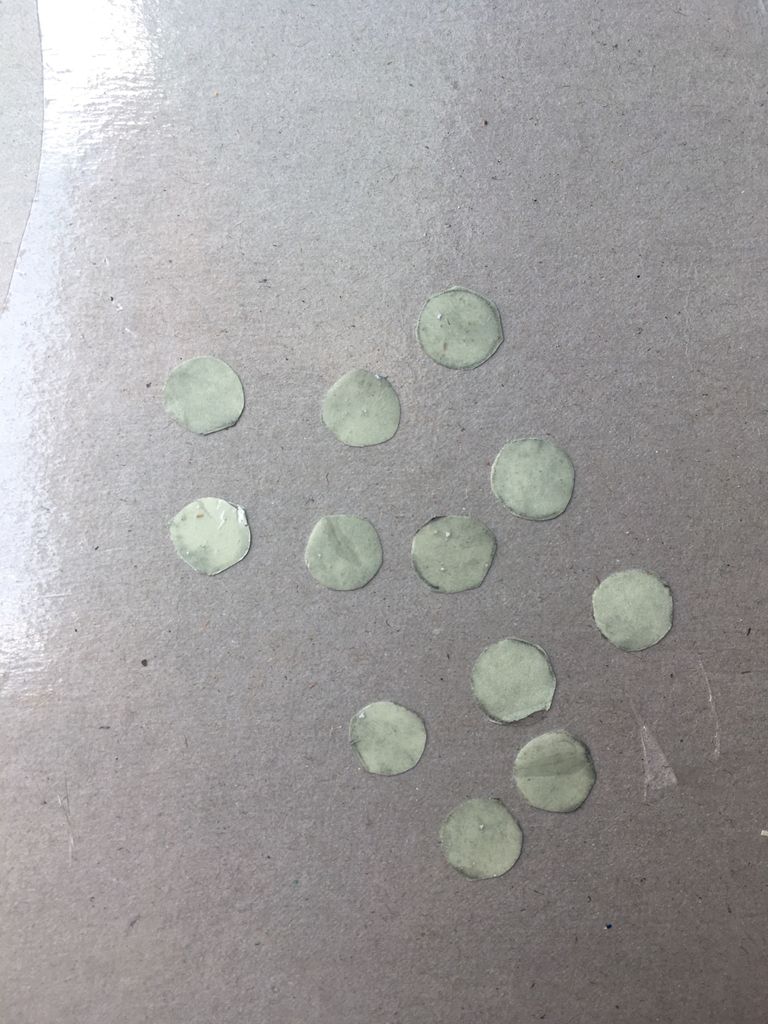

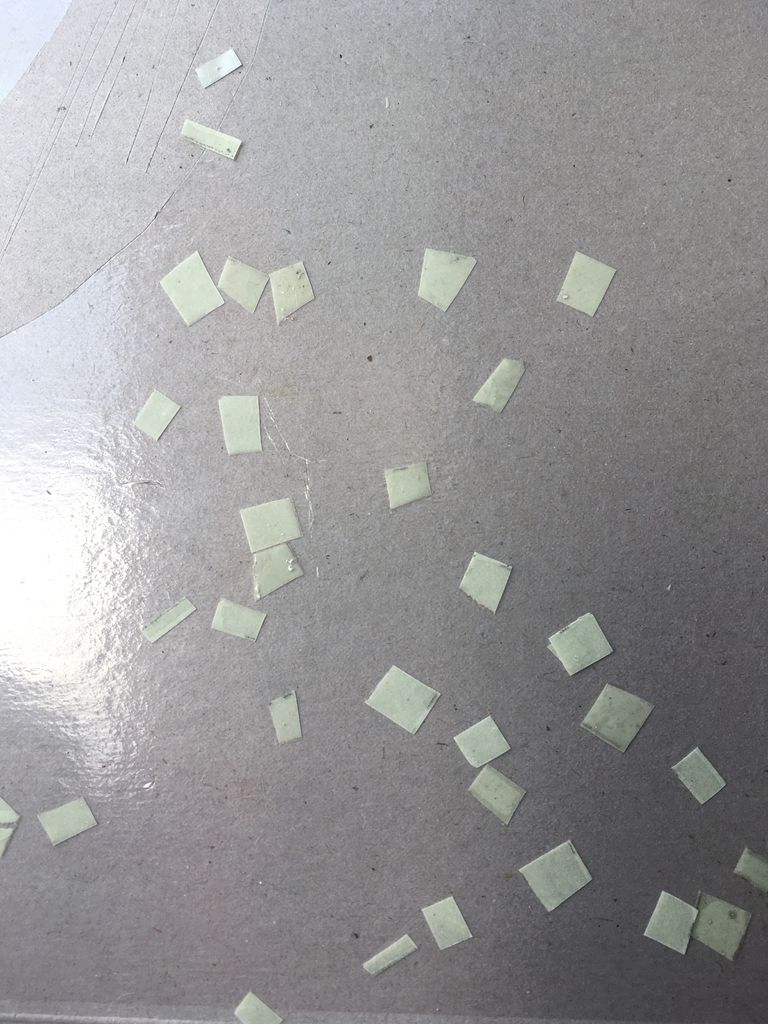

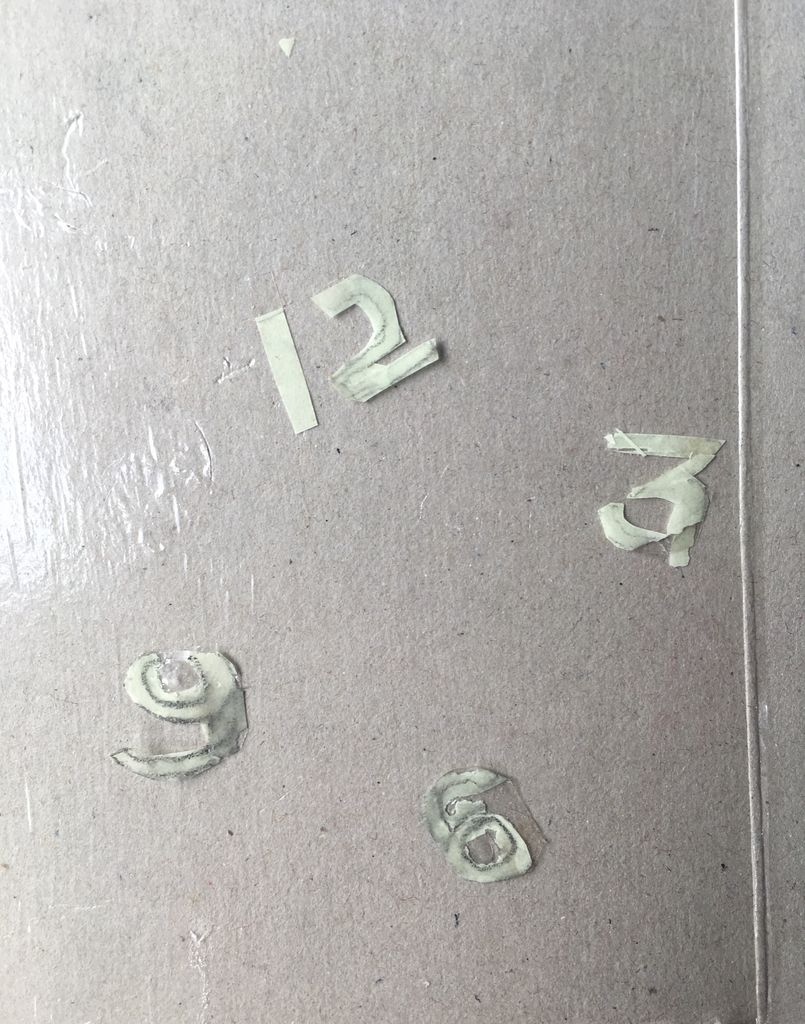

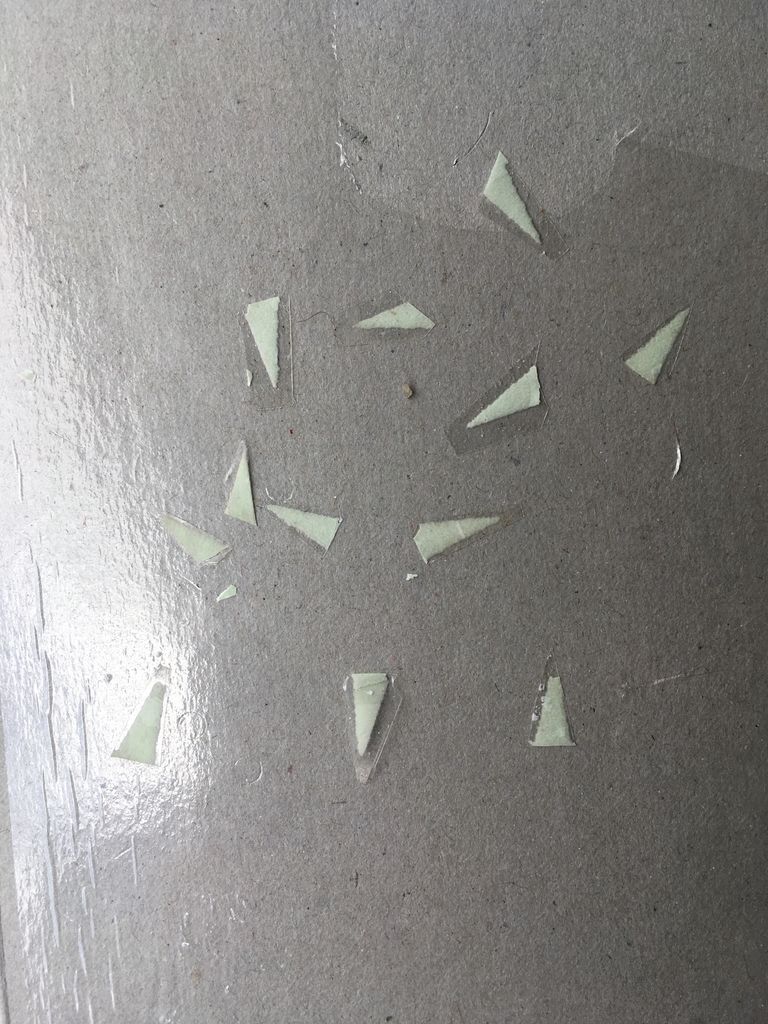

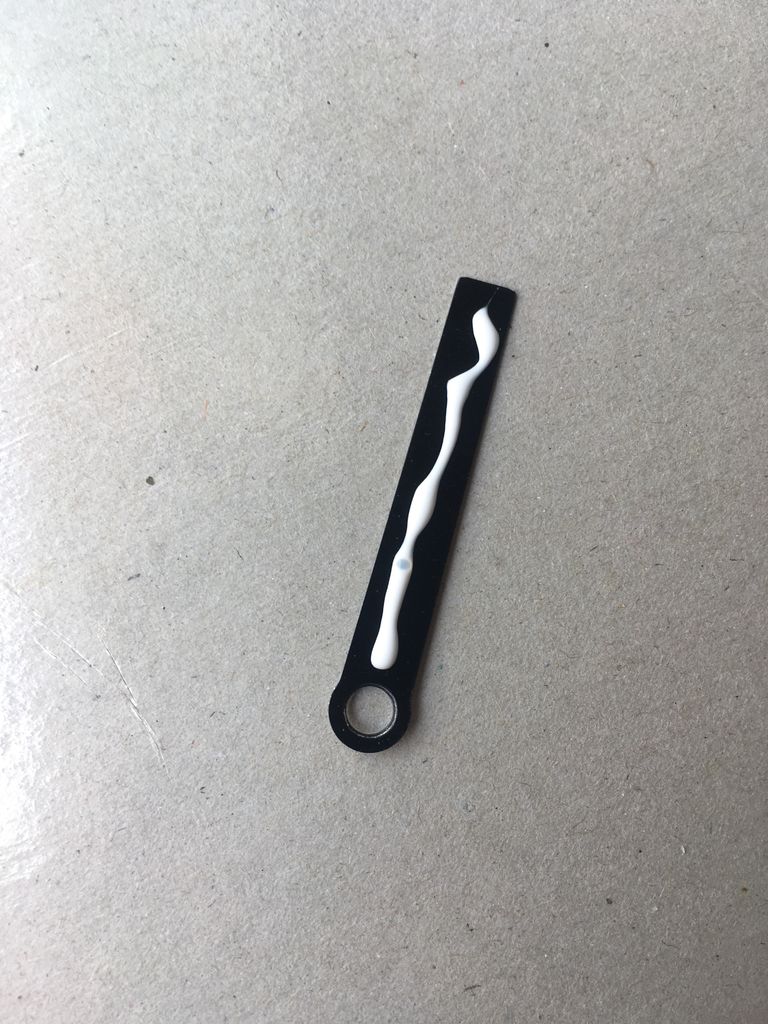

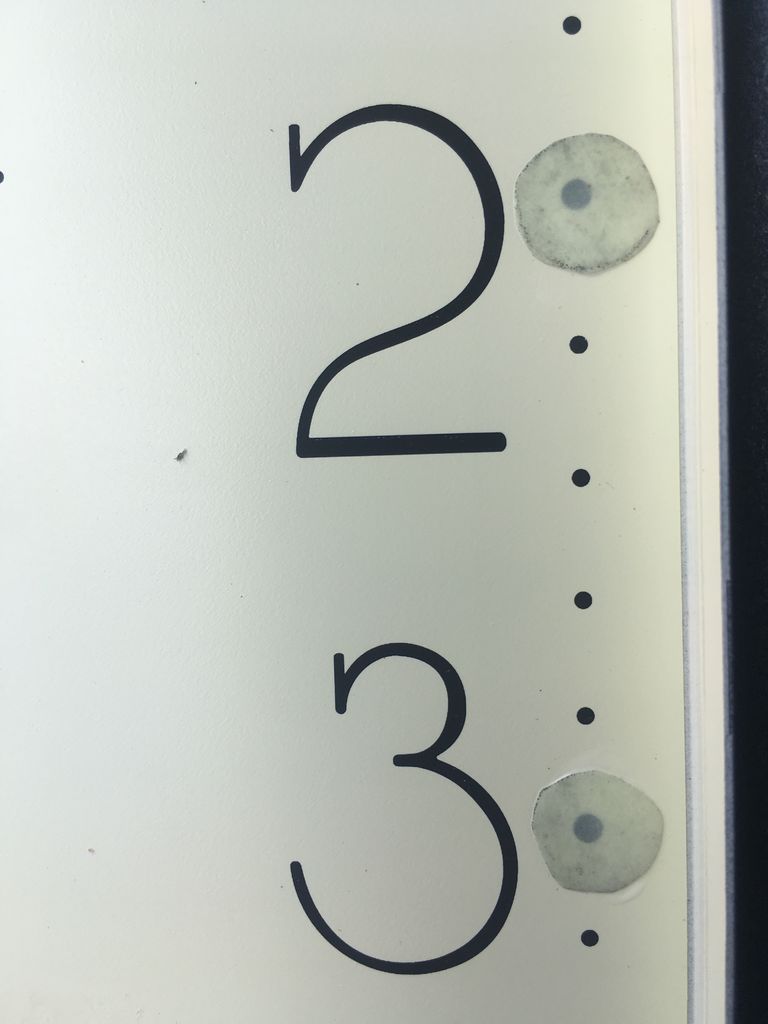

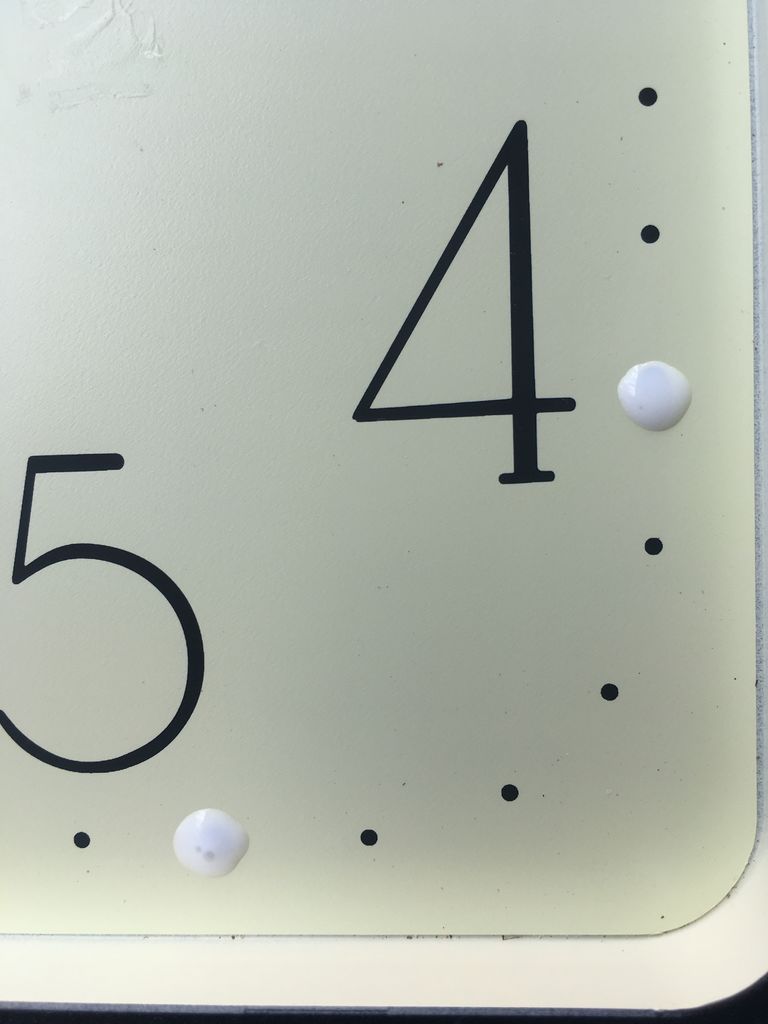

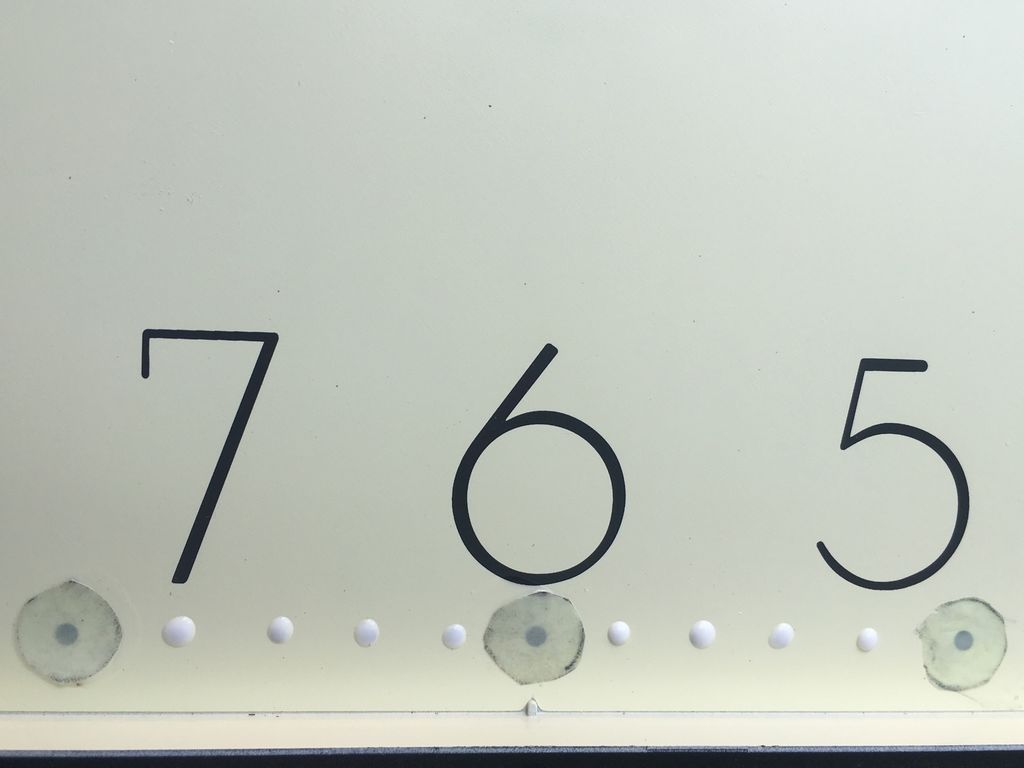

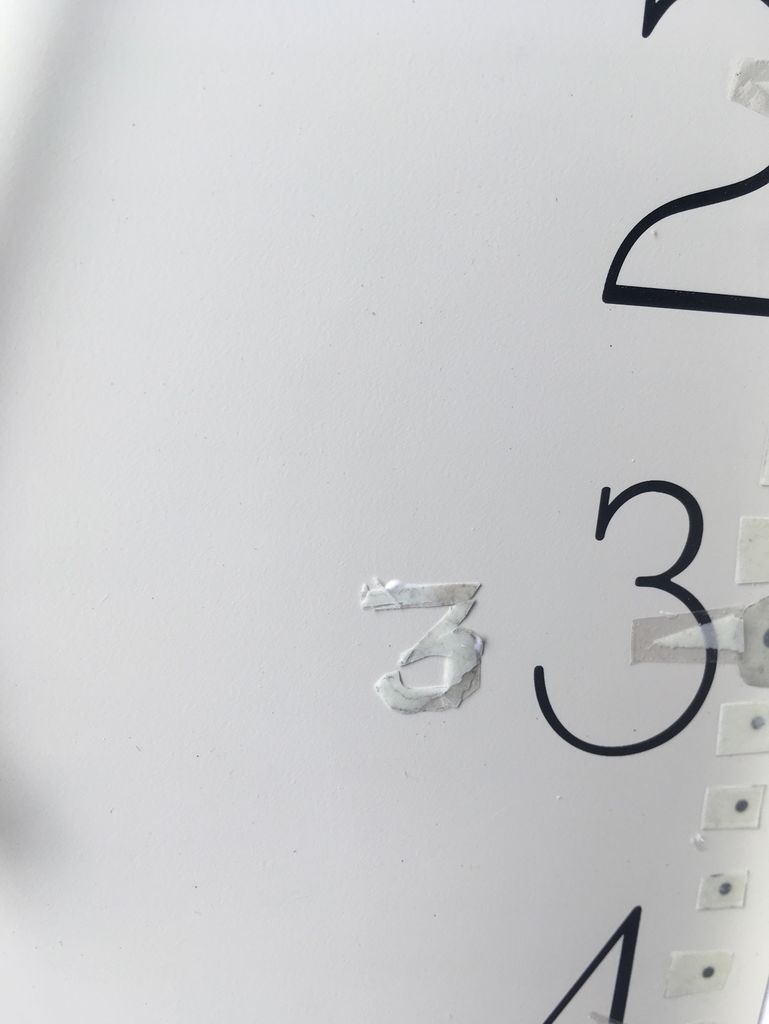

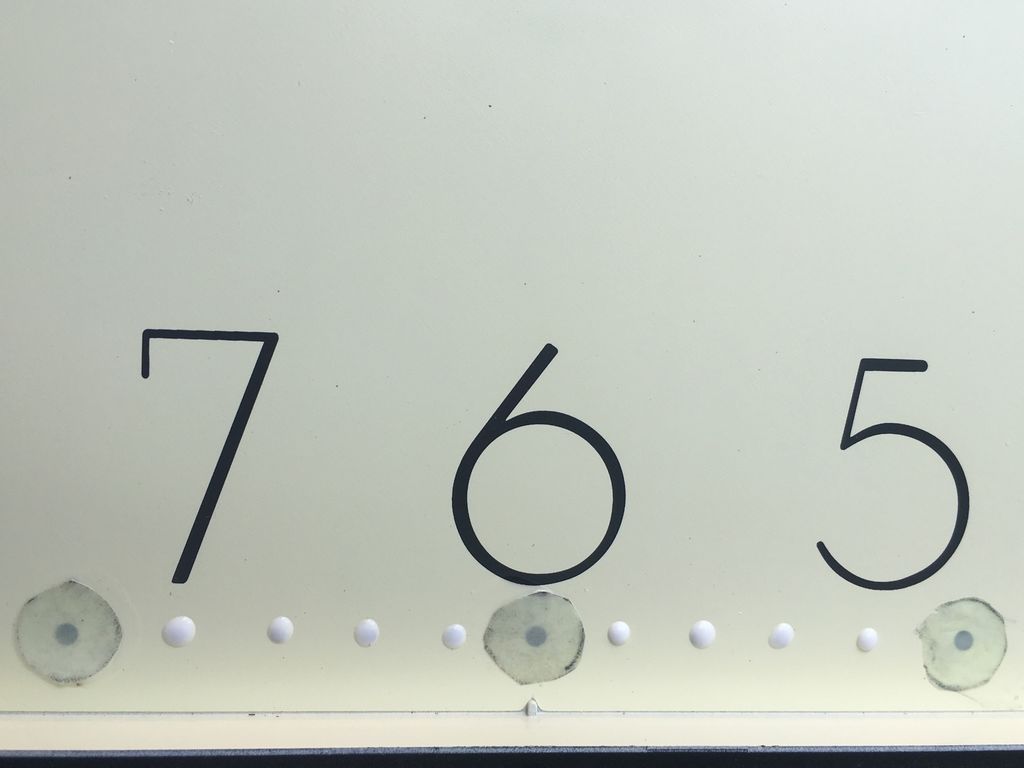

步骤5:将镭标签剪切到小时和分钟指示

》》这在RADIUM条上没有标记尺寸,因此您将在时钟刻度盘上标记形状和数字样式形状。

》》切割标记通过任何尖锐的介质或使用剪刀。

》》喜欢这样切割时钟表,分钟指示器,小时指示器和数字样式的所有需要。

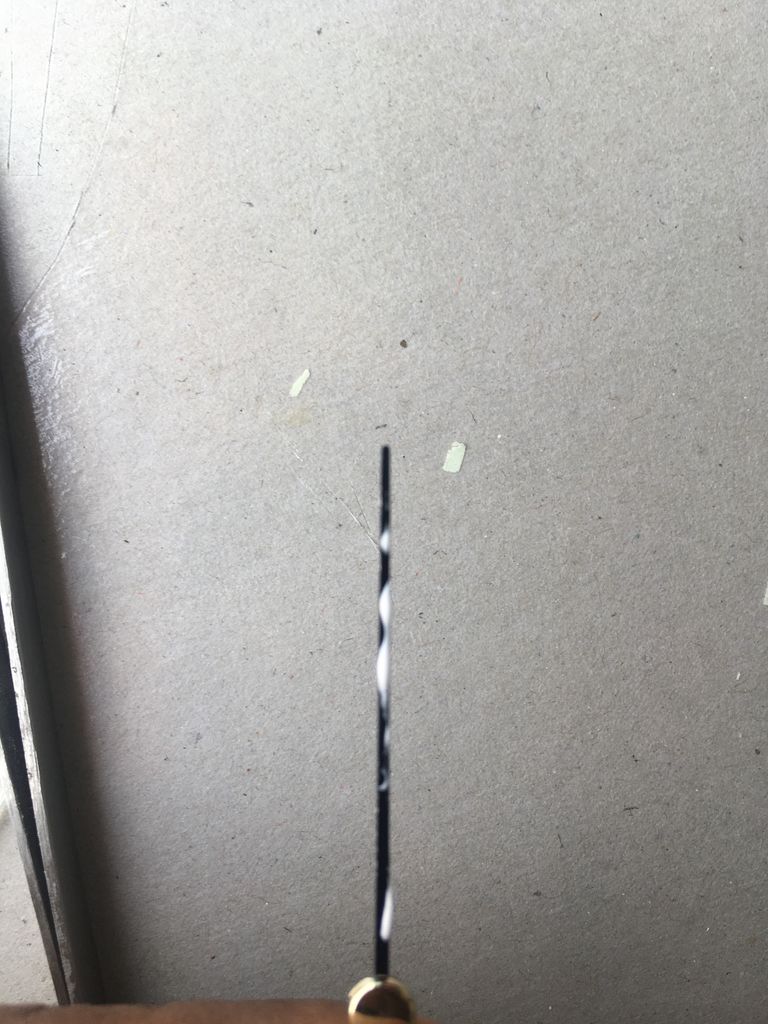

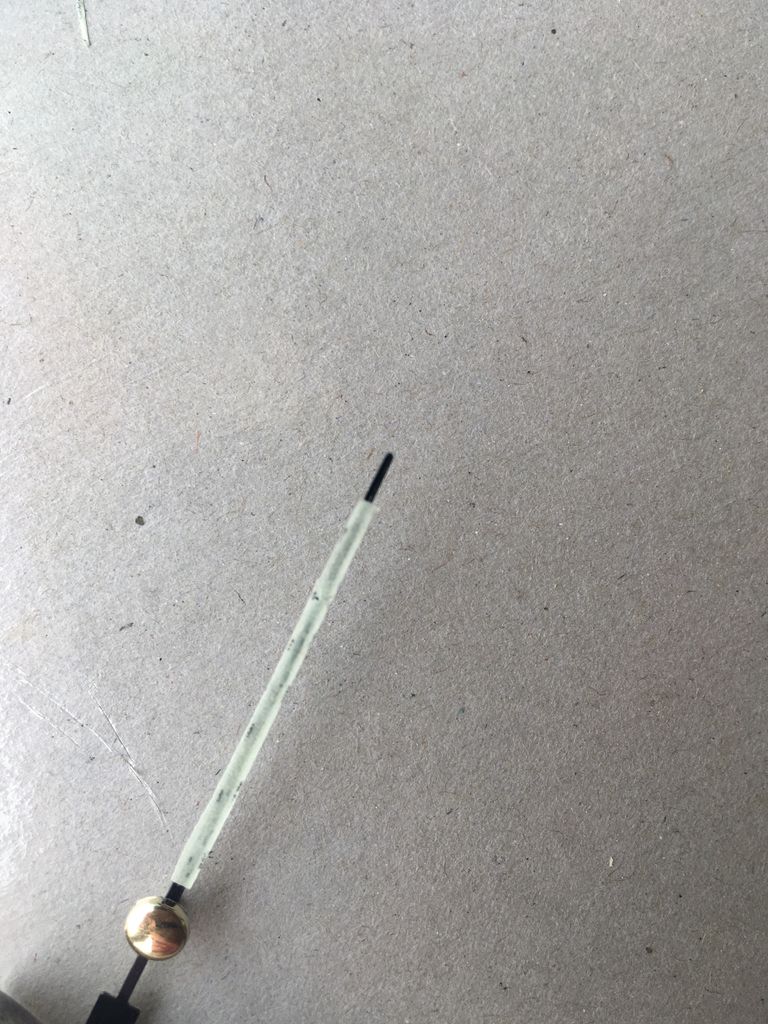

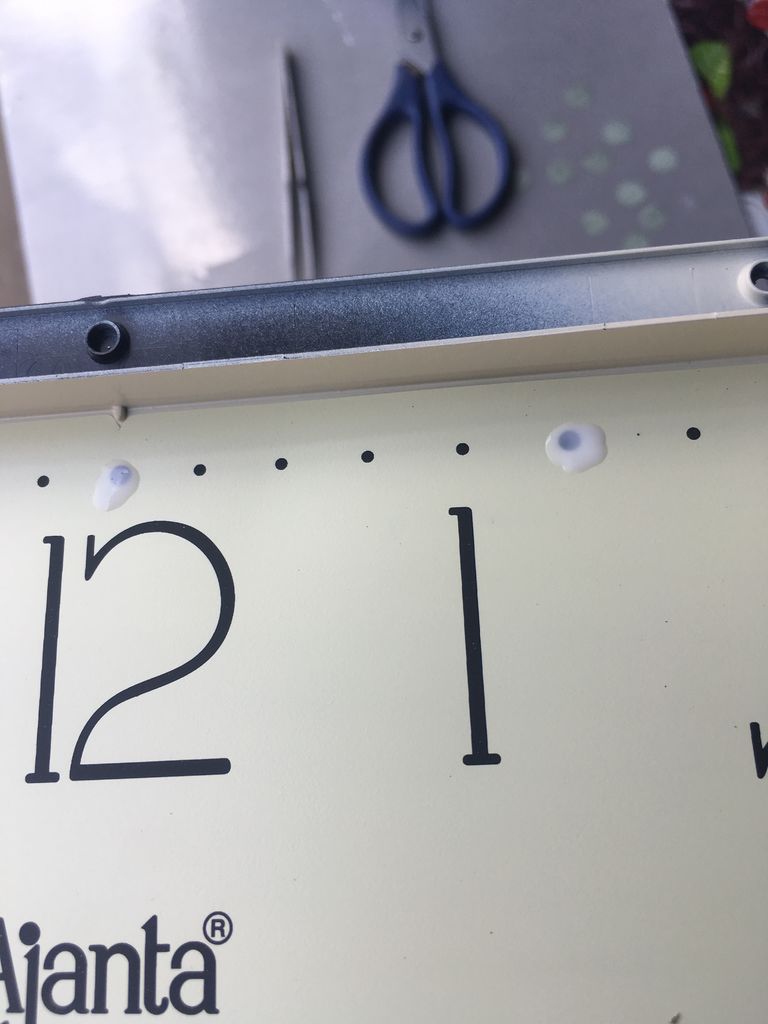

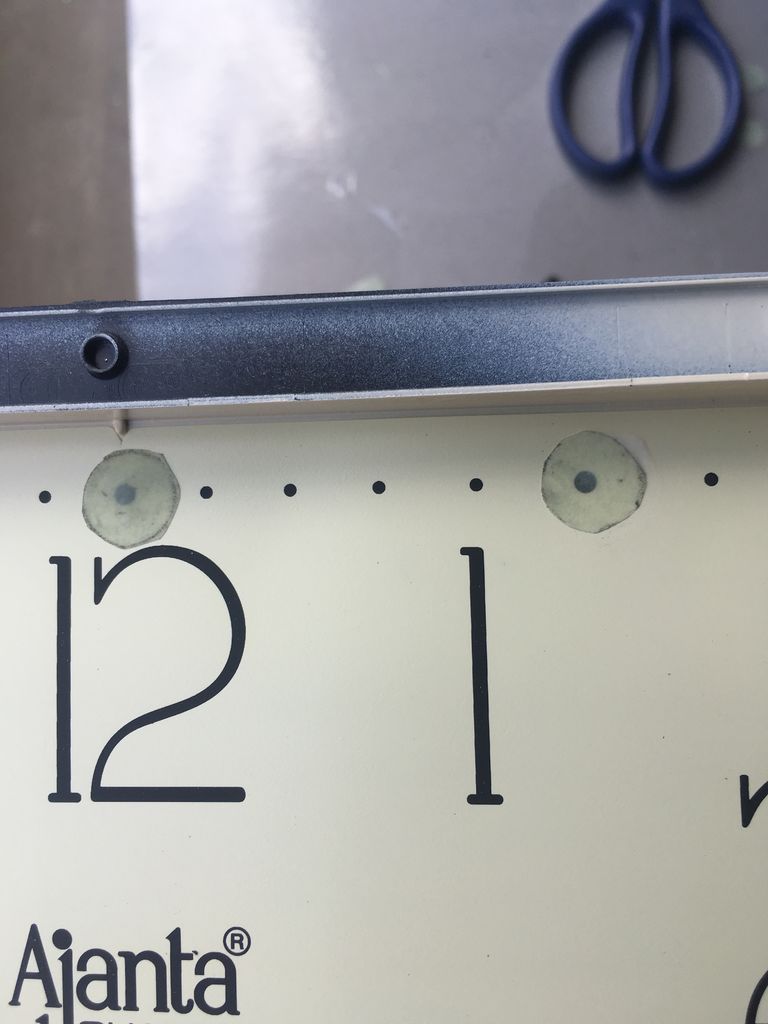

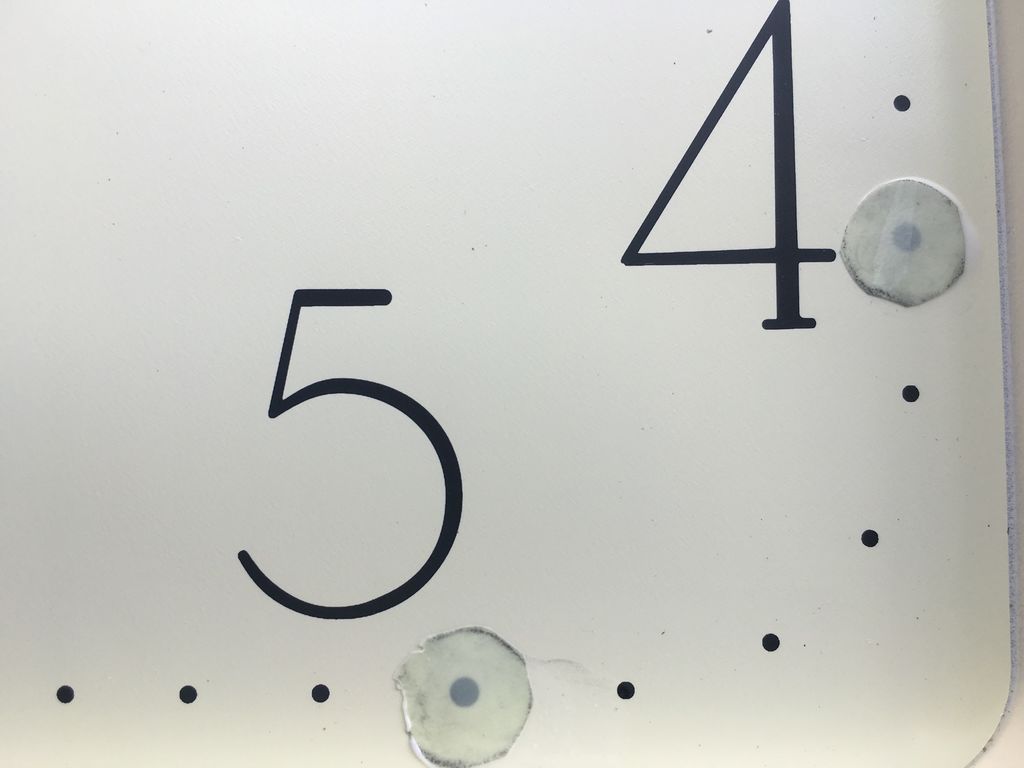

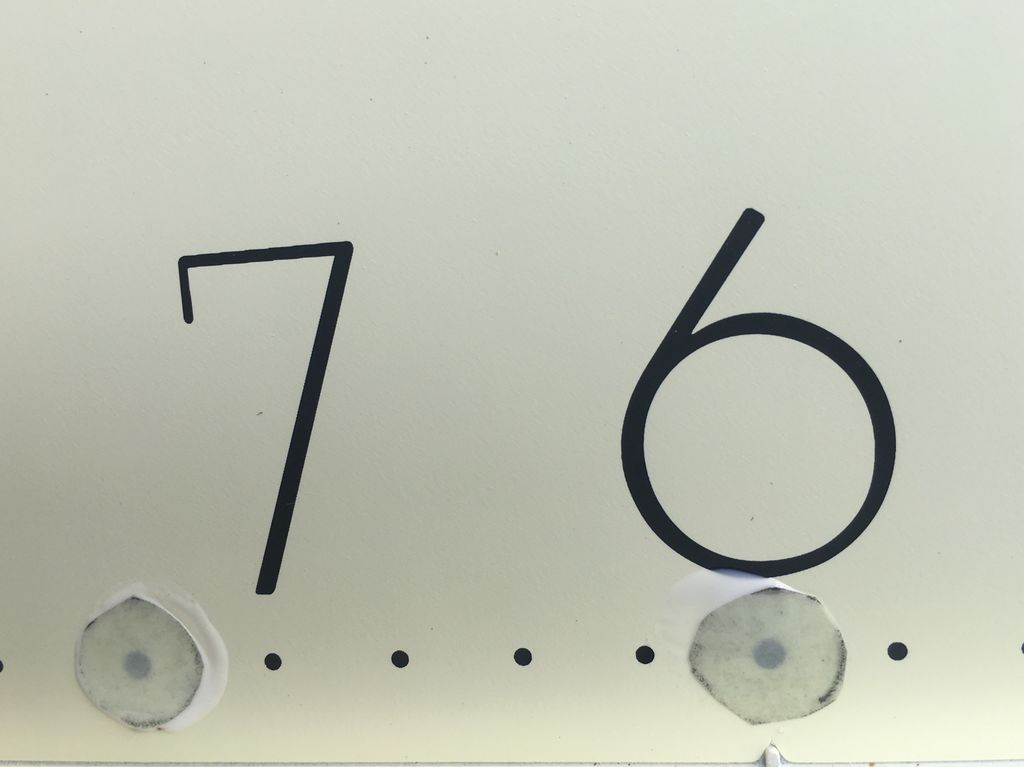

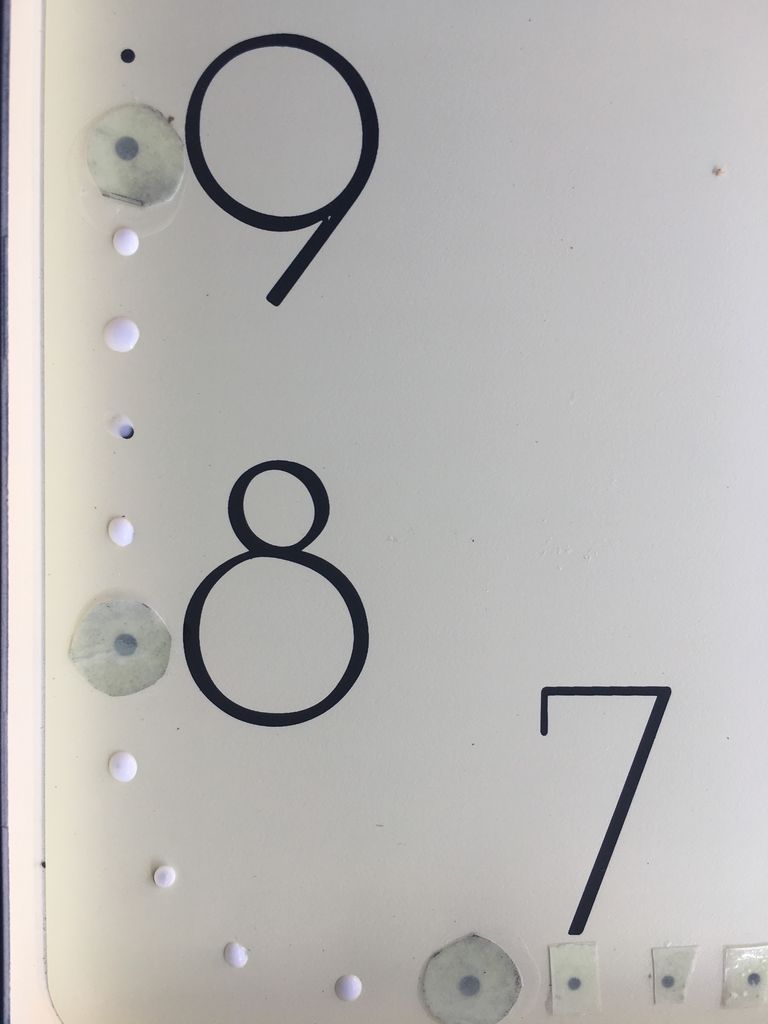

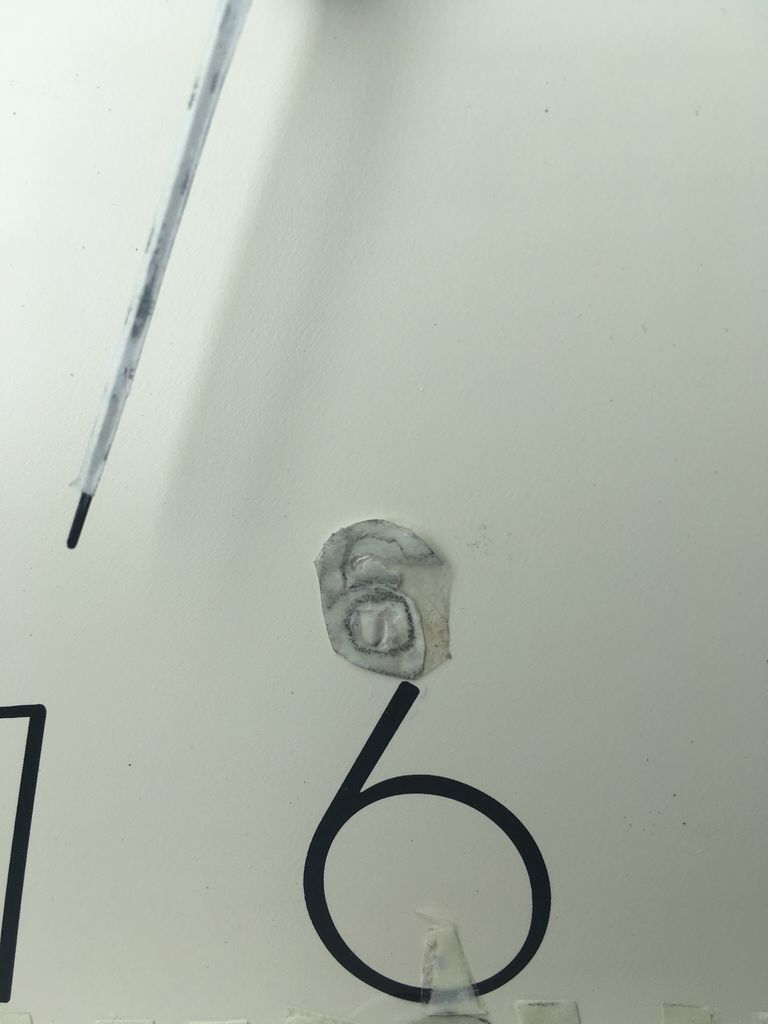

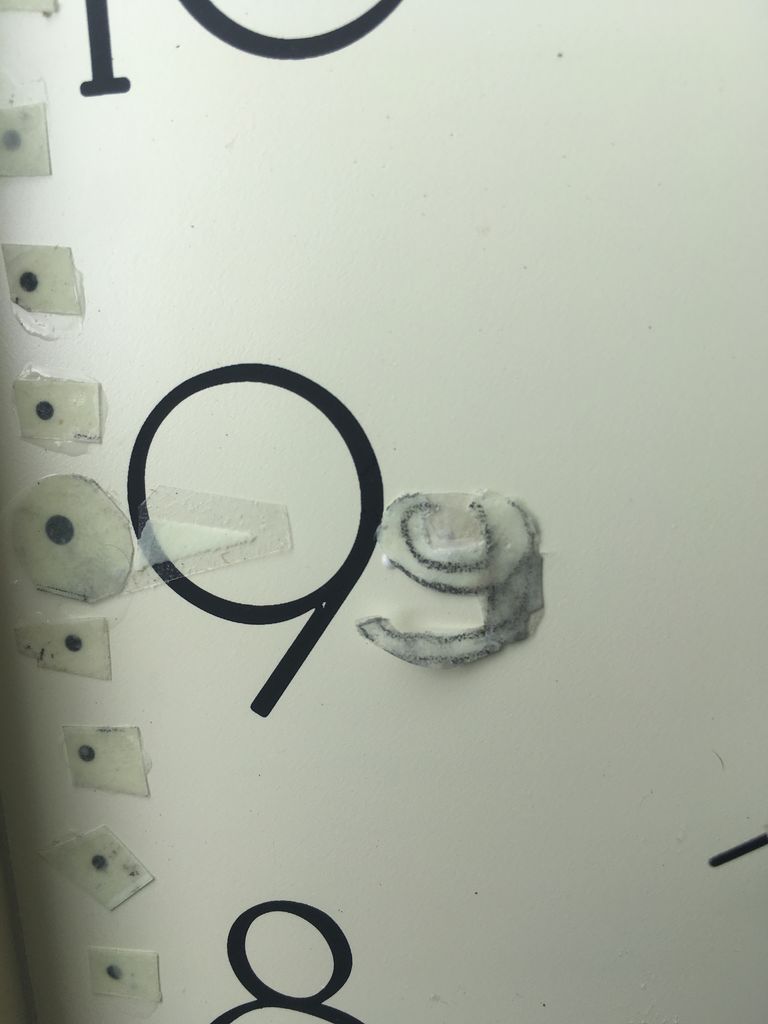

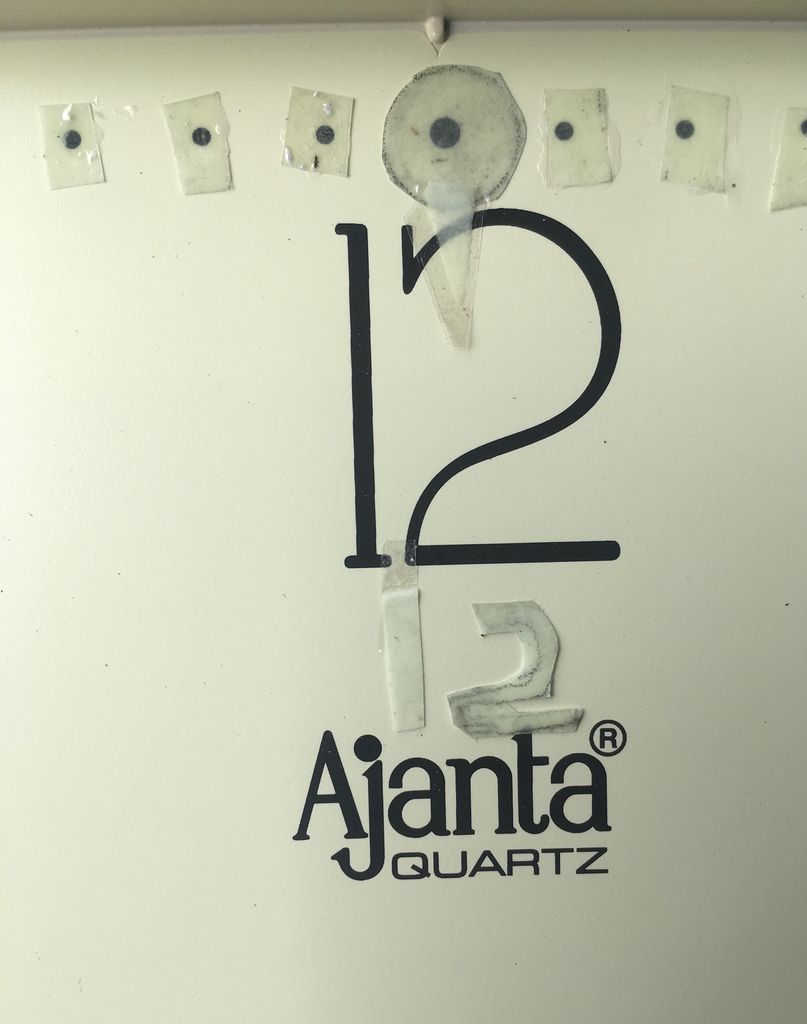

步骤6:GLUING一切都在时钟

》》首先取出时钟电池并拧下所有螺丝后面板。 》》根据您的时钟设计,将时钟上的所有组件从RADIUM条上拉下来并粘贴所有组件。

》》然后关闭时钟的后面板并拧紧它们。

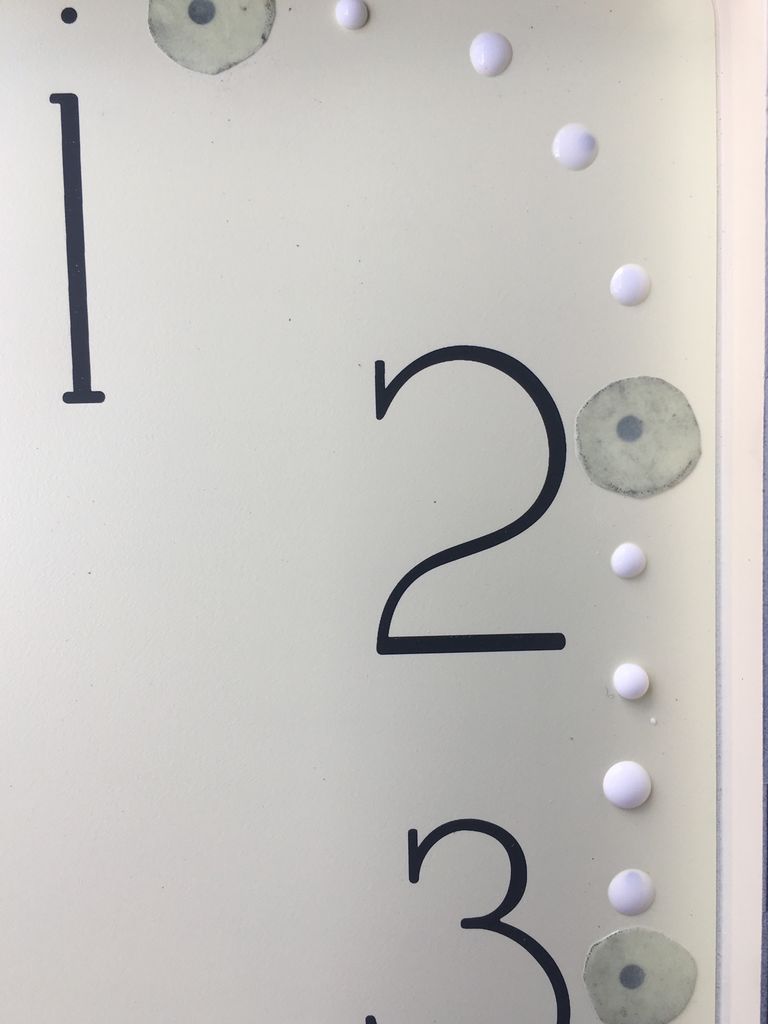

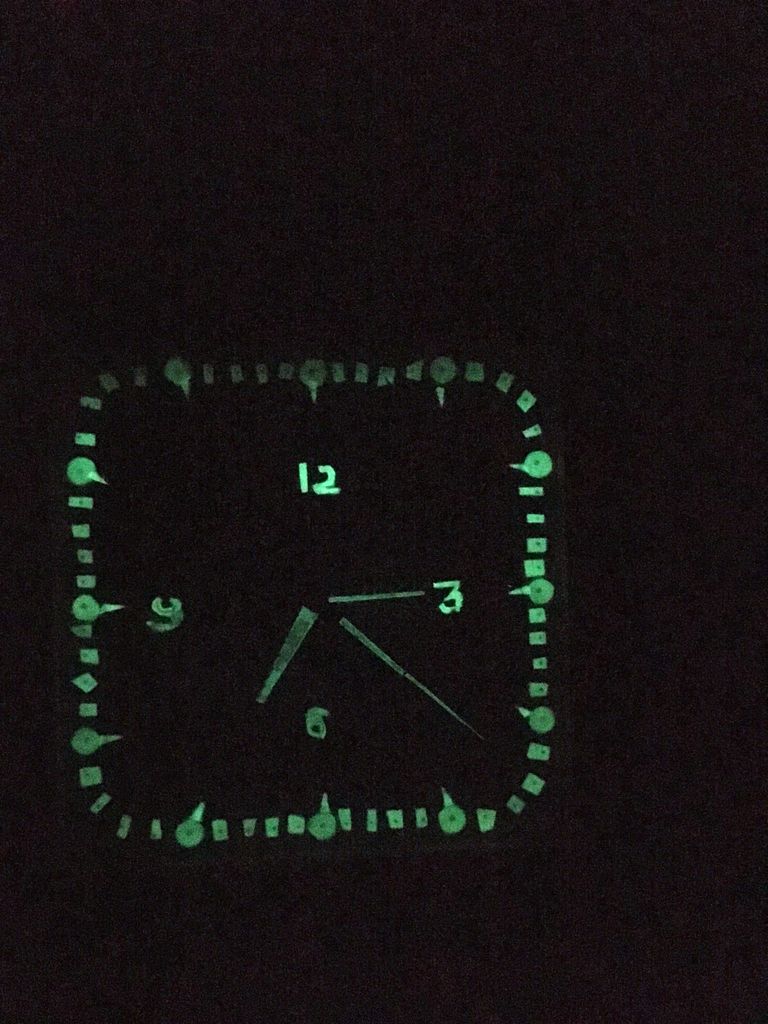

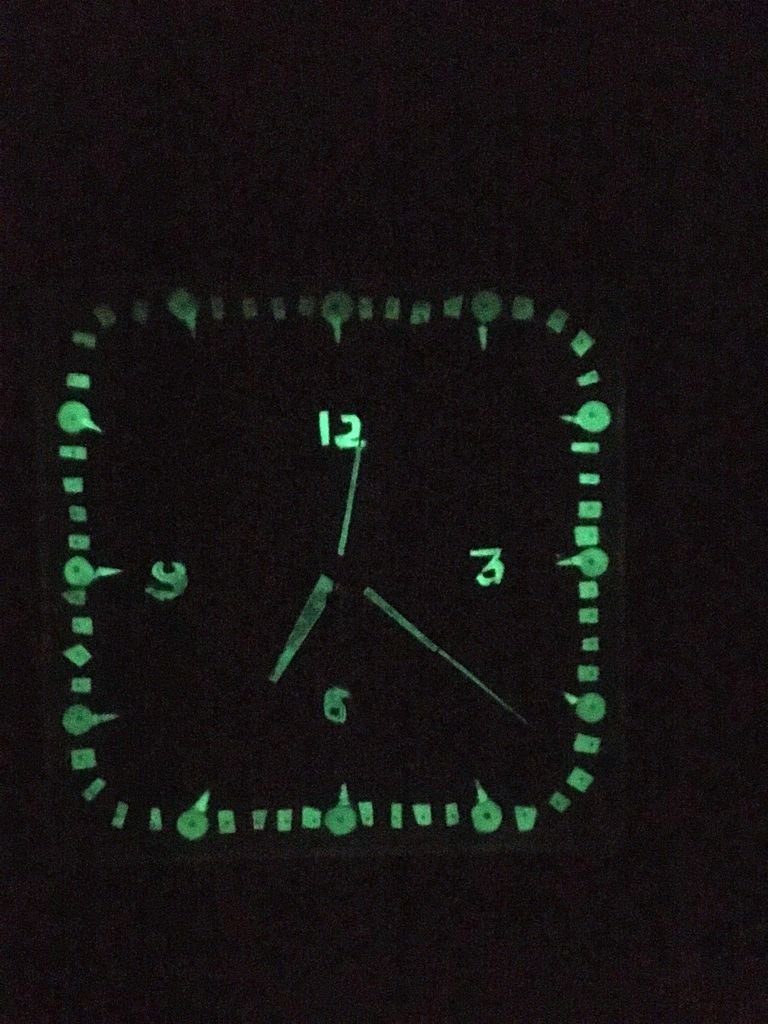

第7步:最终结果

因此我们终于得到了一个发光的时钟。

我把这个挂钟放在我家的起居室里。我看起来很酷,而且我非常喜欢。..。

第8步:使用镭的好处

》》否需要电池,电源或外部电源介质。..

》》 RADIUM是一种自发光元件,即使在黑暗中我们也可以从时钟获得自发光指示。

KIDS靠近我的家更像是这个时钟,并且经常在日落之后看到时间,并且让我跟这个时钟一样。

-

时钟

+关注

关注

10文章

1733浏览量

131479

发布评论请先 登录

相关推荐

ADS58C48的输出给FPGA的时钟怎样产生的,是只要有输入时钟,就有输出时钟吗?

请问ADS4129高速转换器的输入时钟引脚应该怎样设计?是应该外挂时钟吗?

时序约束一主时钟与生成时钟

高速ADC设计中采样时钟影响的考量

怎样将普通时钟转换为自发光时钟

怎样将普通时钟转换为自发光时钟

评论