1、对于一组总线(地址,数据,命令)驱动多个(多达4,5个)设备(FLASH,SDRAM,其他外设。..)的情况,在PCB布线时,采用那种方式?

布线拓扑对信号完整性的影响,主要反映在各个节点上信号到达时刻不一致,反射信号同样到达某节点的时刻不一致,所以造成信号质量恶化。一般来讲,星型拓扑结构,可以通过控制同样长的几个stub,使信号传输和反射时延一致,达到比较好的信号质量。

在使用拓扑之间,要考虑到信号拓扑节点情况、实际工作原理和布线难度。不同的buffer,对于信号的反射影响也不一致,所以星型拓扑并不能很好解决上述数据地址总线连接到flash和sdram的时延,进而无法确保信号的质量;另一方面,高速的信号一般在dsp和sdram之间通信,flash加载时的速率并不高,所以在高速仿真时只要确保实际高速信号有效工作的节点处的波形,而无需关注flash处波形;星型拓扑比较菊花链等拓扑来讲,布线难度较大,尤其大量数据地址信号都采用星型拓扑时。

附图是使用Hyperlynx仿真数据信号在DDR——DSP——FLASH拓扑连接,和DDR——FLASH——DSP连接时在150MHz时的仿真波形。

可以看到,第二种情形,DSP处信号质量更好,而FLASH处波形较差,而实际工作信号时DSP和DDR处的波形。

2、在EMC测试中发现时钟信号的谐波超标十分严重,只是在电源引脚上连接去耦电容。在PCB设计中需要注意哪些方面以抑止电磁辐射呢?

EMC的三要素为辐射源,传播途径和受害体。传播途径分为空间辐射传播和电缆传导。所以要抑制谐波,首先看看它传播的途径。电源去耦是解决传导方式传播,此外,必要的匹配和屏蔽也是需要的。

3、导带,即微带线的地平面的铺铜面积有规定吗?

对于微波电路设计,地平面的面积对传输线的参数有影响。具体算法比较复杂(请参阅安杰伦的EESOFT有关资料)。而一般PCB数字电路的传输线仿真计算而言,地平面面积对传输线参数没有影响,或者说忽略影响。

4、在PCB设计中,通常将地线又分为保护地和信号地;电源地又分为数字地和模拟地,为什么要对地线进行划分?

划分地的目的主要是出于EMC的考虑,担心数字部分电源和地上的噪声会对其他信号,特别是模拟信号通过传导途径有干扰。至于信号的和保护地的划分,是因为EMC中ESD静放电的考虑,类似于我们生活中避雷针接地的作用。无论怎样分,最终的大地只有一个。只是噪声泻放途径不同而已。

5、频率30M以上的PCB,布线时使用自动布线还是手动布线;布线的软件功能都一样吗?

是否高速信号是依据信号上升沿而不是绝对频率或速度。自动或手动布线要看软件布线功能的支持,有些布线手工可能会优于自动布线,但有些布线,例如查分布线,总线时延补偿布线,自动布线的效果和效率会远高于手工布线。一般 PCB基材主要由树脂和玻璃丝布混合构成,由于比例不同,介电常数和厚度都不同。一般树脂含量高的,介电常数越小,可以更薄。具体参数,可以向PCB生产厂家咨询。另外,随着新工艺出现,还有一些特殊材质的PCB板提供给诸如超厚背板或低损耗射频板需要。

6、、PCB单层板手工布线时,跳线要如何表示?

跳线是PCB设计中特别的器件,只有两个焊盘,距离可以定长的,也可以是可变长度的。手工布线时可根据需要添加。板上会有直连线表示,料单中也会出现。

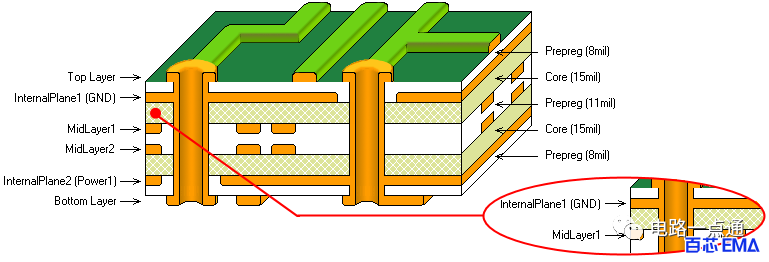

7、采用4层板设计的产品中,为什么有些是双面铺地的,有些不是?

铺地的作用有几个方面的考虑:1,屏蔽;2,散热;3,加固;4,PCB工艺加工需要。所以不管几层板铺地,首先要看它的主要原因。

这里我们主要讨论高速问题,所以主要说屏蔽作用。表面铺地对EMC有好处,但是铺铜要尽量完整,避免出现孤岛。一般如果表层器件布线较多,

很难保证铜箔完整,还会带来内层信号跨分割问题。所以建议表层器件或走线多的板子,不铺铜。

8、布不同频率的时钟线时有什么相应的对策?

对时钟线的布线,最好是进行信号完整性分析,制定相应的布线规则,并根据这些规则来进行布线。

9、PCB单层板手工布线时,是放在顶层还是底层?

如果是顶层放器件,底层布线。

10在布时钟时,有必要两边加地线屏蔽吗?

是否加屏蔽地线要根据板上的串扰/EMI情况来决定,而且如对屏蔽地线的处理不好,有可能反而会使情况更糟。

以上即是PCB设计中十个精华回答,希望在PCB设计中有帮助

责任编辑:ct

-

pcb

+关注

关注

4319文章

23084浏览量

397633 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

43036

发布评论请先 登录

相关推荐

详谈PCB有铅锡和无铅锡的区别

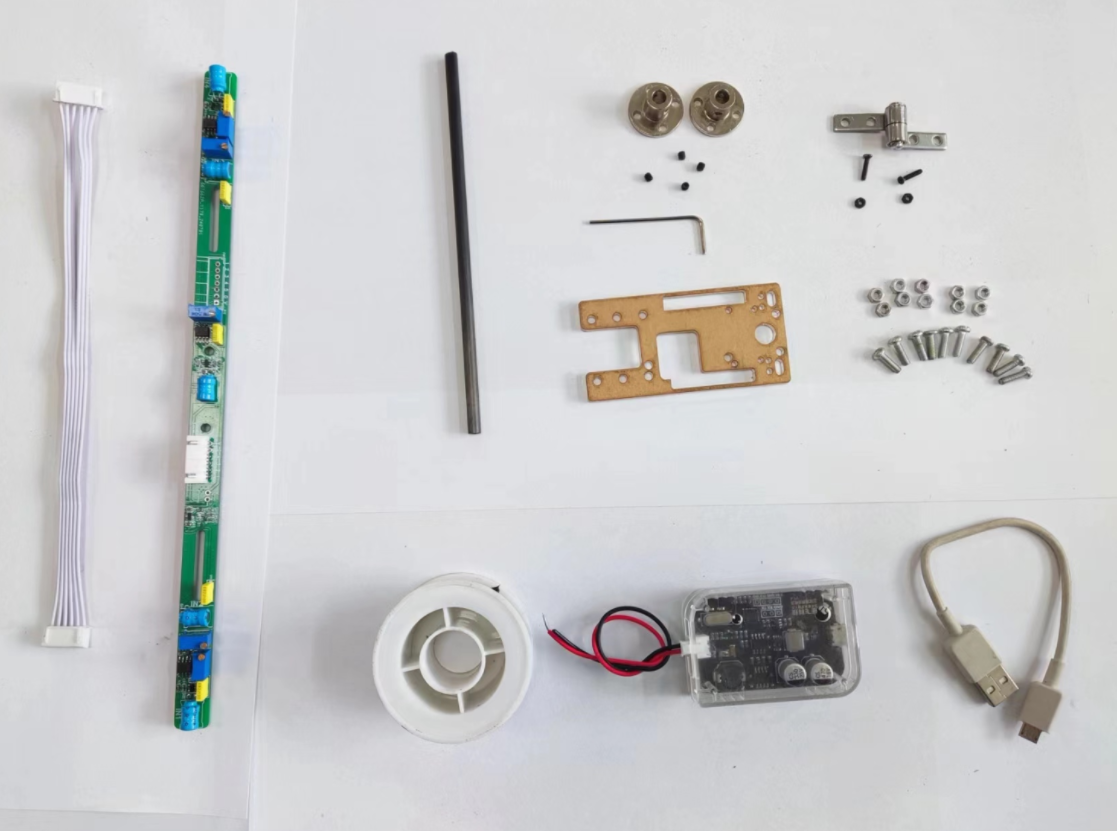

20.0-电磁杆的组装和实物介绍“这个是就是你想要的“-智能车电磁组 电磁循迹小车

PCB线路板制造中常见的错误有哪些,如何避免?

PCB设计中的常见问题有哪些?

什么是PCB扇孔,PCB设计中对PCB扇孔有哪些要求

做电路板的小伙伴,你有想问为什么PCB地与金属机壳用阻容连接吗?

你想轻松掌握PCB逆向研发原理图吗

PCB设计工作中常见的错误有哪些?

pcb的基板材料有哪些

pcb有哪些层面 都有什么作用

pcb问题有你想问的吗

pcb问题有你想问的吗

评论