虽然需要定制逻辑解决方案的系统设计人员越来越多地面临新的技术挑战,但他们在定制芯片产品方面拥有新的进步和选择。其中一个选择是基于单元的ASIC和平台ASIC解决方案之间的选择。

两者都是在芯片上实现复杂和高性能系统的可行途径。确定哪种解决方案最适合应用程序通常会混淆技术和业务考虑因素。技术考虑因素包括系统性能,逻辑和IP(知识产权)集成要求。业务问题通常涉及产品市场窗口,预计数量,设计成本,资源和风险分析。

一般情况下,如果应用程序要求在逻辑集成方面处于较高端(超过500万个ASIC门) ),就性能而言(超过300 MHz系统性能),由于大量预测,它绝对必须达到尽可能低的单位成本,它可能更适合基于单元的ASIC实现。另一方面,如果上市时间和风险缓解是驱动因素,逻辑集成要求大约为50万到500万门,并且进入门槛低于绝对最低单位成本的需求,那么平台ASIC实施通常是正确的选择。

此外,这些选项并不相互排斥。在其生产的初始阶段适用于平台ASIC的应用可以无缝地迁移到基于单元的ASIC,在两种解决方案之间具有类似的基础技术(硅和IP)。在这种情况下,创新者可以选择通过平台ASIC通过合理的前期投资来捕捉市场的新产品创意,并且在创新取得巨大成功的情况下仍然可以通过基于单元的ASIC降低成本。

什么是平台ASIC?

由于平台ASIC产品对于ASIC市场来说相当新,因此明确定义它们非常重要。可行的平台ASIC解决方案是一系列紧密定义的芯片,IP和设计方法,专注于缩短设计周期并最大限度地降低复杂系统的开发成本。

这是通过解决ASIC构造中对设计进度及其可变性影响最大的区域来完成的。了解这三个组件中的每个组件在实现平台ASIC目标中的作用非常重要。平台ASIC芯片通常由一组片提供,提供不同的门范围,存储器,I/O,PLL和其他知识产权,如高速串行器/解串器(SerDes)。平台ASIC“片”是预先制造的器件,用于实现芯片上的定制系统(SoC)。

可以通过几层金属为用户应用定制切片。平板ASIC切片的一个示例如图1所示。由于只有几层金属可以针对任何给定的设计进行定制,因此非重复工程(NRE)成本明显低于基于单元的ASIC开发,其中完整掩模需要设置。

图1—平台ASIC切片

与基于单元的ASIC相比,缩短平台ASIC设计周期的关键因素之一是设计方法。通过从“平台”切片开始,平台ASIC用户在设计周期中处于领先地位。

基于单元的ASIC设计流程中的许多必需步骤通常已由平台ASIC供应商在设计切片时完成。 I/O布局,存储器布局和布局规划,电源网格设计,扩散IP时钟和定时,信号完整性分析和封装只是片上预先完成的一些步骤。因此,当用户开始使用平台ASIC切片进行设计时,他们实际上完成的步骤要少得多,因此设计周期更短。平台ASIC设计方法的另一个关键组成部分涉及IP的使用。平台ASIC中通常使用四种不同类型的IP:

扩散IP —使用标准单元,定制和/或混合信号逻辑的固定扩散和金属化的知识产权及其位置是不可移动的。当不用于恢复路由区域和降低功率时,扩散的IP可以“铺设”。

硬IP —使用特定于体系结构的单元完成放置和路由的IP。由于尺寸和纵横比是固定的,因此在空间允许的情况下这些是可移动的。当需要控制性能/功率限制以保证性能时,使用硬IP。一个例子是嵌入高端处理器,如ARM926。

公司IP — IP作为网表提供,包括构建可交付成果(例如时序约束,综合脚本,仿真模型)。它还可能包含展示位置文件。当需要对部署进行一些控制并且存在一些灵活性时,或者更常见的情况是,由于合同义务而无法提供RTL代码,因此使用固定IP。

Soft IP &#151 ; IP简单地作为RTL提供,包括构建可交付成果(时序约束,综合脚本)。这只是实例化并与设计的其余部分合成。软RTL的主要优点是它独立于技术,使其易于携带。更高级别的SerDes链路层控制器,处理器外设和特定IP功能块都可以这种方式提供。

在图1所示的片中,8通道4.25 Gb/s SerDes就是一个例子。切片东侧的扩散IP。图中还显示了扩散的ARM926处理器和双倍数据速率(DDR2)接口。处理器还可以使用片上的“着陆区”区域实现为硬IP。裸片的着陆区(特定于LSI Logic RapidChip平台ASIC)区域专门设计用于使用基本晶体管结构和存储器块以高性能实现诸如处理器之类的功能。

在这种情况下,应用程序不需要处理器。模具的着陆区域没有浪费,可用于实现其他用户逻辑。这种着陆区的灵活性允许更好地适应切片到多个应用中作为扩散IP的有吸引力的替代方案,并且可能在不使用IP的情况下浪费芯片区域。

基于单元的ASIC或平台ASIC?

由于平台ASIC用户需要定义其架构以适应给定的目标平台(片),平台ASIC供应商提供这些片的系列,以适应不同的应用,具有各种门,存储器,I/O,SerDes和其他资源要求。在选择最适合应用的平台ASIC切片方面拥有广泛的选择,可确保最终用户获得更高的成本效率和更快的设计周期。

但是,如果应用程序在批量定价方面的业务要求非常严格,那么基于单元的ASIC可能是正确的解决方案。由于完全定义了基于单元的ASIC解决方案以仅适合其预期应用,因此它显然提供了最高的成本效率。

许多应用单元体积不足以证明开发基于单元的完整掩模集成本ASIC解决方案。通常,这些应用程序往往迫切需要快速进入市场,并且可能受到动态标准和接口的影响,这些标准和接口可能会相对较快地发生变化。

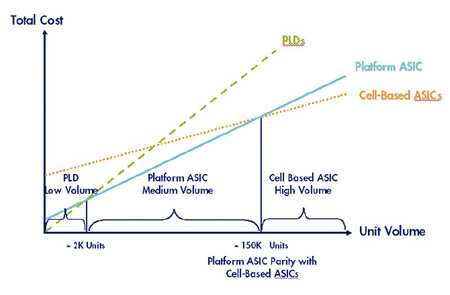

图2显示了典型的产品数量与成本分析的定义平板ASIC和基于单元的ASIC的“最佳点”,用于芯片上的复杂系统。从平台ASIC到基于单元的ASIC的交叉产品体积点完全取决于设计的复杂性,并且因应用而异。

图2—产品数量与成本分析

在选择平台ASIC和基于单元的ASIC之间的决策点,考虑所有相关因素非常重要。这些因素通常在不同程度上决定最终决策:

成本分析(NRE,单位成本,设计资源,设计工具)

每个解决方案实现的技术可行性最终产品目标特征

市场压力和竞争格局

风险分析

工程资源和项目团队核心竞争力

考虑从平台ASIC解决方案到基于单元的ASIC设备的可用迁移路径也非常重要。对于难以投射最终产品数量的应用,平台ASIC解决方案可以提供低成本的市场准入点,而不会排除通过基于单元的ASIC等效产品提供的较低成本定价的未来路径。

对于此迁移尽可能无缝地选择供应两种产品的供应商具有显着的优势。 ASIC平台和基于单元的产品供应商使用相同的基础工艺技术,两种解决方案之间采用相同的IP和类似方法,可以提供从平台ASIC到基于单元的ASIC更加透明的迁移路径。

作为LSI Logic的RapidChip产品营销总监,Yousef Khalilollahi负责全球RapidChip平台ASIC的“上市”战略。他的职责是致力于推动LSI Logic在平台ASIC市场的最新创新的引入和市场接受度。在担任现职之前,Yousef在FPGA业务部门工作了13年,在Actel Corporation担任过各种董事级营销和业务开发职位。

-

asic

+关注

关注

34文章

1200浏览量

120514

发布评论请先 登录

相关推荐

基于FPGA的单芯片实现ARM系统的应用解决方案

可行的平台ASIC解决方案用于实现芯片上的定制系统

可行的平台ASIC解决方案用于实现芯片上的定制系统

评论