之前在设计板卡时,只是听过相关的概念,但是未真正去研究关于SI相关的知识。将之前看过的一些资料整理如下:

(1)信号完整性分析

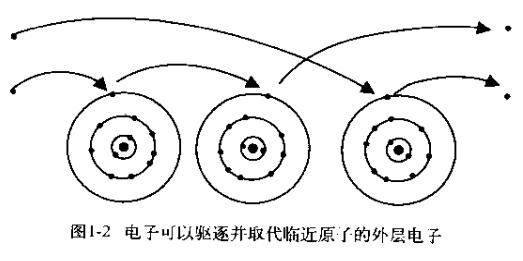

与SI有关的因素:反射,串扰,辐射。反射是由于传输路径上的阻抗不匹配导致;串扰是由于线间距导致;辐射则与高速器件本身以及PCB设计有关。

传输线判断

传输线的判断可以参考之前的博客

利用之前判断高速信号的公式,所以对于高速和低速的区分,需要考虑信号频率和传输路径长度。

判断步骤: 1)获得信号的有效频率Fknee 和走线长度 L;

2)利用Fknee 计算出信号的有效波长λknee,,即λknee = C /Fknee ;

3)判断L与1/6 x λknee之间的关系,若L > 1/6 x λknee,则信号为高速信号,反之为 低速信号;

其中λknee = C / Fknee;其中C是比光速略低的速度,Fknee = 0.5 / Tr(10% ~ 90%),还需注意的是,若是对于百兆频率的信号,若是没有现成的板子,可以对有效频率Fknee进行估算, Fknee 约为 7倍的Fclock(信号的周期)。

若L > 1/6 x λknee,则视为传输线,传输线必须考虑在传输过程中可能由于阻抗不匹配导致信号的反射问题。

反射公式

信号的反射ρ = (Z2 -Z1)/(Z2 +Z1);

其中Z2 为反射点之后的线路阻抗;Z1为反射之前的线路阻抗;

ρ 的可能存在值±1,0,当为0时全部吸收,当为±1时则发生反射。信号的反射由始端、传输路径、终端阻抗的不匹配导致。

降低反射方法

为了尽可能降低信号的反射,那么需要Z2 和Z1尽可能相近。有几种方法进行阻抗匹配:发送端串联匹配,接收端并联匹配,接收端分压匹配,接收端阻容并联匹配,接收端二极管并联匹配。

3)接收端分压匹配

4)接收端阻容并联匹配

优点:功耗较小;

缺点:存在接收端高低电平不匹配情况,由于电容的存在,会使信号的边沿变化变缓。

(2)信号回路

信号回路主要包括两个路径,一个是驱动路径,一个是回路路径,在发送端、传输路径、接收端测得的信号电平,实质上是该信号在驱动路径和返回路径上对应位置的电压值,这两条路径都非常重要。

要提供完整的回流路径,需要注意以下几点:

1.信号换层时,最好不要改变参考层,若信号的换层时从信号层1换到信号层2,参考层都是底层1,在这种情况下,返回路径无需换层,即信号的换层对其反回路径无影响。

2.信号换层时,最好不改变参考层的网络属性。也就是信号1开始的参考层是电源层1/地层1,经过换层之后,信号1的参考层是电源层2/地层2,其参考层的网络属性未变,都是GND或电源属性,可利用附近的GND或者电源过孔实现反回路径的通路。这里在高速情况下,过孔的容抗和感抗也是不能忽略的,这种情况下,尽量减小过孔,减小过孔本身产生的阻抗变化影响,减小对信号回流路径的影响。

3.信号换层时,最好在信号过孔附近增加一个与参考层同属性的过孔。

4.若换层前后,两层参考层的网路属性不同,要求两参考层相距较近,减小层间阻抗和返回路径上的压降。

5.当换层的信号较密集时,附近的地或者电源过孔之间应保持一定距离,换层信号很多时,需要多打几个对地或者对电源的过孔。

(3)串扰

解决串扰的办法是,高速信号,时钟信号,其他数据信号等,间距满足3W原则。

-

pcb

+关注

关注

4418文章

23979浏览量

426338 -

信号完整性

+关注

关注

68文章

1500浏览量

98270

发布评论请先 登录

速率不高的PCB是否需要考虑信号完整性

降低PCB设计风险的三点技巧(于博士信号完整性)

如何实现高性能的PCB设计工程

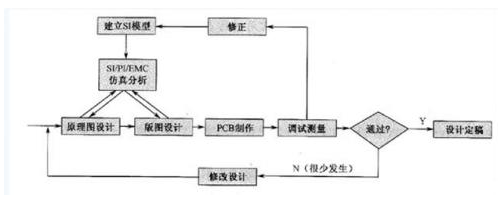

基于信号完整性的高速PCB设计流程解析

PCB设计信号完整性知识整理

PCB设计信号完整性知识整理

评论