如果一个数字系统的时钟频率达到或者超过50MHz,而且工作在这个频率之上的电路已经占到了整个电子系统一定的分量(比如说1/3),这就称为高速电路。

实际上信号的谐波频率比信号本身的重复频率高,是信号快速变化的上升沿与下降沿引发了信号传输的非预期结果。因此,通常约定如果走线传播延时大于20%驱动端的信号上升时间,则认为此类信号是高速信号并可能产生传输线效应。

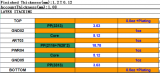

定义了传输线效应发生的前提条件,又如何判断传播延时是否大于20%驱动端的信号上升时间呢?信号上升时间的典型值一般可通过器件手册查出,而信号的传播时间在PCB设计中由实际布线长度和传播速度决定。例如,“FR4”板上信号传播速度大约为6in/ns(1in=2.54 cm),但如果过孔多,器件引脚多,速度将降低,高速逻辑器件的信号上升时间大约为0.2ns,则安全的走线长度将不会超过0.24in。

假设“Tr”为信号上升时问,“TD”为信号线传播延时,有如下经验法则:如果民≥5TD,信号落在安全区域;如果2TD≥Tr≥5TD,信号落在不确定区域;如果Tr≤2TD,信号落在问题区域。对于落在不确定区域及问题区域的信号,应该使用高速电路设计方法。

与低速情况下的数字设计相比,高速数字设计着重强调了数字电路之间用来传输信号的路径和互连,从发送信号芯片到接收信号芯片间的完整的电流路径,包括封装、走线、连接器、插座,以及许多其他的结构。高速数字电路的设计主要研究互连对信号传播的影响、信号间的相互作用,以及和外界的相互作用。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

pcb

+关注

关注

4417文章

23961浏览量

426061 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

44706

发布评论请先 登录

相关推荐

热点推荐

高速PCB工程师必看:用仿真三步法,让铺铜从“隐患”变“保障”

23年PCBA一站式行业经验PCBA加工厂家今天为大家讲讲在高速PCB设计中,如何通过仿真工具验证铺铜对信号完整性的影响。在高速PCB设计中,铺铜(Plane)并非简单的“接地”或“铺

高速PCB谐振威力,不容小觑

高速先生成员--姜杰

如果大家对平面谐振腔的印象还停留在方方正正的铜皮上,这篇文章可能会颠覆你的认知……

高速先生最近在做SMA测试板的仿真时,遇到一个奇怪的现象:同一块PCB,某些层面走线的

发表于 02-03 14:36

是德科技高频高速PCB板全流程测试解决方案

甚至更高的速率迈进,“高频高速”已成为PCB行业的必争之地。与之一同到来的是更严苛的材料Dk/Df控制,更复杂的阻抗匹配,以及更棘手的信号完整性挑战。在这个机遇与挑战并存的时刻,一块完美的高频高速

为什么高速信号链路 = 芯片 + PCB + 极细同轴线束三者匹配?

高速信号链路的性能,不取决于单一环节,而是“芯片 + PCB + 极细同轴线束”三者的整体匹配;芯片是信号的源,PCB 是高速通道,线束是关键桥梁;三者只有协同优化,才能实现

PCB分板切割就选Sycotec高速电主轴的硬核理由

在电子制造领域,PCB(印刷电路板)的分板切割环节至关重要,其精度与效率直接关乎产品质量与生产效益。要想切割效果好,选用好的工具及刀具是关键。在此背景下,德国Sycotec高速电主轴凭借数十年的技术

高速PCB铺铜到底怎么铺

在日常PCB设计中,我们经常会看到整版大面积铺铜,看起来既专业又美观,好像已经成了“默认操作”。但你真的了解这样做的后果吗?尤其是在电源类板子和高速信号板中,铺铜可不是越多越好,处理不好反而会影响电气性能甚至埋下安全隐患!

高频高速PCB板材材料技术解析与应用趋势

高频高速PCB板材材料技术解析与应用趋势 一、材料体系与核心性能指标 高频高速PCB板材的核心性能指标包括介电常数(Dk)、介质损耗因子(Df)、热导率、吸水率及尺寸稳定性。其中,

高速PCB布局/布线的原则

目录:一、布线的一般原则1、PCB板知识2、5-5原则3、20H原则4、3W/4W/10W原则(W:Width)5、重叠电源与地线层规则6、1/4波长规则7、芯片引脚布线二、信号走线下方添加公共接地

高速PCB板的电源布线设计

随着集成电路工艺和集成度的不断提高,集成电路的工作电压越来越低,速度越来越快。进入新的时代后,这对于PCB板的设计提出了更高的要求。本文正是基于这种背景下,对高速PCB设计中最重要的环节之一一电源

发表于 04-29 17:31

pcb的高速是怎样界定的

pcb的高速是怎样界定的

评论