8月15日,《自然》(Nature)杂质今天刊登了一项重大科学突破:牛津大学的化学家和IBM的团队一起,首次制造出了由18个碳原子组成的环形纯碳分子,而这在过去「几乎难以成功」,曾有无数团队尝试后放弃了。

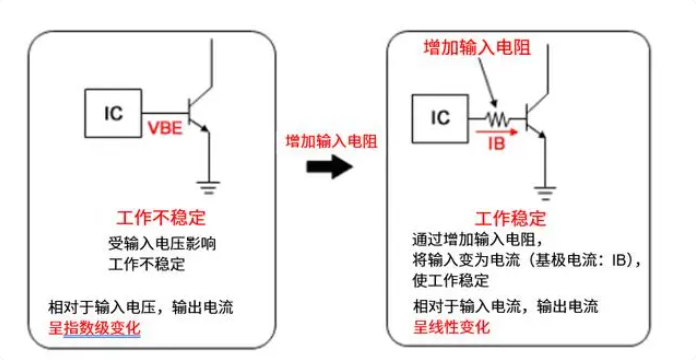

一开始,科学家先合成了由碳原子和氧原子组成的三角形分子,然后经电流作用产生碳18分子。这种分子被称为「环碳」(cyclocarbon),初步研究发现它表现为半导体,这可能对制造分子级的晶体管有很大帮助。

很多科学家表示,这绝对是「令人震惊的突破」。

碳是一种常见的非金属元素,由纯碳组成的碳单质可能外在表现截然不同,如坚硬透明的钻石和黑色、柔软的石墨,它们被称为「同素异形体」。据科普中国介绍,它们不同只要取决于其分子结构,金刚石中,每个碳原子都与周围的4个碳原子通过强烈的相互作用紧密结合,这样形成的三维结构非常稳定。

石墨则是层状结构,就一个片层而言,每1个碳原子会与其周围的3个碳原子通过强烈的相互作用紧密结合。因为层之间的距离较大,碳原子的相互作用较弱,因此石墨很软、有滑腻感。

理论上,碳分子也可以由相邻的两个原子组成,这样就形成一个环装结构。过去已有类似的研究,但是这样的结构相比金刚石和石墨都非常不稳定,很难有真实应用。此次的科学家团队则提出了一种新的方法,目前,在一定的前提条件下(基材表面保持冷却,大约零下450华氏度),新的碳分子可以保持稳定。

这可能对芯片行业有重大影响。例如目前主流的手机处理器是10纳米和7纳米制程,芯片厂商也在研究5纳米甚至2纳米制程的新产品,厂商在尝试将晶体管的尺寸越做越小,因为这样芯片就可以在同样尺寸下容纳更多晶体管,以获得更强的性能。

现在,比拇指还小的芯片上能容纳上亿个晶体管,你的手机比当年登月工程使用的计算机有更强的性能。

驱动科技行业快速发展的摩尔定律就是对这种趋势的总结,「集成电路上可容纳的晶体管数目,约每隔两年便会增加一倍。」

但是,当晶体管越做越小的同时,摩尔定律也开始受到挑战,这主要是因为受物理特性的影响,当芯片采用越来越小的制程时,会遇到各种各样的,如制造工艺、功耗,甚至包含漏电。

摩尔本人也曾预测过摩尔定律将在2020年失效,不过,他当时提出的几个问题都已经得到了解决。芯片行业目前遇到的瓶颈,已经触及材料的物理极限,要突破瓶颈很可能需要借助新材料的发展。如果能制造出分子级的晶体管,电子行业进入分子电子学时代,摩尔定律将再次显现威力。

-

芯片

+关注

关注

454文章

50676浏览量

423002 -

晶体管

+关注

关注

77文章

9678浏览量

138049 -

石墨

+关注

关注

2文章

111浏览量

18514

发布评论请先 登录

相关推荐

AI for Science:人工智能驱动科学创新》第4章-AI与生命科学读后感

达林顿晶体管概述和作用

PMOS晶体管的饱和状态

CMOS晶体管的尺寸规则

NMOS晶体管和PMOS晶体管的区别

上海科学家精准操控原子“人造”蓝宝石 为低功耗芯片研制开辟新路

BFR840L3RHESD晶体管是否可以用来放大nA级电流?

晶体管的分类与作用

基于量子干涉技术的单分子晶体管问世

晶体管放大时,各级电位状态是什么

什么是达林顿晶体管?达林顿晶体管的基本电路

科学家首次合成纯碳环形分子,可能是分子级晶体管的关键一步

科学家首次合成纯碳环形分子,可能是分子级晶体管的关键一步

评论