1定义

DDR:Double Date Rate 双倍速率同步动态随机存储器。

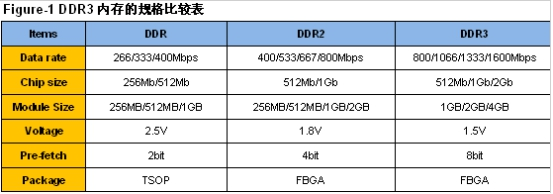

DDR、DDR2、DDR3常用规格:

02阻抗控制要求

单端走线控制 50欧姆,差分走线控制 100欧姆

03DDR布局要求

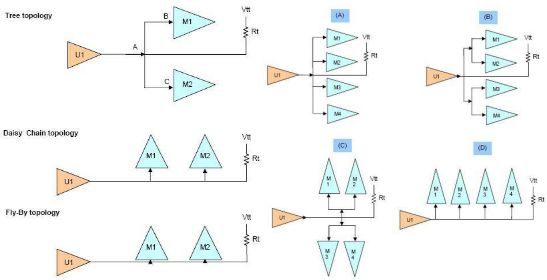

通常,根据器件的摆放方式不同而选择相应的拓扑结构。

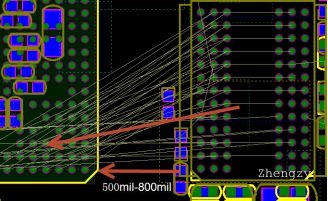

A、DDR*1片,一般采用点对点的布局方式,靠近主控,相对飞线 Bank 对称。间距可以按照是实际要求进行调整,推荐间距为 500-800mil。

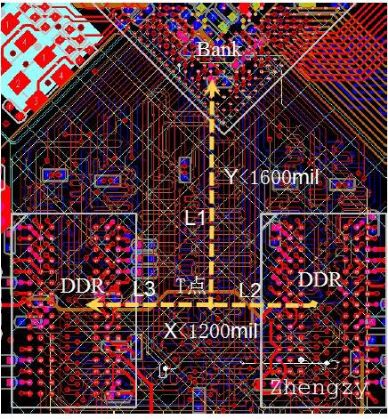

B、DDR*2片,布局相对主控飞线 Bank对称,常采用 T型拓扑结构, 推荐间距如下:

等长要求 L1+L2=L1+L3

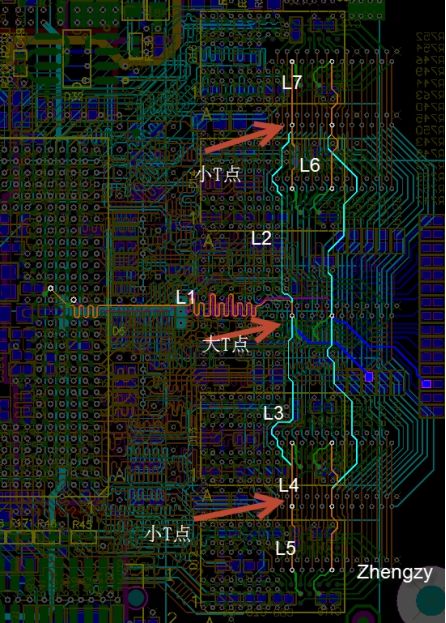

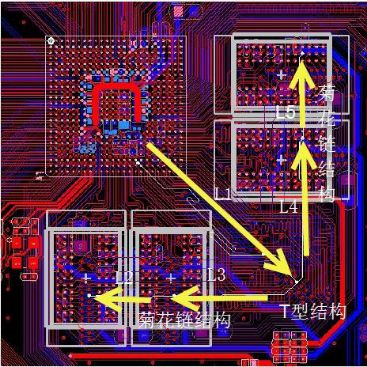

C、DDR*4 片,以下列出了常用的 4 片 DDR 布局拓扑结构。

针对于 DDR2,这些拓扑结构都是能适用的,只是有少许的差别。

若PCB布线空间允许,Address/Command、Control、CLK,应优先采用单纯的“T”型拓扑结构,并尽可能缩短分支线长度,如上面拓扑结构的B图所示。

等长要求 L1+L2+L6=L1+L2+L7=L1+L3+L4=L1+L3+L5

然而,菊花链式拓扑结构被证明在 SI 方面是具有优势的。对于 DDR3的设计, 特别是在 1600 Mbps时,则一般采用D所示菊花链拓扑结构进行设计。

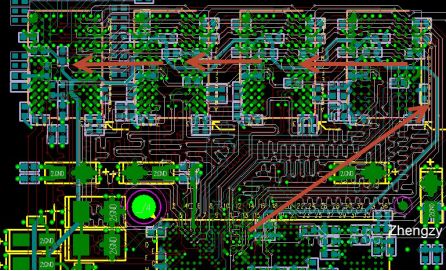

PCB 布线空间有限的,可以采用“T”型拓扑和菊莲拓扑混合的结构,如下图所示:

混合拓扑结构中“T”型拓扑的要求与两片DDR2/3 相同。

等长要求 L1+L3+L2=L1+L4+L5

04信号分组以及走线要求

(以下以4片DDR3设计进行说明)

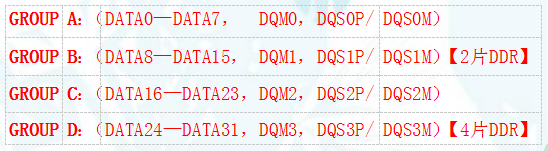

A、32条数据线(DATA0-DATA31)、4条DATA MASKS(DQM0-DQM3),4对DATA STROBES差分线(DQS0P/ DQS0M—DQS3P/DQS3M)

这36条线和4对差分线分为四组:

再将剩下的信号线分为三类:

Address/Command、Control与CLK归为一组,因为它们都是以CLK的下降沿由DDR控制器输出,DDR颗粒由CLK 的上升沿锁存Address/Command、Control 总线上的状态,所以需要严格控制CLK 与Address/Command、Control 之间的时序关系,确保DDR颗粒能够获得足够的、最佳的建立/保持时间。

B、误差控制,差分对对内误差尽量控制在5mil以内;数据线组内误差尽量控制在+-25mil以内,组间误差尽量控制在+-50mil以内。

Address/Command 、Control全部参照时钟进行等长,误差尽量控制在+-100mil 以内。

C、数据线之间间距要满足3W原则,控制线、地址线必要时可稍微放宽到2W~3W, 其他走线离时钟线20mil或至少3W以上的间距,以减小信号传输的串扰问题。

D、VERF电容需靠近管脚放置,VREF走线尽量短,且与任何数据线分开,保证其不受干扰(特别注意相邻上下层的串扰),推荐走线宽度>=15mil。

E、DDR设计区域,这个区域请保障完整的参考平面,如下方图片所示:

-

pcb

+关注

关注

4320文章

23113浏览量

398401 -

DDR

+关注

关注

11文章

712浏览量

65378

原文标题:看过来,DDR 模块的 PCB 设计要点都在这里!

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

分享一些常见的电路

DDR 模块的 PCB 设计要点有哪一些

DDR 模块的 PCB 设计要点有哪一些

评论