在PCB设计中,如何区分高速信号与低速信号?很多人有一个误区,一般认为频率高的信号就是高速信号,对于GHz这样的信号来说无可厚非,但却不能一概而论。

凡是大于50MHz的信号,就是高速信号;

信号是否高速和频率没有直接关系,而是信号上升/下降沿小于50ps时就认为是高速信号;

当信号所在的传输路径长度大于1/6λ,信号被认为是高速信号;

当信号沿着传输路径传输,发生了严重的趋肤效应和电离损耗时,被认为是高速信号。

所以说高速信号并不是以频率高低来界定的,那么应该怎样区分高低速信号呢?

在高速信号的设计中,一般考虑的并不是信号的周期频率F,一般是有效频率F1,T代表信号的时钟周期,T1代表信号的10%-90%的上升时间,则有:

周期频率定义:F=1/T

有效频率定义:F1=0.5/T1

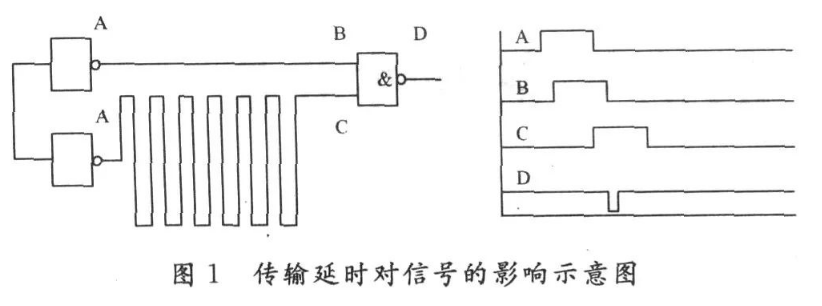

低速信号中,各个点的电平相差不大,但高速信号中,需要用分布式的思维来考虑问题,在传输路径中,每个点的路径相差很大,所以高低速信号的划分还与信号的传输路径有关。

信号的传输长度小于信号波长的1/6时,可认为是低速信号,反之高速。λ是信号波长,c是信号在PCB上传输速度,F是信号的有效频率。

λ=c/F

在C为常数的情况下,λ与F成反比,即频率F越高,波长越短,可以划分的高低速信号线的分水的线长越短。

总结:高速信号与低速信号的区分方法

1、获得有效频率F1及走线长度L

2、利用有效频率F1计算信号的波长λ

3、判断L与1/6*λ的大小关系,L大为高速信号,反之为低速。

补充:一般有效频率可以由专业仪器测量得到,也可以估算,可假设上升沿为信号周期的7%,假如信号频率是10MHz,可以假设有效频率是70MHz。

-

pcb

+关注

关注

4316文章

22988浏览量

396117 -

高速信号

+关注

关注

1文章

220浏览量

17676

原文标题:干货| PCB设计中高速信号与低速信号的区分

文章出处:【微信号:eqpcb_cp,微信公众号:快点儿PCB学院】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

高速pcb与普通pcb的区别是什么

高速PCB设计,信号完整性问题你一定要清楚!

stm32的高低速外设是怎么区分的?

分析高速数字PCB设计信号完整性解决方法

高速PCB信号走线的九大规则

混合信号PCB设计问题

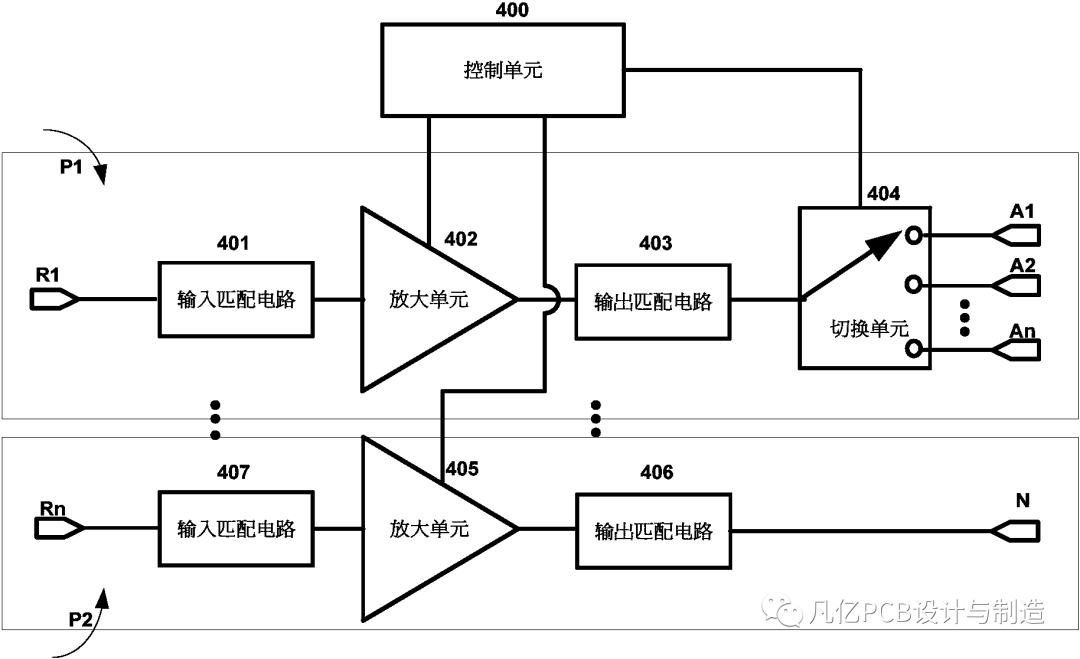

详解PCB设计中高速背板设计过程

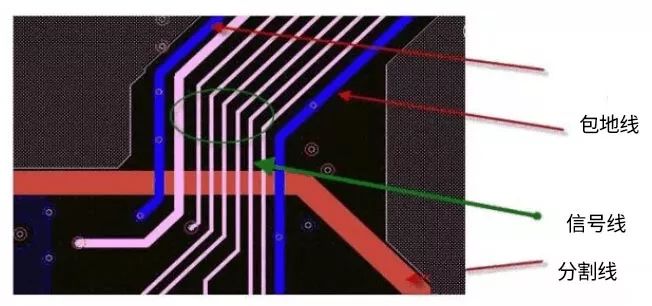

在高速电路设计中,如何应对PCB设计中信号线的跨分割

PCB设计中高速信号与低速信号如何区分

PCB设计中高速信号与低速信号如何区分

评论