很多硬件工程师都有过因为一个小小的不注意,不得不重新打板的经历,对有些不以为然的工程师甚至成了家常便饭,殊不知这每一次的打板导致的工期延误对于企业是很大的浪费,尤其是对于争分夺秒抢占市场的产品来讲任何小小的疏忽导致的工期延误带来的损失都有可能是致命的。

我在前面的文章中说过,硬件工程师设计PCB,即便是一个崭新的设计,到最终定型不能超过3版,最好2版以内搞定。而做到这一点就必须养成良好的设计习惯,PCB设计是牵扯到很多个环节的链条,越早的环节越是重要,为避免最终的错误,从一开始就要小心翼翼,不能埋下任何雷。今天苏老师来讲讲电路原理图设计中要注意的一些要点。

首先要说明的是,原理图是连接产品的概念性设计(方案框图)和最终的以PCBA形式的物理呈现之间的桥梁,因此它一定要准确、完整。原理图的基本构成单元是表征一个个电子元器件的“符号(Symbol)”,因此要求原理图的“符号”一定要准确、完整,而这些符号之间的连线(元器件各管脚之间的电气连接)要正确无误。

元器件符号的准确、完整

熟练掌握原理图符号的编辑(Symbol Editor)是非常重要的,即便在设计中你没有必要自己亲自创建原理图符号,但你仍然需要查看或检查这些符号的特性。尤其是你从一些网站上(SamacSys、Ultralibrarian、SnapEDA等)下载的符号,这些网站提供的是适用于各种PCB设计工具的符号,因此最好要根据自己的电路设计对这些符号中的管脚进行位置的重新排列,以及一些管脚属性的定义。

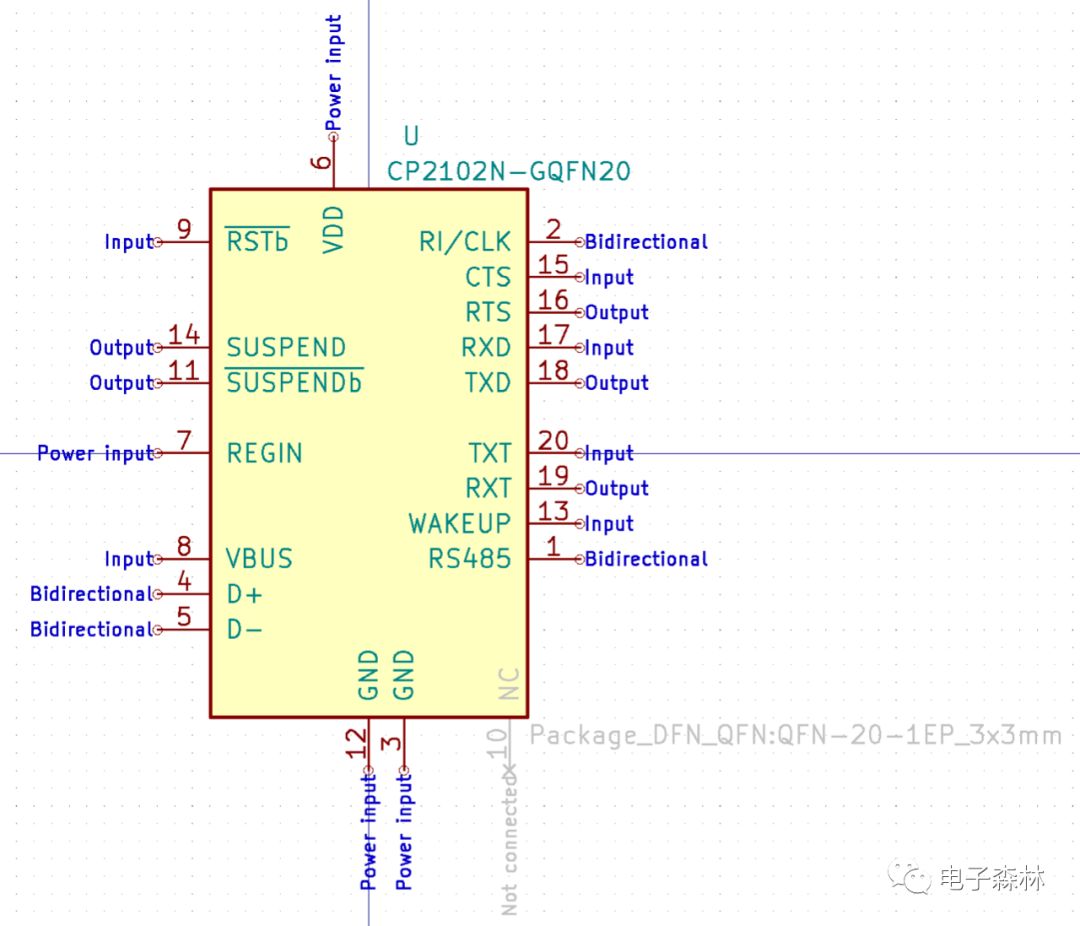

一个元器件的所有的管脚都必须在符号上“可见(Visiable)”,也就是显示出来,如果这个器件有20个管脚,那就必须有20个管脚出现在符号上,永远不要用“不可见(Invisible)”管脚,比如“电源”和“地”管脚,另外“No Connect”(简称NC - 无连接)的管脚也要显示出来。

有两种类型的“NC”管脚,第一种类型是在任何的设计中都不会被连接,它可能本身就是没有任何内部连接的,或者说只是供生产厂商测试用的。比如上面图中的CP2102N-GQFN20的第10个管脚就是永远不用连接的管脚。有的原理图工具允许给这种管脚设定一个“NC”类型的属性,这些管脚将被永久地用一个小“x”来标记。你也可以给它们一个独特的管脚名字NC1、NC2等等,就像在原理图上显示的那样。虽然原理图允许管脚重名,但我建议最好给每个不同的管脚不同的名字。

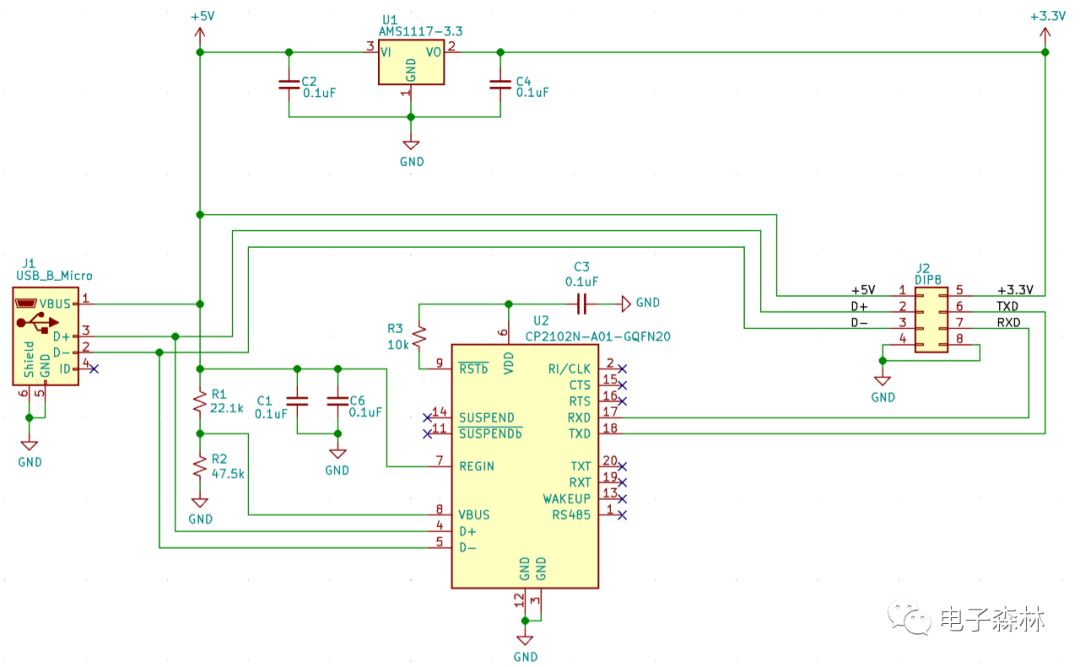

第二种类型的“NC”是有一些管脚是有意义的,但在某些设计中用不着,例如下图用CP2102设计的USB - UART桥接电路中,有不少管脚内部是有连接,但在这个设计中它们是不用连接上的。很多原理图工具允许将没有连接的管脚上放置一个叫“NC”的原理图符号,一般为“X”的形状,作为原理图的一部分。如果原理图工具中没有这么个“NC”符号,系统做ERC(电气规则检查)的时候就会报“错误”(Error)或者“警告”(Warning),在知道事情的原委的前提下你可以忽略这些信息,但一定要确保你知道这些信息的来源.

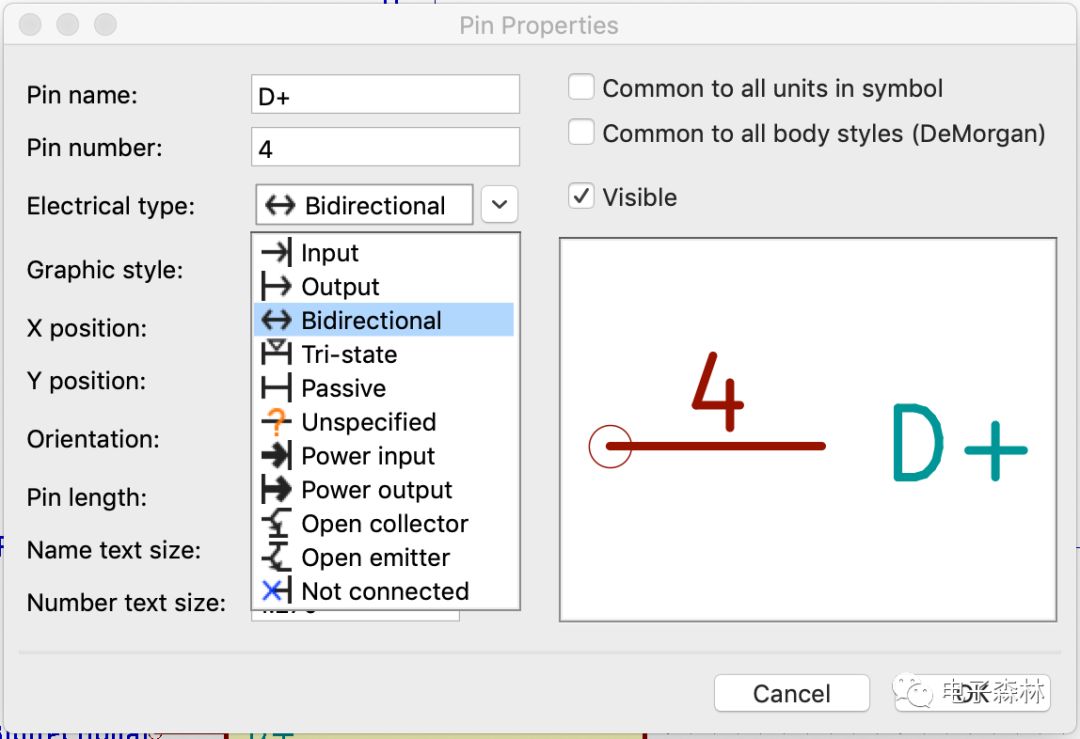

在构建原理图符号的时候非常重要的一步就是为每个管脚赋予正确的“电气类型”,这些管脚的类型会用在ERC中,这些电气类型的添加或编辑有专门的菜单来执行,如下图(KiCad工具为例),电气类型选项中可以看出针对每一个管脚的一些典型的电气特性。

有的时候还是需要一些小技巧才能选到准确的类型的 -可以选择最接近的。有时候找不到合适的类型,你可以选择“Passive”(无源),这个属性会被轻松通过ERC。不是所有的工具都有“NC”类型,如果没有的话,你可以选择一种类型,使得它连接了任何一种管脚ERC都会报错。

连接器、FPGA、微控制器等这些器件的符号经常需要修改某些管脚的电气类型,因为这些管脚在不同的设计中其电气类型是不同的,要根据分配给这些管脚的信号的属性来重新修改这些管脚的电气类型。

在创建完所有的原理图符号后,找一个安静、无人打扰的地方,打开符号编辑器以及这些元器件的数据手册,再仔细检查每一个器件的每一个管脚:管脚编号、管脚名字、电气类型等,确保每一个管脚都在符号上而且属性是对的。我个人的习惯是在画完原理图以后再检查一遍原图中的每个符号,从创建原理图符号,到绘制原理图再做最终的检查中间隔一段时间会比较容易检查出一些刚创建时无法看出来的问题。

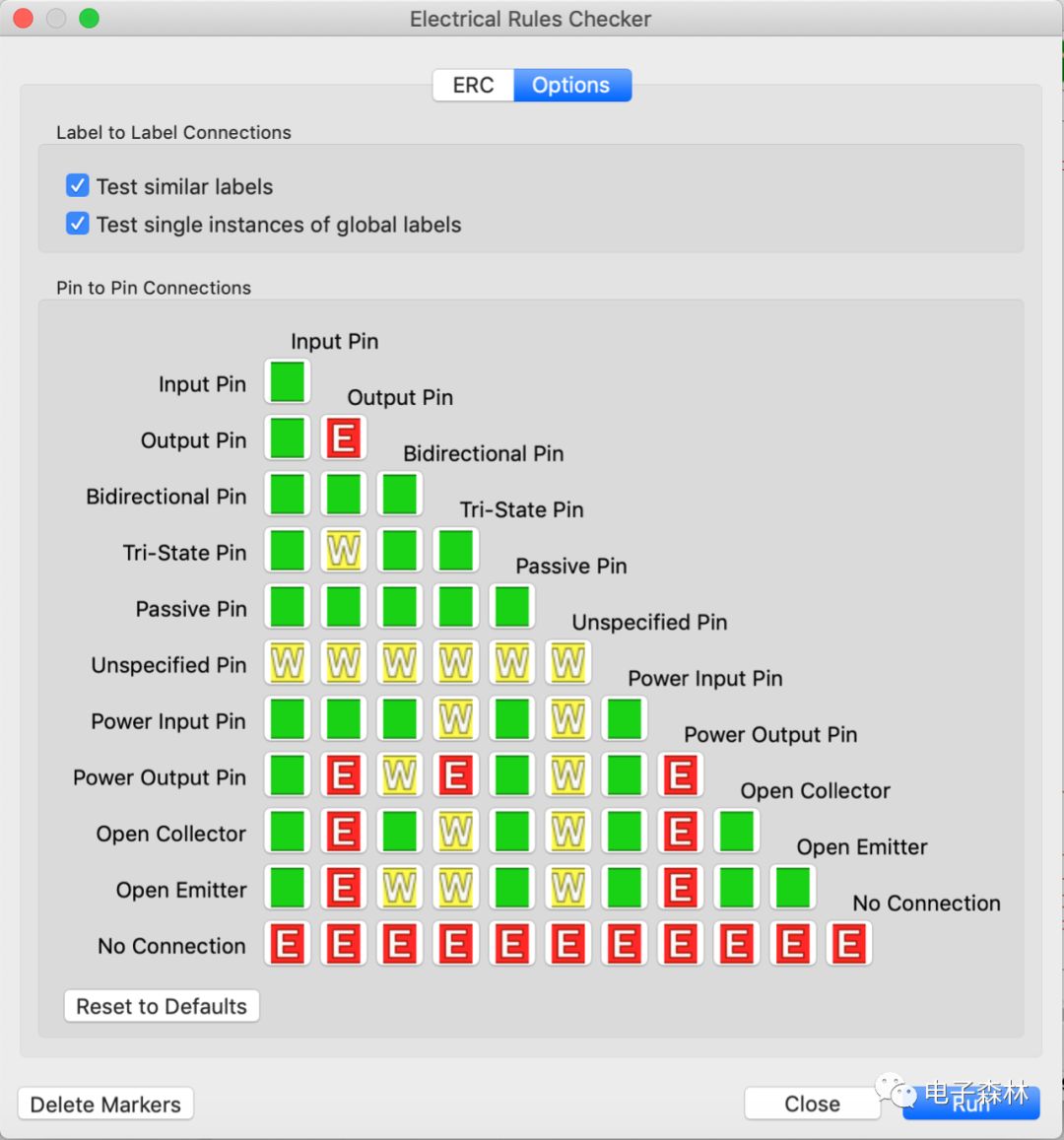

善用ERC(电气规则检查)ERC是根据一系列设定的规则进行的电气连接方面的检查,如果有不正确的连接就会给出“错误”或“警告”的提示信息。一般来讲,规则都是在寻找悬空的管脚,或者电气类型不兼容的管脚之间产生了连接。一般来讲,这些规则被一个“连接矩阵”来设定,如下面的例子(来源于KiCad工具):

在矩阵中,每一种可以指定给管脚的电气类型都有一行和一列,这些由行、列交叉的管脚的每一种组合就被定义了一种规则,在本图中,矩阵中绿色的意味着两种类型的管脚是可以进行连接的,一个“W”在ERC报告中会产生一个“报警”信息,一个“E”在ERC报告中会产生一个“错误”信息。工具一般都会有一个缺省的矩阵规则,这种规则是常用的,当然在具体的电路设计中你可以根据需要改变这些规则。 虽然ERC是有局限性的,也一定要在设计原理图的时候运行ERC,根据你电路的设计设计可以调整你电路ERC的规则矩阵,并根据产生的报告修改电路图中存在的错误和不规范的地方,直到所有的错误、警告信息全部消失再执行下一步。

通过网表(netlist)检查

即便你的设计通过了ERC,没有了错误,也没有了警告提示,但不意味着你的设计一定就安全了,你可能标记网络名字的时候将两个名字做了交换,有可能本该连接的管脚并没有真正连接上,而这些通过ERC可能无法检查出来的,生成的Netlist可能帮你大忙。 我一般会手工检查生成的网表 - 对比原理图中的每一根连线,查找netlist中的每一个连接信息,检查完一个连接在原理图上划掉,并在netlist文件中删除掉,直到原理图中的每一个连接、netlist中的每一行信息都彼此做了一一对应。很多人会觉得这没有必要,但我确实发现过通过其它检查工具未查出来的问题。对我来讲,发现一个问题就值得所有的努力。 机器 - PCB设计工具,毕竟是按照人设定的规则进行检查的一种方式,它不可能尽善尽美,但学会使用这些工具会对你的设计大有裨益。当然最重要的还是要养成好的设计习惯 - 在创建原理图符号、绘制原理图的每一步都要尽可能做到严谨、细致、一丝不苟,确保原理图、原理图的每一个符号都是准确的、完整的,原理图的连线都是准确的、完整的并且清晰的。除此之外,考虑到原理图的易读性(多数情况下原理图是给别人看的,而别人更容易发现你看不到的问题),原理图的设计风格也要做到清晰、规范、符合人的阅读习惯。 前期点点滴滴的努力,都是为了后期项目进展的顺畅,记住一点,前期花的时间越多,整体的效率会越高。

-

pcb

+关注

关注

4318文章

23070浏览量

397147 -

电路原理图

+关注

关注

40文章

347浏览量

38309

原文标题:如何设计电路原理图才能降低PCB的出错风险

文章出处:【微信号:xiaojiaoyafpga,微信公众号:电子森林】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

24M开发出新隔离膜可降低电动汽车电池火灾风险

PCB设计中怎么降低EMC

欧姆龙工厂火灾风险降低解决方案

【《软件开发珠玑》阅读体验】居安思危之风险

4pinM8接口生产时易出错的几个环节

降低PCB的出错风险的几个技巧

降低PCB的出错风险的几个技巧

评论