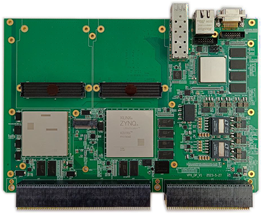

米尔XCZU3EG系列开发板MYD-CZU3EG以超高性能著称,下面用这款板子做一个演示。

开发环境:vivado 2017.4,开发板型号:米尔MYD-CZU3EG, 主芯片XCZU3EG-1SFVC784。这个系列板子还有4EV,5EV等版本,手里的3EG版本不支持SFP,因此板上相应接口(白色部分)是空贴的。

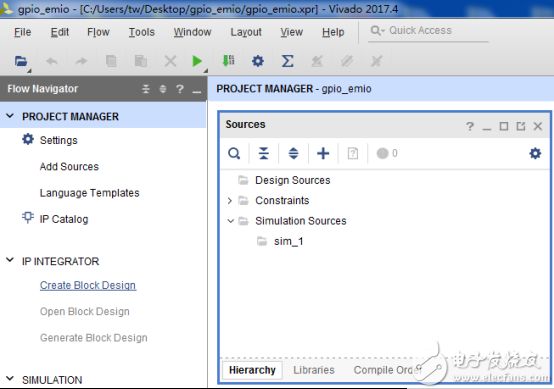

生成的vivado工程(如果不知道如何生成可以参考前面的工程)

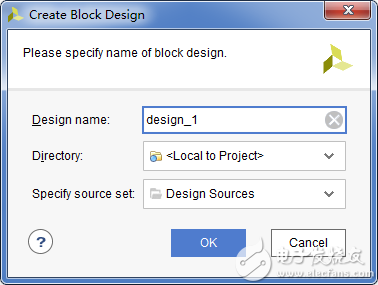

Step1新建Block Design

点击OK

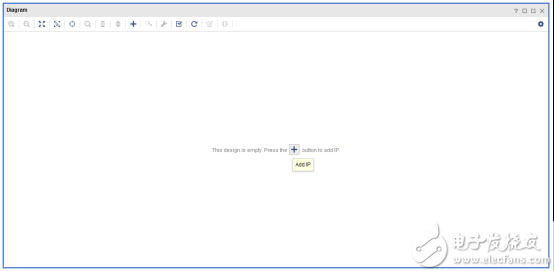

Step2添加PS的IP核并配置

点击这个Add IP添加IP核

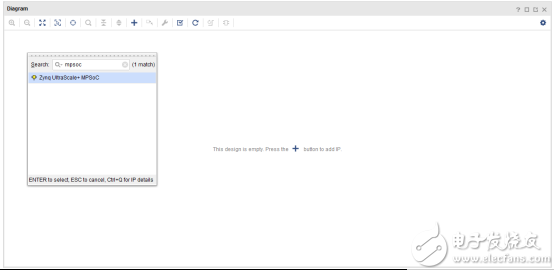

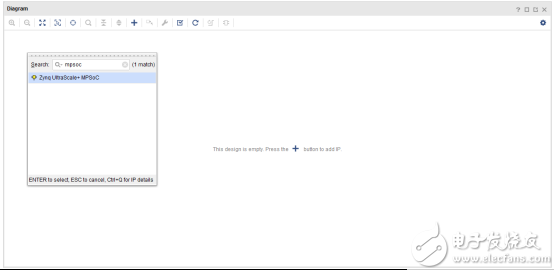

输入mpsoc,然后双击Zynq UltraScale+MPSoC添加mpsoc核

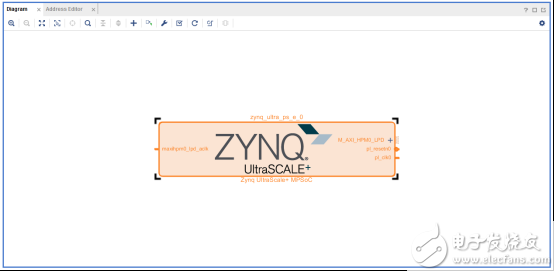

zynq mpsoc核如下图所示

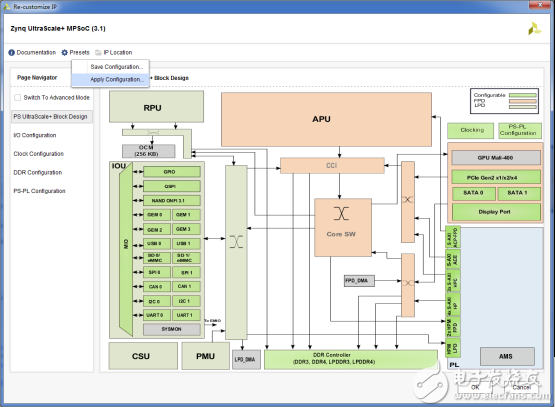

双击zynq mpsoc核导入配置文件

Presets-->Apply Configuration

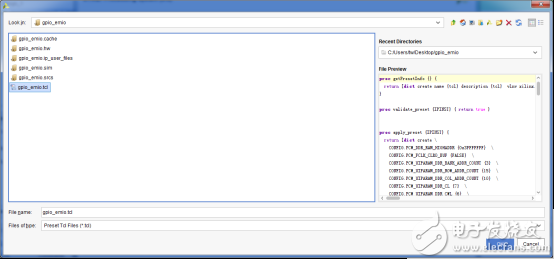

这里导入的是gpio_emio.tcl配置文件

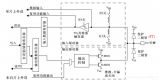

配置完成后,如下图所示

在gpio管脚上右击选择Make External,引出的gpio管脚如下图所示

……

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

发布评论请先 登录

相关推荐

高速图像处理卡设计原理图:527-基于3U VPX XCZU15EG+TMS320C6678的信号处理板

C6678信号处理板 , FPGA 信号处理 , FPGA开发平台 , XC7Z045板卡 , XCZU15EG板卡

DAC38J84EVM SYNC信号无法通过FMC-LHC接口输入到FPGA,怎么解决?

我在使用一块第三方的alinx xczu9eg ultrascale+mpsoc开发板进行基于JESD204B的DA开发.

我现在使用的FMC子板是DAC38J84EVM , 其中DAC芯片的同步

发表于 11-26 06:43

SOC GPIO操作

sapphire Soc提供了两个GPIO组每组有4个GPIO,定义为GPIO[3:0],其中只有GPIO[1:0]可以支持中断。中断在程序

全志模块设备开发之GPIO编程基础介绍

编号为从N到N+ngpio-1

” label”属性,用于判断控制器,并不总是唯一的

9.3 IMX6ULL开发板GPIO编号的确定

每个芯片可以有N组GPIO,每组GPIO最多有

发表于 08-05 13:33

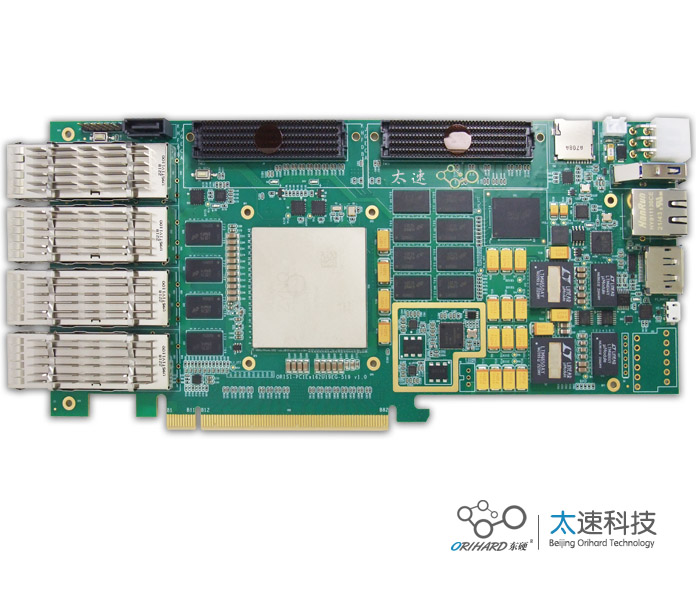

学习资料:520-基于ZU15EG 适配AWR2243的雷达验证底板 高速信号处理板 AWR2243毫米波板

本板卡系太速科技自主研发,基于MPSOC系列SOC XCZU15EG-FFVB1156架构,搭载两组64-bit DDR4,每组容量32Gb,最高可稳定运行在2400MT/s。

米尔基于NXP iMX.93开发板的M33处理器应用开发笔记

资源MYD-LMX9X开发板(米尔基于NXPiMX.93开发板)3.软件资源Windows7及以上版本软件:IAREmbeddedWorkbench4.板载固件调试

产品原理图:619-基于双FMC接口 ZU19EG 的6U VPX采集存储计算处理卡

该板卡是采集、存储、计算、管理一体的高集成度、加固型的信号处理平台,北京太速科技本板卡基于Xilinx公司Zynq UltraScale+ MPSOC系列SOC XCZU19EG-FFVC1760架构,其中,ARM端搭载一组64-bit DDR4,总容量达4GB,可稳定运行在2400MT/s。

什么是GPIO?GPIO组成原理

GPIO全拼叫General Purpose Input Output(通用输入输出)简称IO口也叫总线扩展器,GPIO口是由引脚,功能寄存器组成,不同的架构中的GPIO封装不同,所使用的引脚数与寄存器数不同,具体可以参考芯片手

发表于 04-28 12:30

•7010次阅读

XCZU15EG设计原理图:523(ZCU102E的pin兼容替代卡) 基于 XCZU15EG的双 FMC通用信号处理板

本板卡基于Xilinx Zynq Ultrascale+ MPSOC系列SOC XCZU15EG-FFVB1156架构,PS端搭载一组64-bit DDR4,容量32Gb,北京太速科技板卡,最高可

KU115+ZU19EG+DSP6678的双FMC 6U VPX处理板

和 1 片 Zynq UltraScale+ MPSoC 家族的 XCZU19EG-2FFVC1760I 以及 1 片 TI 公司的 DSP 芯片 TMS320C6678ACYPA。

请问有XCZU9CG-FFVC900的原理图库吗?

有大佬分享一下XCZU6CG-FFVC900、XCZU9CG-FFVC900、XCZU15EG-FFVC900的原理图库?

发表于 04-01 15:43

XCZU3EG开发笔记之gpio_emio

XCZU3EG开发笔记之gpio_emio

评论