在本文中,我们将讨论定制设计的任意波形发生器(AWG)板的PCB布局。

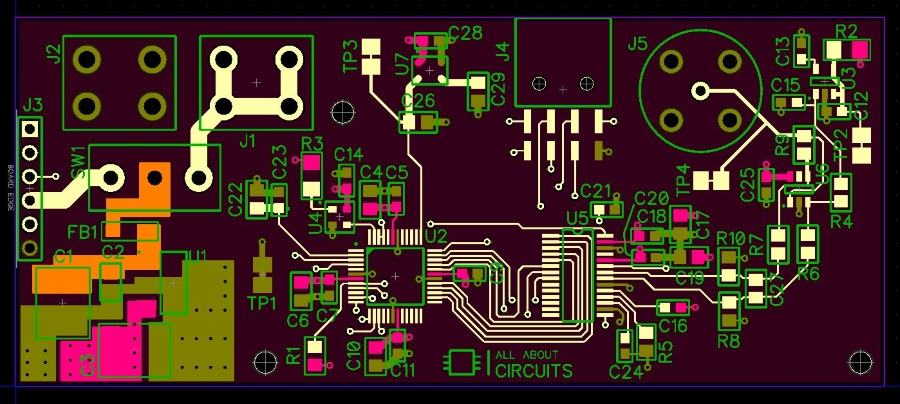

这是我写的关于设计的第四篇文章我的AWG PCB。这就是电路板的样子:

其他三篇文章涵盖了微控制器, DAC和DAC的输出电路。现在是讨论布局的时候了;在本文之后,我们将考虑技术介绍完成,我们将继续进行实际项目。

基础知识

此PCB,像几乎所有的PCB一样,是一个四层板。在我看来,将你自己限制在两个层次是不明智的,除非你正在处理一个非常简单的电路,否则你真的需要削减成本。

四层布局在路由方面是有益的。性能:布线,因为通过内部平面的连接几乎完全消除了电源和接地走线;和性能,因为内部平面允许低电阻,低电感电源和接地连接。当您需要提供宽大的铜区域以改善热性能时,所有内部平面连接打开的额外顶层和底层空间非常方便(例如,确保您的LDO或电机驱动器不会过热并进入热关断状态。

电源

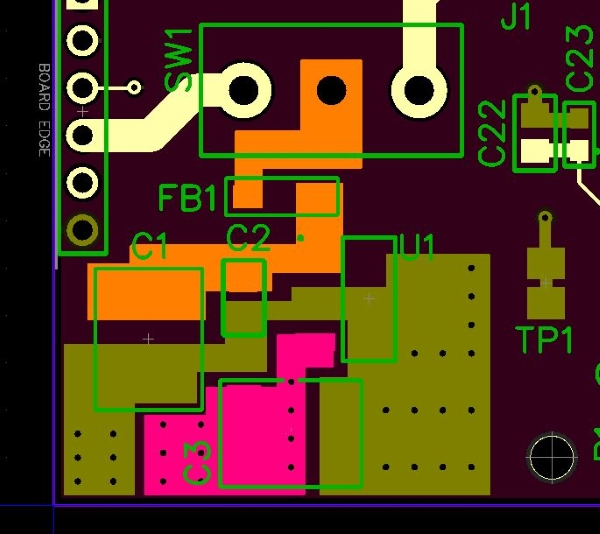

我们不妨讨论电源电路热设计主题。

您可以看到所有电源连接如何使用大痕迹或铜倾泻。 AWG没有很高的电流要求,但是如果你有房间,那么你可以选择大的(=低电阻,低电感)迹线。

您还可以看到,我已经很容易将热量从调节器(U1)移到周围环境或PCB的其他部分。 U1的散热片连接到一个大的铜浇口,这个铜浇注通过过孔,将热量传导到内部接地层。如果我真的担心散热问题,我也可以将这些过孔连接到电路板底部的铜浇注,但在这种情况下,它会完全过度杀伤。

微控制器

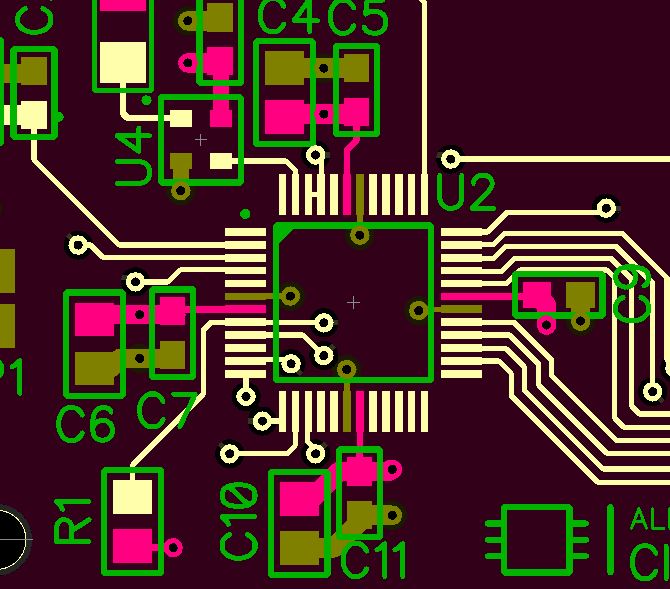

这是电路板微控制器部分的布局:

去耦电容(C4,C5,C6,C7,C9,C10,C11)围绕芯片周边排列,非常靠近各自的电源引脚和连接电容的通孔内部飞机。注意较小的帽子是如何始终靠近电源引脚的;这是因为我们更多地依靠低值电容进行高频旁路,因此首要任务是尽量减小较小电容和引脚之间的电感和电阻。

请注意,U4是一个10 MHz的MEMS振荡器,也非常靠近微控制器的时钟输入引脚。最小化携带高频数字信号的迹线的长度总是一个好主意。首先,存在噪声优势:更短,更直接的迹线减少了否则将耦合到相邻迹线的噪声量,并且更短的迹线还减少了电磁干扰(EMI),因为它作为天线的效率较低。第二个问题与传输线效应有关。最小化迹线长度是避免与信号反射相关的问题的简单方法。但是,除非您处理长互连或非常大的PCB,否则反射不是10 MHz范围内频率的重要问题。

并行总线

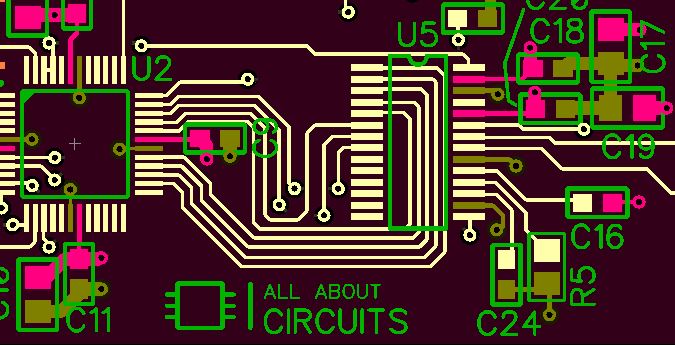

下一张图显示了DAC的布局;微控制器和DAC的布置使得8位并行数据总线从微控制器的右侧传输到DAC的左侧。

您可能已经注意到,这是令人烦恼的情况之一,其中引脚配置与您想要的相反:DAC的输入引脚从第7位移到位0向下,而MCU的输出引脚从位7移动到位0向上。我无法通过重新分配微控制器引脚来解决这个问题,因为我希望数据位对应于端口2寄存器的实际位(这样我就可以在不移动位的情况下向DAC写入一个完整的字节)。所以我最终得到了一些笨拙的路由,但没有什么可怕的。

当你布置一个并行总线时,总是很好地认识到跟踪长度,尽管在中等频率下没有什么可以强调的。通过迹线的信号的传播时间可能是150皮秒/英寸。因此,如果您有两条长度不匹配为1英寸的迹线,则一条信号将在另一条信号之后达到150 ps。如果您的信号以相应周期远大于150 ps的频率转换,则这一英寸不匹配不会导致问题。即使在100 MHz(对于并行总线来说相当快),周期为10 ns,即比一英寸不匹配的到达时间差异大约67倍。

大图

以下是整个布局:

我总是喜欢在PCB布局中保持信号和功能的逻辑流程。我认为这种方法可以使设计过程更加简单,并且可以提供更好的电路板。 AWG布局从左到右进行:从电源输入和通信输入/输出,到电源电路,到处理器,再到DAC(由处理器控制,构成电路板从数字到模拟的转换)到模拟信号调理电路,最后到输出连接器。在功能流程中没有特定位置的部件 - 例如振荡器(U4),DAC的无源元件(C16,R5等)和电压参考(U3) - 布置在它们支持的组件附近。

结论

我们现在已经详细了解了这个定制设计的任意波形发生器的原理图和布局。在下一篇文章中,我们将通过简单的数模转换任务启动并运行电路板,我们将继续阅读涉及更高级功能和应用的其他文章。

-

微控制器

+关注

关注

49文章

8830浏览量

165578 -

pcb

+关注

关注

4415文章

23955浏览量

426009 -

波形发生器

+关注

关注

3文章

327浏览量

32813

发布评论请先 登录

任意波形发生器pcb是怎样布局的

任意波形发生器pcb是怎样布局的

评论