在本届Hot Chips大会上,AI 仍是主角,但 AI芯片设计已经不是主角,从一个新颖的话题变为了成熟的工程。本文作者姚颂是赛灵思 AI 业务高级总监、原深鉴科技联合创始人,他用近万字洋洋洒洒分享了对这次大会的观察与思考,必须收藏细读!

2019 年 8 月 19 日到 21 日,第 31 届 Hot Chips 大会在斯坦福大学成功举办。从 2016 年开始,这是我参加的第四届 Hot Chips。在之前的三届 Hot Chips,有两次我作为演讲者参与(2016 年与 2018 年),有一年作为展商参与(2017 年),这一次是第一次没有任何任务来参加 Hot Chips,终于可以安心地听取报告、进行学习。

而在之前 Hot Chips TPC meeting 刚结束时,已经从几位技术委员会的成员那里听说今年的竞争异常激烈,Xilinx 的同事 Ralph Wittig 更是评论,这一届 Hot Chips 的论文质量是他觉得过去十年中最好的,让人不由得对本次 Hot Chips 充满期待。

本次大会确实是有非常多非常扎实的工作,也展现了整个处理器与高性能芯片领域行业的趋势与变化。本系列文章将介绍我在 Hot Chips 大会上的几点观察与思考,涵盖以下几点内容:

Cerebras 其实是在帮大家追求心中的梦想,祝福,但也存在挑战;

AI 仍是主角,但 AI 芯片设计已经不是主角,从一个新颖的话题变为了成熟的工程;

异构是大势所趋,无论赛灵思还是英伟达,都在持续前进;

安全是一个越来越重要的话题;

FPGA 在各种不同应用中扮演着重要角色;

集成电路工艺演进:未来越来越难,但一定会有突破。

文章也将介绍一些 Hot Chips 会议上发生的趣事。未经特别说明,图片均来自于本人在 Hot Chips 拍摄的照片。

本文作者姚颂是赛灵思 AI 业务高级总监、原深鉴科技联合创始人

No.1Cerebras: 会议最大热点

本届 Hot Chips 最大的亮点,毫无疑问是 Cerebras 的wafer-scale engine (WSE)。我们通常的芯片,一片 wafer 可以切出几十到上万片不等的芯片,而为了追求极致的性能、最大的片上存储,Cerebras 选择了一条极端的路线,让整片 wafer 就是一片芯片。当 Cerebras 的联合创始人 Sean Lie 拿出样品实物的时候,会场里响起了掌声,这也是本次大会唯一一次不是在报告开始与结束时候礼节性的掌声。

WSE 芯片,由 12x7=84 个 die 组成,共有 40 万个为深度学习优化的计算核,片上存储达到了惊人的 18GB,超过了很多电脑的内存大小。这样一颗芯片,在我眼里是有特殊的美感的:如同看到长城和金字塔,这样在技术水平极其低下时,似乎人类无法实现的杰作;也如同看到了蒸汽朋克电影中的庞然大物,复古而雄伟;又如同最为精密和复杂的机械表,无数精巧的结构让人感叹。这是在大的范式没有改变的情况,当前工程技术可以做到的极限了。

Cerebras 的报告是极少数全篇没有任何性能数字的报告,只有一句话 “It’s working”。这样一篇论文能够被 Hot Chips 录用来进行报告,足见其受到的关注和重视。而我个人有一个习惯,除了认真听别人说做了什么,更会去想他们没说什么。而在这次,他们只说了 “It’s working”,而并没有说 “It’s working well”,也许就是在暗示些什么。

Cerebras 的 WSE 芯片仍然是有非常多待解决的问题的:

(1) 这样一片芯片,尽管做了很多的容错设计,其良品率怎样,仍然是一个疑问;

(2) 传说中 15kw 甚至 50kw 的功耗,怎样去实现良好的散热;

(3) 整个芯片由 12x7 个 die 组成,die 之间的通信是与台积电联合研发的新型工艺,其效果如何;

这样许许多多的问题,都值得追问下去,而在报告现场,尽管 PPT 上有相关的页来阐述是用怎样的思路来解决,但是 Sean 基本上是一带而过,没有介绍任何细节,这也不由得不让人猜测,在这些地方,可能仍然存在着非常多的技术问题需要解决。

对于我个人来说,我非常佩服 Cerebras 的 CEO Andrew Feldman 这样一位有魄力、有远见的成功的连续创业者:他曾经做过四个公司,都以上市或者并购成功退出。我也非常佩服包括 Sean Lie 在内的 Cerebras 的工程师,勇于挑战最极致的技术路线。任何一条技术路线走通都非常不容易,希望 Cerebras 能够一个一个解决路上的技术难题,这不仅仅是 Cerebras 一家公司的事情,也是所有有技术信仰的芯片行业工程师与研究者的共同心声 —— 大家没有机会和财力去做这样一件激动人心的事情,希望你们能做好!

No.2AI 芯片从火热到理性

Cerebras 是本次报告最大的亮点,也是被大家关注最多的 “AI 芯片” 的代表。然而,实际上本次大会,AI 芯片的设计本身,已经不是被大家关注的重点了 —— 更进一步说,实际上从 2017 年到现在的两年间,纯数字电路的 AI 芯片的发展已经几乎停滞了,除了 sparsity 和 low-bit(比如 1bit 网络,或者 tenary 网络),在 AI 芯片,很少听到新的题材了。

本次大会特斯拉的报告,也充分体现了这一点:许多人最开始对于特斯拉的报告 “Compute and redundancy solution for Tesla’s Full Self driving computer” 充满期待,因为这是少有的可能能介绍完整自动驾驶系统设计的报告,而结果却令人失望:整个报告花了 80% 的时间,在介绍底层架构怎样设计,卷积计算的流程如何,指令集如何设计,pooling 单元如何设计,而在介绍这些设计的时候,许多抬头听报告的人,都将视线转向了笔记本电脑或者手机。另一个更直观的体现是,在报告结束后的 Q&A 环节,提问者的问题都在关注在自动驾驶系统中,两片特斯拉自动驾驶芯片是如何配合的,如果真的发生了错误,是如何进行纠错的,而没有人再去拘泥于底层架构设计。

此次 Hot Chips 仍然有不少 “AI 芯片” 的报告,阿里,华为,Cerebras,Habana(一家以色列不错的创业公司),Tesla,nVidia,Xilinx,Intel,Princeton,然而,每一项工作都是在底层架构设计之外,还有更大的亮点:

阿里实现的应用是少见的 text-to-speech,从文本到声音合成,而不是传统的 CNN 和 LSTM 加速;华为的达芬奇芯片做了 logic die 与 HBM 的直接堆叠,而不是传统高带宽芯片的 2.5D interposer 的模式,Cerebras芯片是最极端的 wafer-scale 芯片,Tesla是带有冗余设计的自动驾驶系统,nVidia是 NoC+NoP 的可扩展架构,Xilinx是全新的 Versal 芯片与拥有更多可编程性的 AI engine 一起,Princeton的研究工作是用 SRAM 做 in-memory computing。

此次 Hot Chips 大会的情况也充分说明,AI 芯片的技术噱头时代已经过去,越来越多的人在考虑,怎样去改变当前的范式,用更新的底层技术去实现更好的性能;是否能够真的做出可量产的芯片,之后怎样去和应用更好的融合,实现一个整体好用的系统。在单纯数字芯片模式下,单纯新的体系结构的创新,已经无法带来任何新的机会了 —— 我们必须进一步向前看。

No.3 异构计算:大势所趋

异构计算,Heterogeneous Computing, 不是一个新鲜的话题,然而真正出现大量使用的异构计算平台,却是从近几年的事情了。异构最重要的涵义,是系统由多种不同功能的部分组成,让每个部分做它最擅长的事情,而不是用统一的平台来做所有的事情。

异构计算的兴起,与 AI 芯片的兴起,本质上都有一个核心原因,摩尔定律的放缓甚至结束(摩尔定律的话题也是一个稍有争议的话题,在 Philip Wong 教授的 Keynote 中,他认为摩尔定律 “well live”,这一点我们在下个部分中再讨论)。

在过去几十年,芯片性能的增长,过半是由于制造工艺的进步带来的。在上图AMD CEO Lisa Su的报告中,也可以看到对于 GPU,过去十年性能进步最重要的因素,也还是制造工艺的进步,占到了 40%。而随着摩尔定律的放缓,由制造工艺带来的进步越来越小,我们必须更多地依赖微架构(也即图中占比 17% 的 Microarchitecture 部分)和系统层面的进步来实现整体的进步。而这其中,最直接的方式,就是设计 Domain-specific architecture(DSA),放弃一部分通用性,来获得更大的性能提升。通常而言,越专用,通用性越差,越容易取得更好的性能。

也正因为此,我们看到了 GPU 在图像渲染上碾压 CPU,我们看到了在不同通用性层次支持深度学习的各类 DPU/NPU/NNP/MLU/DLA/VPU。比如,我们可以选择支持各类机器学习算法、而不仅仅是深度学习的 MLU,也可以选择只支持深度学习推理的 DPU,而如今又出现了不少专注在深度学习训练的专用芯片。

(在 2017 年 3 月 GTIC 会议报告的 PPT 截图)

2018 年 3 月份在智东西组织的 GTIC 大会上,我曾经讲过一个和 nVidia VP of BD,Jeff Herbst 的小故事。在 2017 年 Hot Chips 期间,我约着去拜访了 Jeff,也一起吃了个晚餐。在聊到对于 AI 芯片未来产品时候,我说 “I bet that you will sell a chip with no GPU in two years”,我打赌英伟达会在两年内卖一颗没有 GPU 的芯片。但是没想到其实英伟达的新产品来得如此之快:在 2018 年 2 月的 CES,英伟达 CEO 黄仁勋就公布了面向自动驾驶的 Drive Xavier 芯片,号称 30T 算力,30W 功耗。但是当我们认真的看 PPT 上的数字时候会发现,这 30T 算力,有 10TOPS INT8 来自于 DLA,有 20TOPS 来自于 Tensor Core,都不是传统的 GPU。GPU 部分只有 512 个 CUDA core,只有 1.3 CUDA TFLOPS。也就是说,这个 GPU 的算力几乎可以忽略不计,可能只是用来做大屏幕显示的。在我和 Jeff 见面仅仅半年之后,远没有到两年,nVidia 就已经开始推出几乎没有 GPU 的芯片了,而似乎许多人没有注意到 —— 这也充分说明了软件接口的重要性,当 nVidia 把所有的都做成兼容 CUDA,再加上上层的 Library 和各类 Framework 进行封装,大家已经关注不到底层的改变了。

(HotChips 31 现场 nVidia 的报告)

在这次 Hot Chips 大会上介绍的Turing GPU,虽然还挂着 GPU 的名字,其实也已经是一颗异构计算芯片,不仅仅是传统那些 SIMD 单元,总共由 Turing SM, RT Core,与 Tensor Core 三个部分组成。报告人 John Burgess 介绍,传统做光线追踪,对于每一条光线,要反复花费数千个时钟周期,才能正确计算和物体的交界点在哪里,而一次渲染会有非常多条光线要计算,因此他们才想要设计 RT Core 来专门解决光线追踪的问题。这就是典型的异构与 DSA 解决问题的方式:为一个计算复杂的任务设计专用加速器,用异构的系统来做整体的计算。

(HotChips 31 现场 Xilinx 的报告)

而异构计算一个特别极致的案例就是 Xilinx 本次介绍的Versal,Xilinx 的第一款 ACAP 产品。Versal 上同时有两个 arm A72 核,两个 arm R5 核,可编程逻辑也即 FPGA,还有 AI Engine 与 DSP Engine!这样一颗芯片,可以将应用做非常细致的拆分,AI 部分在 AI Engine 上,信号处理部分在 DSP Engine 上,主控和通用计算部分在两个不同的 CPU,其他需要加速但不能很好利用 AI Engine 与 DSP Engine 的部分在中间的可编程逻辑上。这种感觉就很 “分而治之”,又很像经济学上的 “价格歧视”—— 同样的产品,为不同购买力的人群分别制订他们能接受的最高价格,整体获得的收益会更大。在这里,我们是,同样一颗芯片,但是为不同应用分别划出专用的一块区域,去实现最好的性能。

毫无疑问,越来越异构化的芯片会是大势所趋。但是,实际上,背后依然有非常多的问题,比如,系统与应用层面的考虑,比如,软件编程的问题。当 DSA 越来越专用,必须去考虑整个芯片是否合适于使用的应用,必须有更多和行业结合的软件,而不仅仅只是像原来一样提供一个通用的平台而已。而复杂异构系统的编程开发,在业界依旧是一个没有完全解决好的问题。对于这样一颗异构芯片,我怎么去找到每个部分是否适合某个任务,是手动地划分任务、为不同部分单独编程再拼到一起,还是统一的软件界面去编程、之后自动映射?还有很多问题需要去解决。

No.4安全,是一个越来越重要的话题

在 2018 年初,CPU 行业曝出了两个巨大的安全漏洞,“Spectre” 和 “Meltdown”,其核心原因是因为为了追求更好的性能,CPU 做了很多的优化工作,比如分支跳转预测,和乱序执行,而不是顺序的一条一条执行指令,执行到了再去内存里读取数据。而近几年也有一个很大的趋势,就是原来仅仅用在支付等场景的 https 协议,开始被越来越多的使用,大部分主流网站,比如常用的百度,微博,等等,已经全站都是 https 化了。哪怕我不是一个安全方面的专家,但是我也能感受到,各方面的因素,让 “安全” 这两个词变得越来越重要:我们希望在云计算上运行的任务是安全的,我们希望存储在云端的数据是安全,我们希望与服务器的通信是安全的。

(HotChips 31 Tutorial来自微软 Azure 团队的报告)

(HotChips 31 Tutorial来自 AWS 团队的报告)

在本次 Hot Chips 大会,我们明显也看出了各家互联网公司与芯片公司对于安全的重视,并且把加密变成了产品流程中的重要一环。如上两图,在微软的 tutorial 中,微软介绍了自己正在开发了Corsica 芯片,将文件的压缩解压缩与加解密做到了一起。AWS 的Nitro 项目中,也开发了自己的安全芯片。而在 Intel 的Optane 项目中,加解密也已经融合到了存储一体。

可以想象,未来的存储一定是和加解密融合到一体的。我们也可以猜想,平头哥是不是也会做阿里自己的安全芯片?

No.5两个彩蛋

在 Hot Chips 会场拍摄的两张照片,总计将四位大咖拍摄进去了,大家都认出来了吗?

No.6 黄汉森报告回顾:摩尔定律没有终结

“在互联网领域,阿里、腾讯像两座大山横贯在路上,利用其强大的资金、技术与产品能力、渠道、用户等等优势阻挡住了无数的创业公司。许多成长起来的后起之秀,都是找到自己的途径去规避巨头的最强点:京东自建物流,拼多多充分发掘下沉市场,今日头条用推荐引擎取代搜索引擎。在 AI 芯片领域,我们终于也有了类似的感受,但许多企业还做着想正面直接挑战巨头的计划。而先进工艺下芯片的制造成本,也成了创业公司很难迈过去的一道坎。”

在Hot Chips 31 大会观察与思考系列文章的最后部分,我想结合 Philip Wong 老师的 Keynote,一起讨论一下集成电路制造工艺演进的问题,也想谈一下我自己关于制造工艺对于 AI 芯片创业企业的影响。

在去年 8 月,斯坦福大学著名教授 Philip Wong(黄汉森,以下简称黄教授)确认加入台积电,担任研究副总裁,在业界传为佳话,让大家觉得又是一例产学研结合的典型案例。黄教授多年来在存储领域有非常深的建树,也在碳纳米管器件领域有着深入的研究,他的加盟毫无疑问说明 TSMC 会在存储方面更下功夫。

黄教授一上来便抛出了他最重要的主题,他说:

“Moore’s law is not dead, is not slowing, is even not ill. It’s well alive!”

(摩尔定律没有终结,也没有放缓,更没有生病。摩尔定律活得好好的!)

在之后,他介绍了台积电在工艺节点演进上的路线图与展望,并且阐述了三条他认为可以继续延续摩尔定律的技术路径:

1. 系统集成的方式,如用 interposer 的方式将 SoC 与 DRAM 可以集成在一起,如 SiP,如 Chiplet;

2. 更进一步存储与计算的集成,比如直接将存储与计算部分在垂直方向上进行堆叠,采用更细致和极致的堆叠方案 N3XT;

3. 新的底层材料和技术,比如碳纳米管。

特别地,他强调了半导体技术的演进,总是被不断变化的应用需求所引领的,如上个世纪 80 年代到 2000 年的 PC / 互联网,到 21 世纪至今的移动互联网,在新的时代我们也会更多的去关注 AI 与 5G 的底层需求。

No.7制造工艺之于 AI 芯片

黄老师有理有据地阐述了他的观点:摩尔定律很健康!然而俗话说 “屁股决定脑袋” ,他这样说,我们就无从知道,有多少比例的原因是他正在台积电担任集团研究副总裁。

如在 AMD CEO Lisa Su 的报告中,就已经画出来了工艺演进的曲线,可以看到 10nm 与 7nm 工艺的发展速度已经很大程度上偏离了原来的 projection。虽然系统级封装,利用 Interposer 方式将 HBM 与计算部分集成到一起,大大提升了存储带宽,但是这并不是集成密度的提升。

而芯片制造工艺对于行业影响最大的,并不只是放缓,其制造成本也有非常大的影响:对于晶圆厂和 Fabless 设计公司均是这样。

对于晶圆厂来说,7nm 等先进工艺生产线动辄数十亿美金的投资是一笔巨大的负担。于是我们看到,在 2018 年 8 月,第二梯队的晶圆厂联电、Global Foundries 先后宣布放弃 7nm 工艺。在整个市场上,拥有最先进生产工艺的代工厂,只剩下了台积电、Intel 和三星。

对于 Fabless 的芯片设计公司,问题同样巨大。对于台积电 28nm、16nm、7nm 的芯片来说,要完成一颗芯片的量产,其 IP 购买、MPW、量产的成本在数百万美金,千万美金,亿美金以上 —— 如果考虑人员成本、设备成本等等的,这个数字还会高上不少。这就导致只有出货量极大、收入极高的几家大厂能够负担得起最先进工艺。比如大家耳熟能详的联发科,如今也只能先使用着台积电的 12nm,而不能像高通和海思一样使用 7nm 工艺。

先进制造工艺的成本问题,对于 AI 芯片创业公司也有很大影响。一般的 AI 芯片创业公司,可能只能负担得起 28nm 工艺,或者说最开始只敢用 28nm 工艺进行尝试。融资足够多的 AI 创业企业才能尝试得起 16nm 工艺的生产费用。在全球数十家 AI 芯片创业公司当中,我只听说过有一家敢于去使用 7nm。

如地平线在周五发布的征程二代芯片,就是使用的台积电 28nm 工艺(虽然 28nm HPC + 是多次改进的版本,不展开详细介绍),这也是大部分嵌入式 / 终端 AI 芯片目前选择的制造工艺;在 Hot Chips 上吸引了众多眼球的 Cerebras 与 Habana,均采用的 16nm 工艺 —— 而这也是迫不得已,因为他们的应用场景在云端,必须追求极限的高性能,所以必须使用能负担得起的最好的工艺,也必须选择 HBM 或者更加极端的存储方案(如 Cerebras 使用的 Wafer-scale engine,采用 18GB SRAM,单片成本据说在 100 万美金左右)。

这就导致一个巨大的问题:CPU 与 GPU 的竞争中,CPU 并不能凭借制造工艺的优势,来弥补通用性带来的性能不足,因为二者并无制造工艺上的代差,对于特定应用,性能差距本来也很大;而大公司与 AI 芯片创业公司之间财力的差距,导致大公司的芯片可以选择更先进的制造工艺,而 AI 芯片创业公司却只能负担得起相对成熟的工艺。这样的话,即便在体系结构设计上,AI 芯片创业公司的芯片在特定任务上有数倍的优势,也可能被制造工艺的差别给抹平。大公司可以通过制造工艺的碾压,获得更好的性能,再通过其通用性和原有的渠道、用户生态的优势,卖出更多的芯片来收回成本。

在互联网领域,阿里、腾讯像两座大山横贯在路上,利用其强大的资金、技术与产品能力、渠道、用户等等优势阻挡住了无数的创业公司。许多成长起来的后起之秀,都是找到自己的途径去规避巨头的最强点:京东自建物流,拼多多充分发掘下沉市场,今日头条用推荐引擎取代搜索引擎。在 AI 芯片领域,我们终于也有了类似的感受,但许多企业还做着想正面直接挑战巨头的计划。而先进工艺下芯片的制造成本,也成了创业公司很难迈过去的一道坎。

没有机会了吗?也不是。发掘巨头没有覆盖到,但是有潜力的新市场,也许机会正在打开,如拼多多一般;用新的底层技术,如存内计算,去获得数量级的提升,而不是在原来传统数字芯片上硬拼,就好像抖音用短视频取代了长视频与图片文字的社区;在具体的领域,去做整个系统与产品层面的优化,而不只是做芯片,提供更好的服务,就如昨晚在朋友圈刷屏的 ZAO,从 DeepFake 单个算法出发,做成了细节考虑充分的完整应用;利用好不同地区之间的政策与文化的差异性,就好像滴滴在中国击败了 Uber。

谁能够跨过这道门槛,真正和巨头们掰一掰呢?我个人看好华为与阿里平头哥。前者有足够多的资源,也可以排在世界前几的的研发实力与工程能力,软硬件都非常强,有机会在市场终于被做大之后进场收割;后者,在有足够多的资源和很强的技术能力外,还有明确的应用以及长期的集团战略,也能在其看重的领域掀起波浪。而对于创业企业,找到与巨头的差异性,无论是细分市场、系统集成度、地区政策差异、还是底层技术变革,强化优势,再拿到足够多的资源,我相信也希望能够跑出几家在各自领域拥有相当地位的公司。

刘慈欣在《流浪地球》里写过一个著名的谜语:“你在平原上走着走着,突然迎面遇到一堵墙,这墙向上无限高,向下无限深,向左无限远,向右无限远,这墙是什么?”

对于 AI 芯片创业企业来说,眼前这墙真的很大,但也不是无限大。

-

处理器

+关注

关注

68文章

19281浏览量

229787 -

集成电路

+关注

关注

5388文章

11544浏览量

361779 -

AI芯片

+关注

关注

17文章

1886浏览量

35014

原文标题:姚颂万字长文:Hot Chips不容错过,史上最大芯片&摩尔定律

文章出处:【微信号:AI_era,微信公众号:新智元】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何把一个振动信号转变为声音信号需要如何组建电路?

解码“新质生产力”,一站式AI工具成工业智能化升级关键

安森美推出新款碳化硅芯片,助力AI数据中心节能

一个成熟的PCBA设计通常包含哪几个方面?

risc-v多核芯片在AI方面的应用

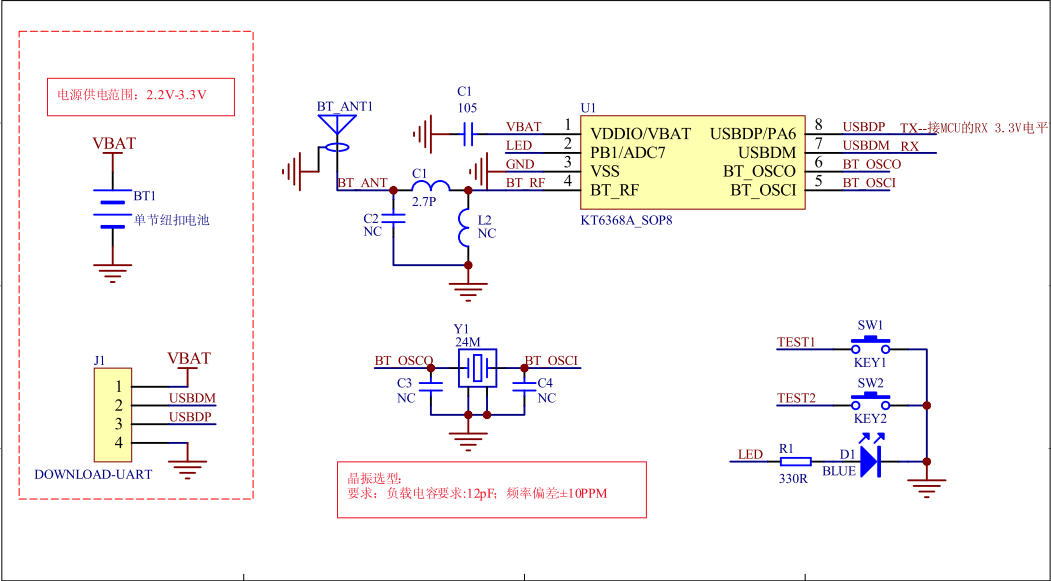

KT6368A蓝牙主从一体芯片_功能简要说明

AI芯片设计已经不是主角,从一个新颖的话题变为了成熟的工程

AI芯片设计已经不是主角,从一个新颖的话题变为了成熟的工程

评论