2019年,EUV光刻(EUVL)将达到一个重要的里程碑。经过多年的等待,先进光刻技术终于进入大批量生产。EUVL将率先用于7nm节点(IMEC N8或代工厂N7)逻辑后段(BEOL)的最关键金属层和通孔。与此同时,研究中心正在探索未来技术节点的选择,这些节点将逐步纳入更多的EUVL印刷结构。在本文的第一部分,imec的干法蚀刻研发工程师Stefan Decoster比较了在N3及更先进技术节点下,不同的多重图形化方案的优缺点。

与过去相比,研究人员现在已经将EUVL作为存储器关键结构的图形化工艺的一个选项,例如DRAM的柱体结构及STT-MRAM的MTJ。在本文的第二部分,IMEC的研发工程师Murat Pak提出了几种STT-MRAM关键结构的图形化方案。

在后段引入EUV多重显影

今年,一些主要的代工厂将首次在其大批量生产线中使用EUVL来处理逻辑7nm(N7)芯片。它们将EUVL引入BEOL的最关键金属层(local M0至M3),以及互连这些金属层的过孔中。在这些层中,线和沟槽具有36-40nm量级的节距。沟槽与沟槽的隔断相互垂直,以便在连续沟槽中产生隔断。下一个技术节点N5会运用到28到32nm之间的金属节距。

“2017年,我们已经证明这些32nm节距线可以在一次曝光中直接用EUVL进行图形化,”Stefan Decoster补充道。“或者,可以使用混合选项,其中基于193i的SAQP与EUV block相结合。”

图示采用193nm浸入式SAQP图形化的32nm节距M2层,以及直接由EUV图形化制作的隔断(block)。

从EUV单次显影到EUVL多重显影

同时,很明显,EUVL单次曝光已经达到了32纳米到30纳米节距的极限。Stefan Decoster:“超过30nm节距,使用当前的EUVL技术(即0.33数值孔径(NA))需要采用多重图形化技术,进一步缩小尺寸。这些技术通常涉及将芯片图案分成两个或更多个更简单的掩模,并且可以以不同的风格存在。EUV多重显影将比原先想象的更早推出, 主要是由于存在随机失效。“这些失效在极小的特征尺寸下开始变得更加明显,并且限制了EUV单次曝光的实际分辨率。

IMEC N5技术节点的多重显影方案

在实践中,这意味着IMEC N5(或代工厂N3)技术节点具有21nm的金属节距,这需要EUVL multi-patterning,例如SADP或LELE,当然,IMEC还提供了另外两种方案,即193iSAQP,193i SAOP,仍然可以实现这些尺寸的线和沟槽。在成本,光刻质量和工艺流程的复杂性方面,这些技术中的每一种都具有其自身的优点和缺点。

“然而,EUVL single patterning 并不止步于此,”Stefan Decoster澄清道。“我们预计更松弛的金属层(例如M4至M7层)和关键过孔仍然可以利用EUVL单次曝光来实现。此外,IMEC和ASML正在开发下一代high-NA EUVL系统(NA =0.55),以进一步提高单次曝光的分辨率。”

IMEC N5以下:16 nm节距的图形化方案

IMEC的研究人员探索了四种不同的图形化方案,用于制作20nm节距以下的图形:基于193i的SAOP方案,基于EUV的SADP方案,基于EUV的SAQP方案和EUV SALELE方案。Stefan Decoster:“这四种方案都可以制作16nm节距的线。然而,它们在流程复杂性,成本,可扩展性和设计自由度方面存在差异,这些都是行业的重要考虑因素。我们还发现,线边缘粗糙度(LER)仍然是主要关注点。”

193nm 浸没式光刻仍然可以完成这项工作

在这些激进的节距下,193nm浸没式光刻只能与SAOP结合使用 ,从128nm节距开始经历三次图形倍增最终达到16nm节距。Stefan Decoster指出,193i SAOP的优点是线条边缘粗糙度(LER)小,但一个固有的缺点是极其漫长而复杂的工艺流程,这给过程控制和成本带来了挑战。

使用EUVL multi-patterning可以使flow变短

“出于这个原因,我们还探索了‘较短的’基于EUVL的图形化方案,即EUV的SADP”,Stefan Decoster补充道,“为了实现这种图形化方法,EUV光刻的起始节距必须为32nm。虽然目前的EUVL技术仍然能够制作32nm节距线,但是所得到的线宽不能小于16nm。因此,我们不得不应用额外的trim技术来实现在32nm节距下8nm的线宽(mandrel)。采用SADP技术,这种节距可以成功地降低到16nm。”16 nm节距的图形也可以采用更具可扩展性的EUVL SAQP方法,从更宽松的64nm节距开始。然而,对于这些基于EUV的多重图形化方法,线边缘粗糙度(LER)仍然是一个重要问题。该团队认为,这种LER可以进一步降低,例如通过选择恰当的光刻胶材料和改善光刻胶平滑性。

三种图形化flow可实现16nm节距图形(自上而下的SEM图)顶部)基于EUV的SADP,(中)基于EUV的SAQP和(底部)193iSAOP。所有三个选项的LER均在8nm line和space的情况下测得。

为了优化MTJ的LCDU,已经提出并比较了不同的EUV光刻方案。MuratPak:“首先,我们考虑了不同的光刻胶,包括众所周知的化学放大胶(CAR),以及两种不同的MCR(含金属)光刻胶。其次,我们的团队筛选了不同的底层包括旋涂碳(SOC)和旋涂玻璃(SOG),并研究了它们对光刻胶性能的影响。最后,我们研究了不同的tonalites(相当于正胶和负胶的区别,编者注),特别是CAR光刻胶(做柱)和positive tone光刻胶加上tone反转工艺(将孔变成柱)。“该团队还研究了光刻胶上的LCDU的改进是否会转移到了蚀刻之后。以上所有实验中的EUV都使用ASMLTWINSCAN NXE:3300B进行曝光。

tone反转过程的图示: (左)用正tone CAR光刻胶获得的孔和(右)在tone反转后获得的柱。

三种有可能的方案 (如下图,由编者添加)

其中一支MCR光刻胶搭配SOC和SOG均获得了相对较好的LCDU结果。第三种方案是tone反转工艺 ,最终也表现良好。“对于所有这三种方法,我们获得了超过20%的LCDU的改进,”Murat Pak补充道。“这是整个工艺流程朝向1.55nm LCDU目标的重要一步。”对于这些有前景的光刻工艺方案,其他性能指标,如工艺窗口分析,柱圆度和尺寸均匀性均已通过验证。

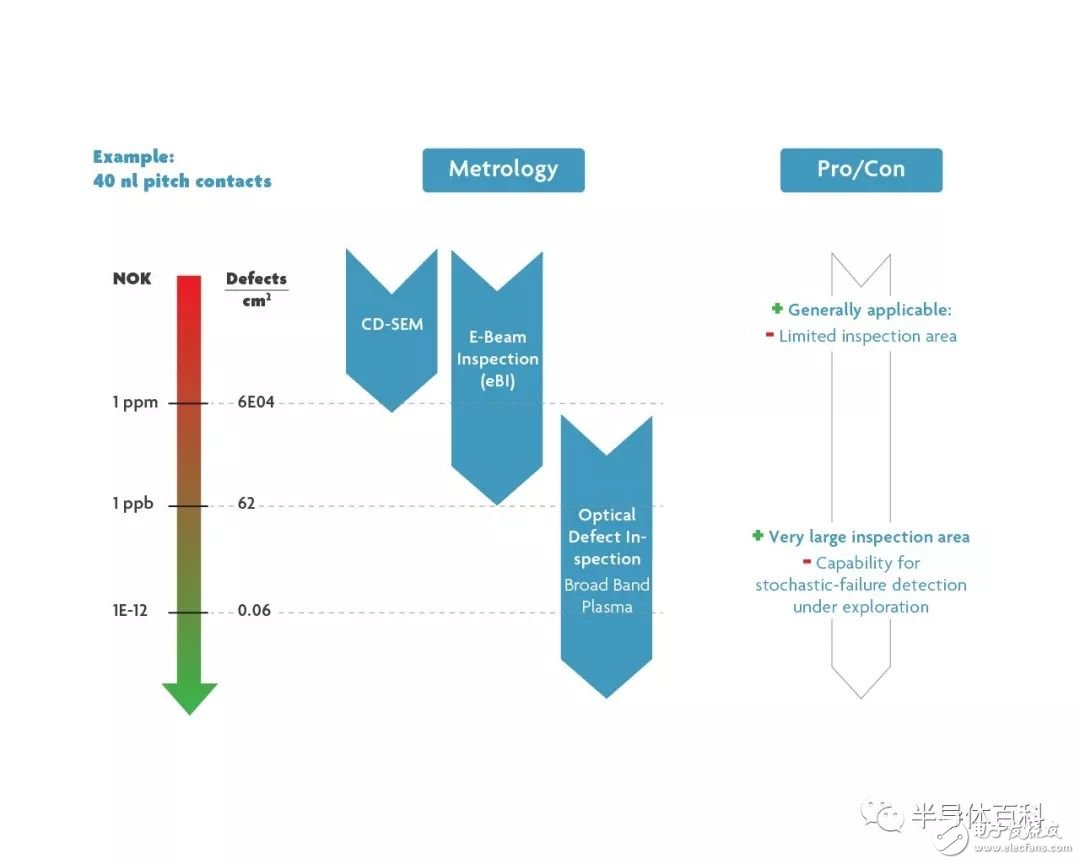

最容易使用的工具是CD-SEM(一种扫描电子显微镜),CD-SEM可被用于各种缺陷的检测,但缺点在于观察面积有限,一片完整的晶圆扫描下来需要几个月。另一种工具是E-beam,扫描面积更大,缺点就是所使用的高能电子束对光刻胶有破坏性并且对晶圆级的扫描仍然不够高效。一些公司采用多电子束扫描试图解决速度问题,但如何保证上千束电子束的校准以及如何保障电子束彼此之间不能互相影响,是他们需要解决的问题。

“光学缺陷检测是每个人都想使用的终极方案,它的优点是晶圆级别的扫描,而这正是工业界需要的。它的检测灵敏度达到0.01/cm2。” Peter De Bisschop说。通过检测光和软件的研究和优化,光学检验领域在最大限度地提高信噪比方面取得了很大的进步。

每种方法都有其优缺点

此外,光学缺陷检测能够检测非常小的缺陷也是要付出代价的。光学技术已被成功的应用于一些尺寸比较大的例如粒子缺陷检测,“但是现在,缺陷变得如此之小,我们不禁要问自己,光学方法是否具有足够高的灵敏度来检测这些随机缺陷,例如线的桥连或者孔的丢失?这仍然是悬而未决的问题。当然,对于尺寸较大的缺陷检测,光学技术毫无疑问是不二选择。”Peter De Bisschop 说道。

所以,我们仍然缺少一个可以做所有事情的方法,每种技术各有其优缺点。例如,对桥连的检测,光学方法相比CD-SEM,二者表现出不同——但互补——的作用范围。测量高密度缺陷时CD-SEM是很好的选择,将CD-SEM测量的数据外推几个量级,可以得到很合理的预测趋势(如下图)。同时,光学检测方法对细微尺寸的桥连缺陷的检测也有非常好的灵敏性。

机器学习的兴起

机器学习可以使现有设备更加高效。CD-SEM比SEM-Review慢得多,因为前者对每一个像素点都进行精细扫描,而后者则只是粗略扫描。“当然扫描速度越快,就会牺牲分辨力以及灵敏度。不过,我们正在尝试用机器学习——比如快速人脸识别技术——来提升对缺陷检测的高质量成像。如果行之有效的话,我们就可以大大加快电子束的扫描速度,wafer级别的扫描就不需要1000束电子了,100束足矣。”Philippe Leray说道。机器学习的另一个用途是制造过程的控制。在集成电路的制造过程中,一片晶圆会经过大量的设备,每一个步骤都由精细的参数来控制,以及原位检测。这个过程中则会产生大量的数据。比如,等离子体刻蚀深度的检测,我们需要观察等离子体的光谱,而图像和光谱包含的信息则远远不只是“缺陷”或者深度。Philippe Leray说:“我们的想法是,在整个集成电路制造以及测量过程中,收集所有的数据来‘训练’设备找出规律。设备对缺陷的理解是通过大量的数据,计算并推测出关键尺寸(critical dimension, CD),或者发现不好的刻蚀。即使这些数据细微复杂到人力无法识别。”

随机世界的认知

其实这些测量方法已经揭示了随机失效的概率和曝光尺寸的关系:随着尺寸的减小,失效概率几乎是指数式的增长,我们把这种关系叫做“随机悬崖”(stochastic cliff)。对于密集结构,有两种失效:随着线条距离和接触孔的尺寸的减小,线条的桥连或者接触孔的丢失两种缺陷则会急剧增长;而线条宽度或者接触孔的距离的减小,线条断裂或者接触孔的重叠两种缺陷会急剧增长。对于比较稀疏的结构,两种失效机理都存在,但只有线条断裂或者接触孔丢失或造成实际缺陷。随机悬崖不是唯一的问题。今年的SPIE先进光刻会议,IMEC首次向我们展示了他们的发现:(桥连)缺陷的数量永远不会减小到零,而是达到一个最小的常数,我们称之为瓶颈。这是一个很重要的发现,揭示了缺陷形成的另一种机理。

虽然这种瓶颈的机理暂未可知,但其后果是很严重的。能够制造的尺寸一定要远离随机悬崖,而且对于密集结构两个悬崖之间的无缺陷窗口会大大变小(见下图a)。这是业界需要解决的问题。瓶颈现象的发现,使得“即使是在无缺陷窗口,也并不表明就没有缺陷。”Peter De Bisschop解释道。

(a) 两种随机悬崖之间存在一个可能的无缺陷窗口

(b) 对于特定的L/S (line/space)桥连缺陷的数量不会减小到零

不仅仅是曝光剂量,光刻胶材料也是很重要的因素。IMEC在减少随机失效和线条糙度度方面取得了一些新的进展,他们通过顺序渗透分析(SIS)——一种常用于定向自组装(DSA)的现有技术——应用到EUV光刻技术上,在光刻胶里面掺杂无机元素使其更坚硬牢固,从而提高制作图形的质量。

“由于有众多参数需要调整,应该存在一个参数的‘最优设置’。不过可能性更大的是,没有一个参数设置可以完全解决问题。”Peter De Bisschop评论道,“基本上,我们希望在合理的时间内得到这些最优工艺参数。但很多设备有几百种可能的参数设定组合,人力难以做到。这显然是机器学习可以发挥的另一个领域。”Philippe Leray 道。

对失效的研究

对失效机理的理解可以更好的应对缺陷,了解工艺参数对失效概率的具体影响。EUV波长很短,高能光子轰击光刻胶,发生化学反应。对这些化学反应的研究可以有助于开发光刻胶以及底层吸收层。

IMEC和KM实验室近期开始合作深入研究EUV光刻技术的基础物理,使得在阿秒到皮秒级别研究EUV光子和光刻胶的化学反应成为可能。目前,暂无其他实验室有此实力。

EUV光子和光刻胶化学反应的研究对于减少随机失效至关重要

另一种揭露EUV光刻技术神秘面纱的方法是探测并量化光刻反应过程中有哪些分子被释放。光刻胶在吸收光子之后发生化学反应,光刻胶分子分解并形成新的化学键,另一部分物质不稳定从而逃逸。光刻胶上方的探测器可以探测到这部分逃逸分子并通过其质量分析其成分。这部分化学产物在曝光之前并不存在,因而他们的产生可以揭示光刻化学反应过程。另外,通过探测反应产物,可以了解曝光剂量或者光刻胶材料对光刻化学反应的影响。这样,我们可以将光刻光学反应对随机失效类型或者概率的利弊联系起来。

“当然,这些策略没有一个能完全揭示随机世界的面貌。但每一种方法都可以让我们对随机世界多一点了解,最后我们期望有一天,能完全了解随机世界的机理。”Peter De Bisschop总结道。

-

芯片

+关注

关注

453文章

50417浏览量

421853 -

EUV

+关注

关注

8文章

604浏览量

85968

发布评论请先 登录

相关推荐

HyperLith软件 EUV光刻交流

单片机图形化编程软件有哪些

降本增效取得新进展,拉普拉斯申请晶圆图形化工艺专利

AI大模型与小模型的优缺点

机器视觉控制的优缺点有哪些

fdm成型工艺的优缺点

日本大带宽服务器优缺点分析

STMCubeIDE使用CubeMX图形化配置USB后没有自动添加头文件路径是什么原因导致的?

Qt For OpenHarmony图形化的进展突破

【图形化编程】创客新手村,ESP32从零开始(1)水果小夜灯

EUV工艺不同多重图形化方案的优缺点及新的进展研究

EUV工艺不同多重图形化方案的优缺点及新的进展研究

评论