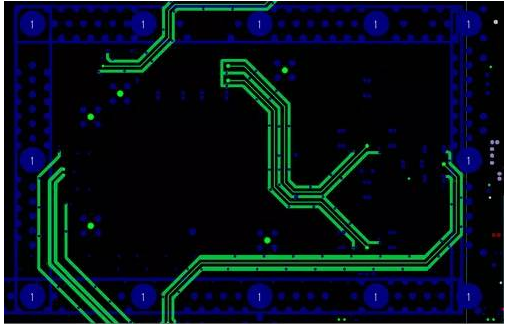

为什么在PCB设计中尽可能使用地平面?接地平面减小了信号返回路径的电感。反过来,这可以最大限度地减少瞬态接地电流产生的噪声。

在本文中,我们将讨论信号路径如何在多层PCB上工作以及返回路径电感的概念。

信号选择最小阻抗路径

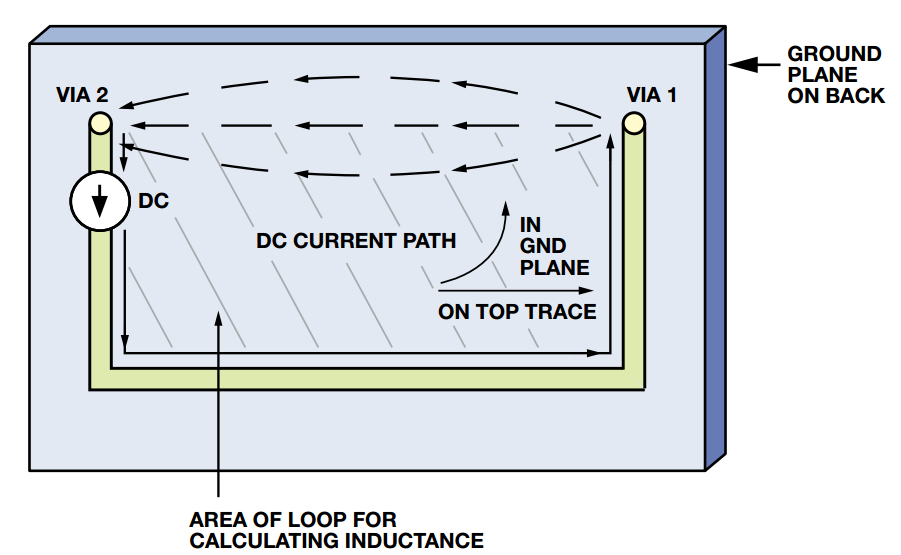

考虑一个双层电路板,如图1所示。底层是接地层,电流源是连接到顶层的U形迹线。顶层迹线通过VIA1和VIA2连接到底层。

首先,如图所示在图2中,DC电流注入顶层迹线。

图2。图片由ADI公司提供。

电流沿着U形迹线下降。然后,通过VIA1,它到达地平面。地平面的哪一部分将电流传回VIA2?我们可以将地平面设想为无限数量的并行的窄轨迹。电流将选择具有相对较小阻抗的迹线。由于从VIA1到VIA2的直接路径最短并且电阻最小,因此大部分电流将流过该路径。当我们离开这条阻力最小的路径时,电流密度会迅速下降。

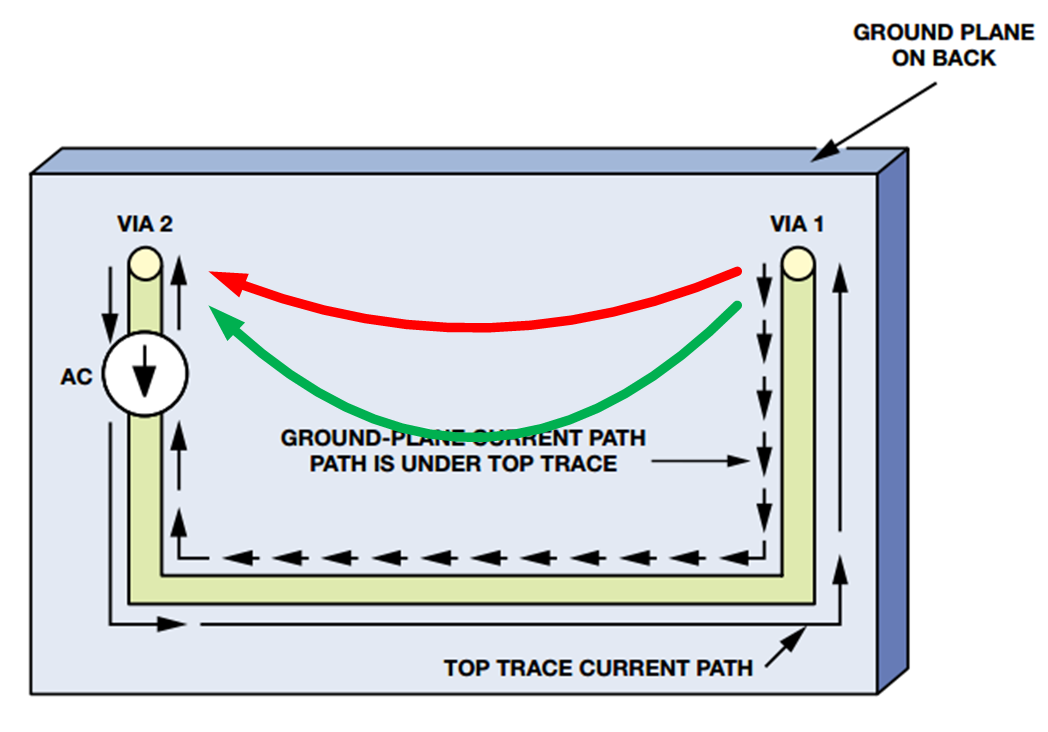

现在,我们假设我们将一个交流电流注入U形迹线。

它会不会采用相同的直流电流路径?

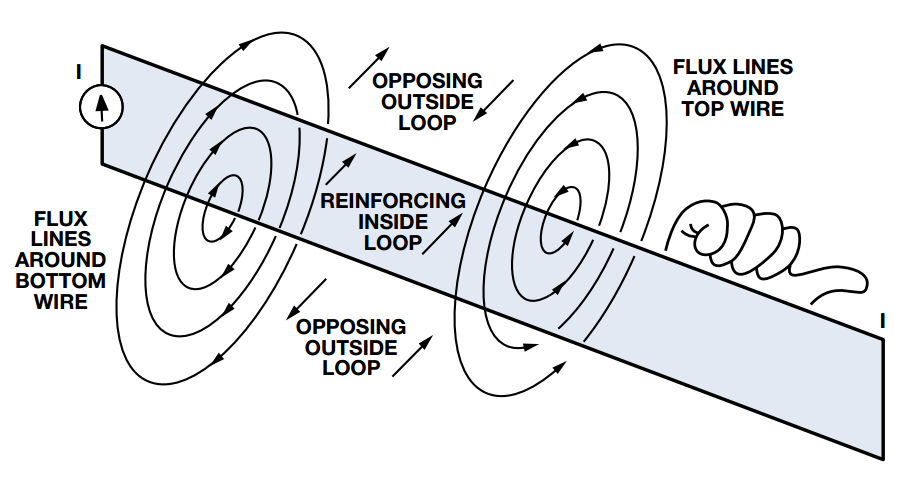

直流电流采用阻抗最小(或最小电阻)的路径。对于AC电流,阻抗取决于路径的电阻和电感。虽然最短路径提供最小电阻,但它不一定提供最小电感。路径的电感取决于电流产生的环路面积。图3显示了信号跟踪及其返回路径创建的示例电流环路。如果由电流产生的环路面积增加,则电感将按比例增加。

图3。图片由ADI公司提供。

例如,红色返回路径在图4中,创建了一个比绿色路径更大的循环。因此,在这两条路径之间,AC电流通过绿色路径,其具有较小的电感。对于路径的总阻抗,我们实际上应该考虑电阻和电感。然而,随着AC信号的频率增加,电感对路径阻抗的贡献最终变得大于电阻的数量级。因此,如图4所示,高频返回电流将直接在U形迹线下方流动,以最小化环路面积(为简单起见,我们忽略了路径电阻)。当我们在地平面上远离这条路径时,电流密度会迅速下降。

图4。图片由ADI公司提供

对于上面的例子,我们有一个可以设想为无限多个窄平行路径的地平面。返回电流流过那些使阻抗最小化的路径。使用双层电路板,我们买不起地平面。在这种情况下,我们可能有一条轨道(而不是一个平面)用于返回电流。即使电流可能表现出很大的电感,也要强制电流经过这条路径。对于双层电路板的一些关键信号走线(例如时钟信号),我们可以路由适当的返回路径,但我们不能对电路板上的所有走线执行此操作。我们如何降低双面电路板上所有走线的电流路径电感?我们将很快讨论双层电路板的高效接地系统,但在此之前,我们先简要介绍接地路径电感增加电路板噪声的机制。

为什么返回路径电感很重要?

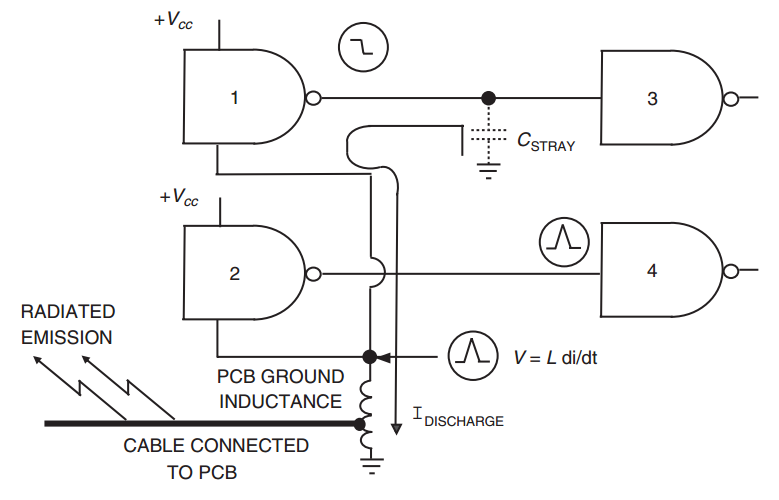

通过将电感器与电路原理图的接地串联,可以得到一个简单的返回路径电感模型。一个例子如图5所示。假设门1的输出从逻辑高变为逻辑低。这将通过接地路径释放存储在C STRAY 中的电荷。考虑到今天的快速逻辑门,放电将在很短的时间内完成(Δ t )。放电电流将流过接地电感。如果通过电感的电流在逻辑转换期间改变Δ I ,则逻辑门的地将反弹$ V = L \ frac {ΔI} {Δt} $$。/p>

在这种情况下,处于逻辑低电平的栅极输出(图4中的栅极2)将经历噪声电压脉冲。如果足够大,这个噪声电压可能会导致栅极4输出端产生不必要的转换。

此外,如图4所示,接地噪声电压可以耦合到离开PCB的电缆。作为天线,这些电缆会辐射并引起EMC问题。

图5显示了另一种有趣的机制,接地电感可能会导致问题。当栅极1的输出从逻辑高转变为逻辑低时,栅极1内的晶体管将杂散电容连接到由接地路径产生的电感器。如果连接CSTRAY和地电感的晶体管呈现小电阻,则会产生高Q串联谐振电路。这可能导致逻辑门转换具有相当大的振铃。如果我们不能充分降低接地电感,我们可能需要在栅极输出端串联一个电阻(例如51Ω)来抑制振铃。

图5.图片由电磁兼容工程提供。

上述噪声机制表明,在设计PCB时,接地路径电感至关重要。如前所述,多层板允许我们具有坚固的接地层,这可以显着降低接地电感。但是,对于双面电路板,我们必须采用其他技术来实现低电感接地系统。

-

pcb

+关注

关注

4322文章

23128浏览量

398620 -

PCB设计

+关注

关注

394文章

4692浏览量

85883 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

43090

发布评论请先 登录

相关推荐

如何降低温度和湿度对高频高速PCB板材介电常数的影响?

场效应管驱动电路设计 如何降低场效应管的噪声

怎样准确合理测试单板上DAC80504输入的系统噪声?

哪些措施能降低电机的噪声?

电源滤波器是如何降低电源噪声的

求助,关于运算放大器反馈电路PCB布局请教

降低PCB热阻的设计方法有哪些

如何降低DC-DC转换器的纹波噪声

采用电容器来降低噪声的方法

EMC之PCB设计技巧

PCB噪声怎样做可以较好的降低

PCB噪声怎样做可以较好的降低

评论