在上一篇文章中,我们探讨了是否连接电容器的问题通过走线或通过一对过孔将电容去耦到IC电源引脚。我们看到通孔技术是优越的,因为它降低了电感,当我们试图确保去耦电容在50-100 MHz的频率下有效时,电感是我们必须克服的主要障碍。高达数百兆赫。

过孔和平面

在本文中,我们将探讨去耦电感的问题。通孔和平面层配置。然而,在我们进入讨论之前,我们需要明确以下几点:随着我们深入探讨高速去耦领域,我们越来越关注平面连接,直到最终看起来很大程度上忽略了跟踪。以下注意事项将有助于将此现象置于语境中:

高电感

正如我们在上一篇文章中所看到的,与连接相比,迹线仅具有过多的电感依赖于过孔和平面层。

平面电容

去耦电容与平面相互作用的方式似乎成为主导因素随着运行频率的增加。科学在这里开始变得复杂,我理解细节的能力有限,甚至解释它们的能力也越来越差。我在本文中发现的一个有趣和直接的陈述表明,在某些情况下,去耦电容本身受到电感的阻碍,以至于它无法真正为IC提供电流。相反,平面电容提供瞬态去耦电流,电容器的工作是为平面充电。

拥挤的布局

高速数字系统通常涉及复杂的空间受限布局,这些布局将大部分PCB空间专用于组件。几乎没有迹线的空间,因此电路板设计师很乐意尽可能使用过孔。

分布式电容与离散电容

如果平面电容是在某些高速数字设计中真正的去耦电荷源,电容真的需要“尽可能靠近引脚”吗?位置是否重要?质疑正确解耦的基本原则之一的有效性似乎令人震惊,但这正是Hubing等人的观点。在这篇研究论文中做过。用另一篇论文的作者的话来说,Hubing等。声称在某些条件下电容器的位置“不重要”,尽管它们可能已将其结论扩展到“研究的有效性范围之外”。无论如何,这是电容器之间相互作用重要性的另一个例子。在平板上到处都有“分布电容”的平面层。

最小化电感

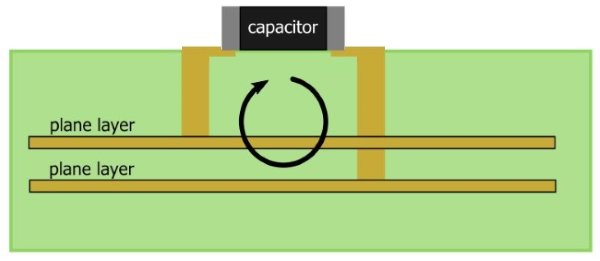

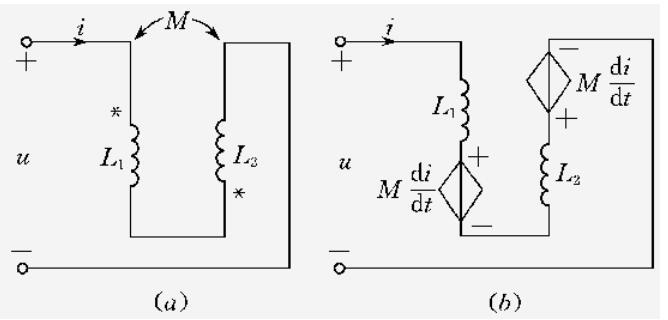

去耦电容的总电感取决于由电容,过孔和平面形成的电流环的面积。

如您所见,环路区域受两个过孔之间的间隔以及电容器与平面层之间的距离的影响。因此,如果目标是改善去耦性能,那么到平面和通过分离的距离是需要解决的关键因素。

与飞机的距离

如果您正在设计一个典型的四层板,那么您可以做的就是减少与飞机的距离 - 去耦帽将始终接近一个平面层并且远离另一个平面层。

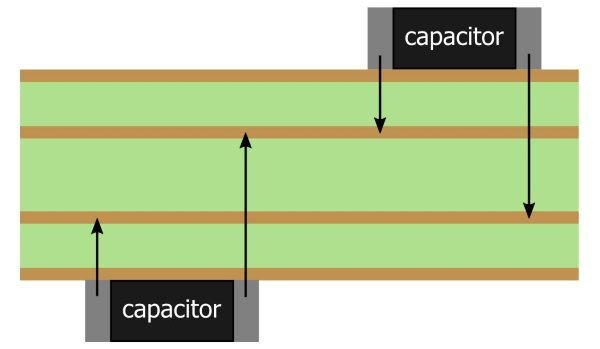

如果但是,电路板有四层以上,您可以灵活地优化去耦电容相对于电源和接地层的位置。此外,现在是指出如果不将电源和接地层放置在相邻层上,将会损失大量分布电容的好时机。在我看来,高速数字设计将从以下配置中受益匪浅:

在两个组件层之一上放置尽可能多的高速IC(让我们说它是顶部)。

布置电源和接地层,使它们相邻并靠近顶层。

将所有去耦帽放在顶层,使它们具有短连接

通过分离

减少通孔分离的第一种方法是使用较小的去耦电容。在我的电路板上,我使用0603封装,因为我经常手工组装它们;如果电路板由机器组装,0402是更好的选择。

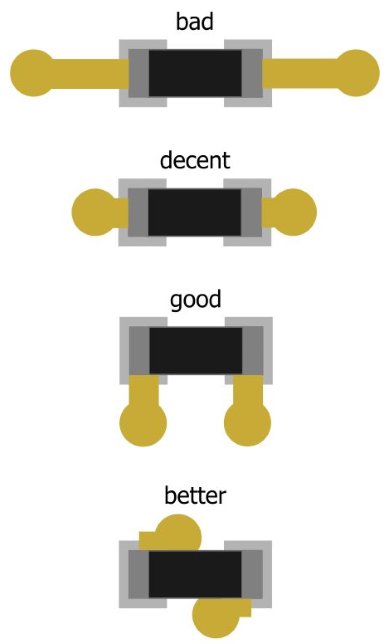

现在最小化电感是选择最佳通孔配置的问题:

改编自 本文件第29页的图表 。

请注意,我们主要关注两个过孔之间的距离。因此,第三个图表标记为“良好”,第二个图表标记为“正常”,尽管“体面”配置使用较短的走线将电容器端子连接到过孔。

结论

我希望本文能让您深入了解高速数字PCB设计的复杂世界。我认为很明显,最小化环路面积是降低电感并因此改善高频性能的关键,但我不确定如何考虑在整个电路板上随机分配去耦电容的可能性(在某些情况下)。如果您对此主题有任何想法,请随时在评论中分享。

-

电容器

+关注

关注

64文章

6215浏览量

99517 -

电感

+关注

关注

54文章

6134浏览量

102273 -

去耦

+关注

关注

2文章

50浏览量

18271

发布评论请先 登录

相关推荐

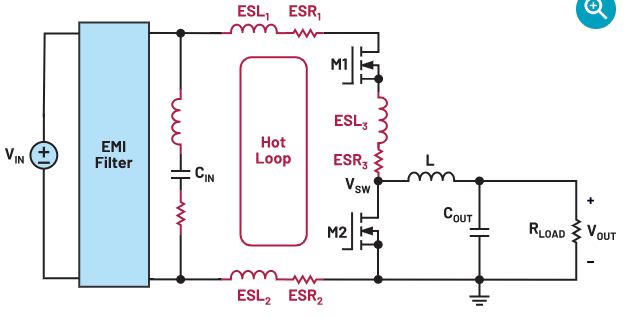

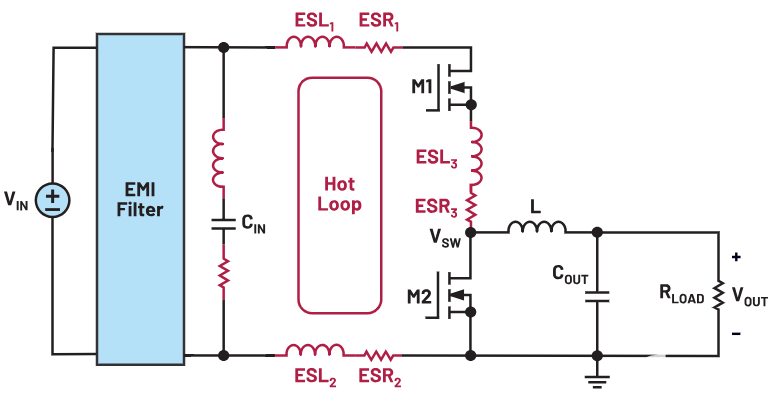

如何通过最小化热回路PCB ESR和ESL来优化开关电源布局

PCB布局提示和技巧:最小化去耦电感

vrf设置程序窗口最小化

基于带权核范数最小化的去噪模型

如何通过最小化热回路来优化开关电源布局?

如何通过最小化热回路PCB ESR和ESL来优化开关电源布局

如何通过最小化热回路来优化开关电源布局?

最小化去耦电感有哪些技巧

最小化去耦电感有哪些技巧

评论