高密度互连或HDI基板是多层,高密度电路,具有细线和明确定义的空间图案等特征。越来越多的HDI基板的采用增强了PCB的整体功能并限制了操作区域。

将HDI板与其他类型板区分开来的关键因素之一是其独特的设计,其中包括多层铜填充微通孔。这些多层微通孔实现了垂直互连。此外,高密度互连(HDI)基板提供的优点包括更高的集成度和更好的两侧元件放置。此外,HDI板由较小数量的I/O组成。高密度互连(HDI)基板的其他功能包括更快的信号传输和显着减少信号损失和交叉延迟。

最近采用的HDI板制备技术涉及组件的小型化并采用高端设备。但是,串扰等挑战会对HDI板的性能产生不同的影响。因此,避免HDI电路板中的串扰变得至关重要。

HDI电路板中的串扰生成

无意识迹线和组件之间的电磁耦合被定义为电子电路中的串扰。此外,由于外部干扰,电磁场干扰可能发生在PCB中。串扰会产生不良影响,影响时钟,周期信号,系统关键网络,如数据线,控制信号和I/O.此外,受影响的时钟和周期性信号会对工作PCB和组件组件产生严重的功能影响。串扰导致电容和电感耦合。 HDI基板中的电容耦合发生在其中一条迹线位于另一条迹线上时。

避免串扰的方法

HDI基板中的串扰因较短而减少耦合长度和较低介电常数高达50%。可以限制HDI基板中串扰的其他因素包括,

使用较低的Dk材料。

HDI材料系统的较低介电常数可使电路板收缩至28%。

距离越短对于参考平面,近端串扰将越低。

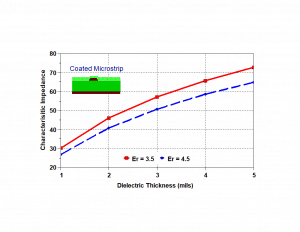

HDI小型化提供更短的互连长度,如果使用更低介电常数材料,则HDI基板中的串扰减少。Eric Bogatin,Teledyne Lecroy的信号完整性宣传员提供了以下示例:“HDI技术中的典型线宽为3密耳(75微米)。下图显示了各种介电厚度下3密耳宽迹线的特征阻抗。

介电常数较低时,介电厚度较小。这意味着较低介电常数的材料系统可以在相同的间距下产生更少的串扰,或者迹线可以更靠近在一起并具有相同的串扰量。“

介电厚度与受控阻抗

案例研究

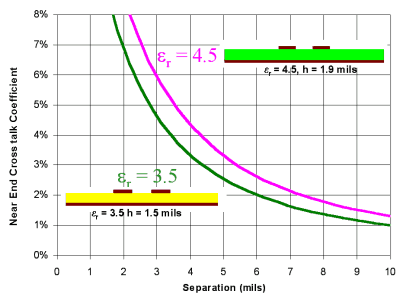

Eric Bogation继续说道,“在研究了两种情况,线宽为3密耳,并调整了介电厚度,使得对于两种不同的介电常数,线阻抗是相同的。从这些曲线可以看出,如果布线间距受串扰约束,则HDI材料系统的较低介电常数可能使电路板缩小至28%。

对于耦合长度小于饱和长度,近端电压噪声的大小将随着长度而变化。饱和长度取决于上升时间。对于1纳秒的上升时间,有效介电常数为2.5的饱和长度约为7.6英寸,这将包括小卡应用中的许多迹线。相对耦合的近端噪声将由下式给出:

近端串扰系数

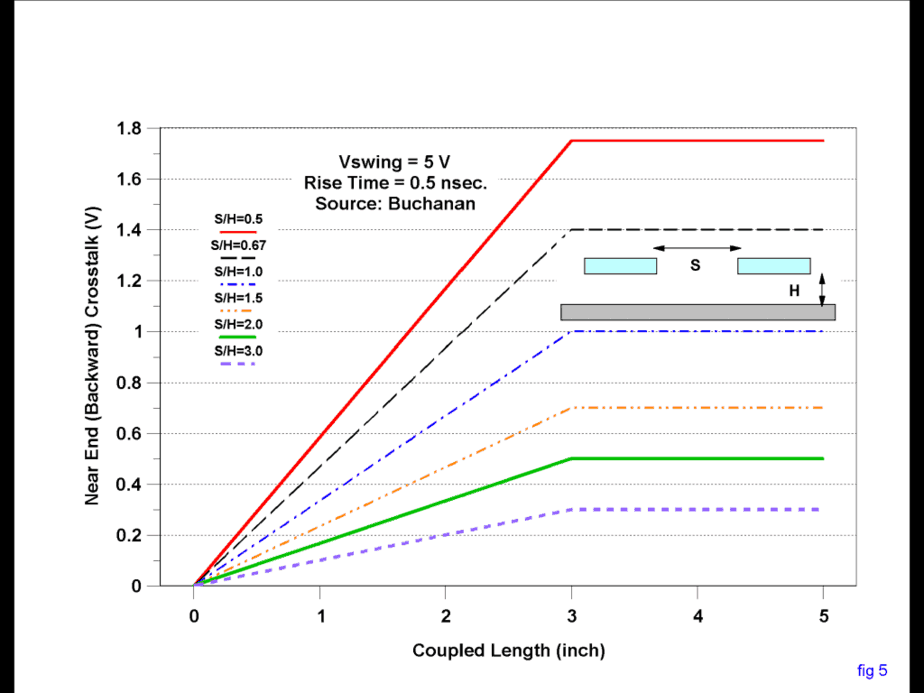

HDI基板中的串扰减少了较短的耦合长度和较低的介电常数可达50%。较短的走线长度将辐射较少,而具有较薄电介质的走线将辐射较少。下面的例子表明,耦合长度越短,互感(Lm)越小,走线越薄,互电容(Cm)越小。

耦合长度

此外,距参考平面的距离越近,近端串扰越小,或者耦合长度越长,串扰越小。与传统电路板相比,长度减少2倍,电介质厚度减少2倍,HDI信号环路的辐射场可能会减少4倍,即12 dB。“

Eric Bogatin进一步指出,“如果整个电路板都是HDI,而不仅仅是几个外层,那么控制返回路径可能比通孔电路板更具挑战性。”

Eric Bogatin的关键要点:

”你必须注意HDI基板中的相同问题:

提供连续的返回路径。

工程控制的阻抗互连。

在具有最小存根长度的线性菊花链路径中进行路由。

使用终端管理反射噪声。

通过返回路径控制来控制通过串扰。

使用连接到IC引脚的低电感电容。

与通孔核心相结合,HDI互连非常有价值。“

信号完整性挑战和结论

我们非常熟悉信号完整性及其在确定高速PCB设计性能中的作用。串扰是影响信号完整性的关键参数之一。串扰可能直接导致接收器信号失真。因此,设计人员最关心的是将HDI基板中串扰的影响降至最低。

不要在自己之间串扰,向我们询问任何问题。我们在这里等你。

-

HDI

+关注

关注

7文章

227浏览量

22801 -

串扰

+关注

关注

4文章

196浏览量

27874 -

可制造性设计

+关注

关注

10文章

2066浏览量

16517 -

华秋DFM

+关注

关注

20文章

3516浏览量

6533

发布评论请先 登录

PCB设计中避免串扰的方法

PCB设计中,如何避免串扰

PCB设计中,如何避免串扰

PCB设计中串扰的产生以及如何避免

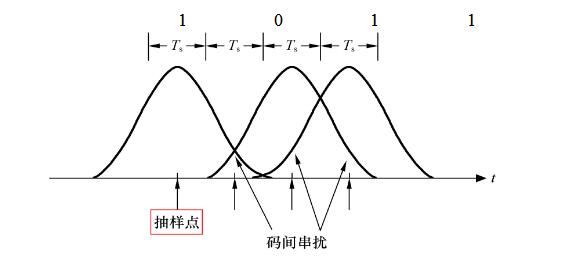

如何消除码间串扰_怎么避免码间串扰

HDI基板中的串扰怎么避免

HDI基板中的串扰怎么避免

评论