简介

时钟抖动性能主题似乎是时钟,ADC和电源的当前焦点供应厂家。理由很清楚;时钟抖动会干扰包括高速ADC在内的数字电路的性能。高速时钟可以对它们所接收的功率的“清洁度”非常敏感,尽管量化关系需要一些努力。

许多电压调节器制造商正在开发新的稳压器产品线(主要是LDO),这些产品可以提供更高的PSRR,专门用于为精密时钟和敏感电路供电。最近有文章表明,当用开关稳压器代替线性稳压器时,时钟和随后的高速ADC的性能是完全可以接受的。[i]

用于测量时钟相位噪声的测试装置和抖动如图1所示:

图1 - 测量时钟相位噪声和抖动的设置。

时钟的噪声路径

时钟抖动Tj,和电源噪声,Nv,可由公式1定义。

这种关系清楚地表明需要根据频率确定时钟抖动对电源噪声的灵敏度。理解感兴趣的频率范围也很重要,这通常会延伸到ADC工作的最高信号频率。并非所有时钟都相似,一些较新的,性能更高的时钟具有内置的高性能线性稳压器,锁相环(PLL)和抖动清除器,以降低时钟性能对电源噪声的灵敏度。

定义电源噪声至少需要三个项,但也可能有几个不太明显的路径。

公式2中的关系显示了到时钟的三条主要噪声路径。第一个是线性稳压器输入端产生的噪声,它通过稳压器的电源抑制比(“PSRR”)降低。这说明了为什么这么多制造商正致力于改善下一代LDO的高频PSRR。第二条噪声路径是从稳压器的内部噪声到稳压器输出。第三个且不常讨论的路径是由于线性调节器输出端的电流变化与调节器输出端的阻抗相互作用,调节器输出端也是时钟的输入功率。如果其他动态负载连接到同一个稳压器,这一点尤其重要。

与测量时钟性能相关的一个更复杂的问题是确定和然后给出具有适当噪声电压和电流的时钟。这是最近发表的一些关于该主题的文章的主要缺点[i]。

本文将展示这些噪声路径的影响和敏感性,并提供一些精简的一般指导原则。优化时钟性能的功率要求。

测量噪声

示例在本文中我们使用的是低成本,现成的3.3V,125MHz CMOS SMD时钟。该频率足够低,相当普通并且相对便宜,同时提供足够高的灵敏度以使其变得有趣。由于CMOS振荡器设计为15pF负载,因此使用10X示波器探头和Picotest J2180A宽带前置放大器将高阻抗探头转换为我们用于测量时钟噪声的Agilent N9020A信号分析仪的50 Ohm输入。由于它的普及,我们使用LM317线性稳压器,以及定制设计的电压调节器,为测试时钟提供电源。 Picotest电压调节器测试标准或“VRTS”套件用作测试台,因为它提供与输入和输出的简单连接,以及支持可互换的线性调节器以进行比较测量。

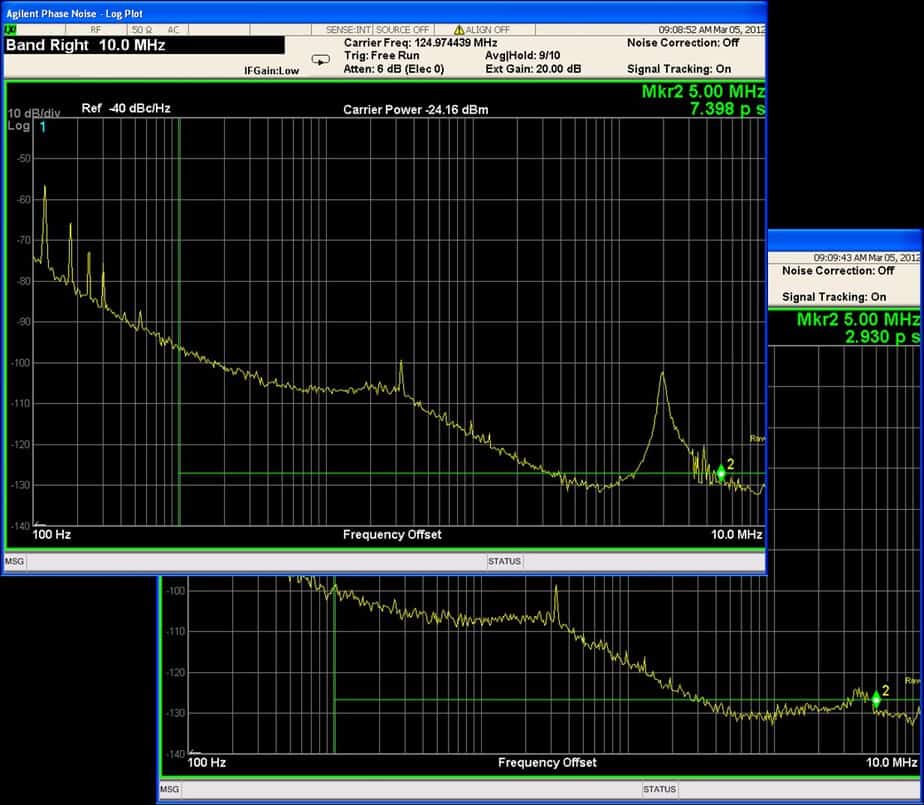

图2 - 开关墙适配器用于为线性稳压器提供电源,然后为时钟提供电源。 LM317产生7.4pS抖动(上图),而定制稳压器产生2.9pS抖动。

图2中LM317的大2MHz信号应该到期调节器的控制回路和墙上适配器的阻抗,包括其输出线和连接器的阻抗。定制设计的稳压器在2MHz时提供50dB PSRR,以及更高的带宽,可抑制大部分输入噪声信号。

使用连接到VRTS板的台式电源更换墙式适配器,使用通用的18“香蕉测试引线,显着降低了时钟的性能,如图3所示。而测试引线和墙上适配器都大致测量1uH的电感,工作台电源阻抗和测试引线导致更高的Q值(实际上,正如2MHz信号及其谐波的出现所示,振荡)。在稳压器输入端增加一个0.47uF陶瓷电容可大大降低2MHz时的输入阻抗。产生的抖动降低到2.8pS。

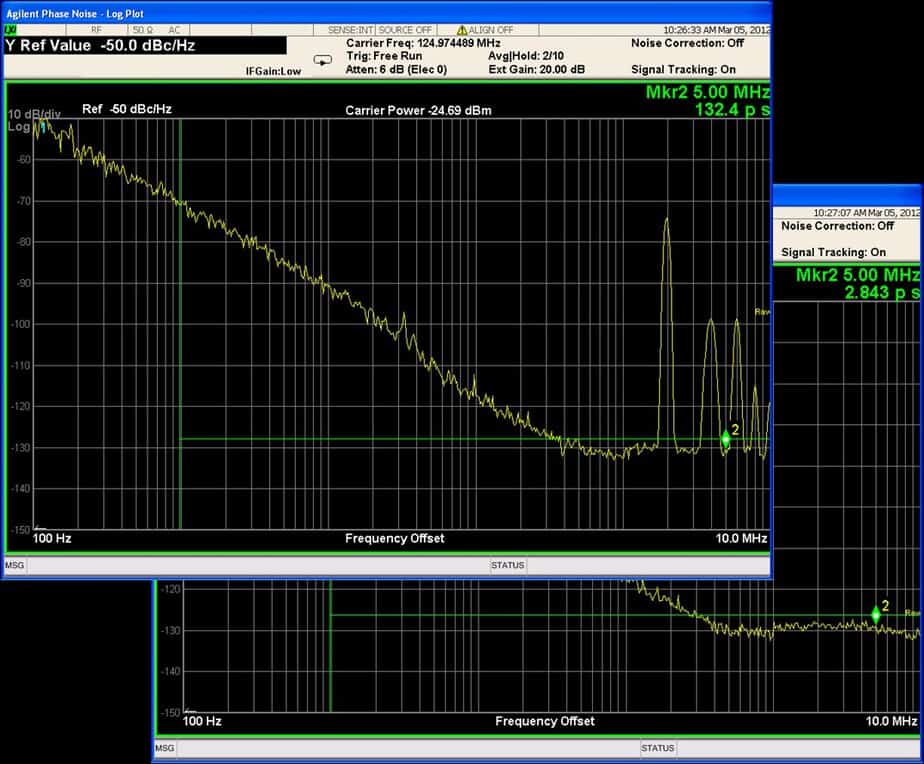

图3 - 连接到LM317线性稳压器的台式电源(使用香蕉测试引线)然后连接到时钟。线性稳压器输入端没有电容(顶部),抖动为132pS,稳压器输入端为0.47uF陶瓷电容,抖动降至2.8pS(底部)。

使用工作台电源和输入电容去耦替换墙上适配器大大减少了时钟抖动。为了证明时钟对电源电路输入和输出阻抗的灵敏度,Picotest J2111A电流注入器用于提供窄电流脉冲,可以连接到线性稳压器的输入或输出,提供外部瞬态刺激。窄脉冲富含谐波。

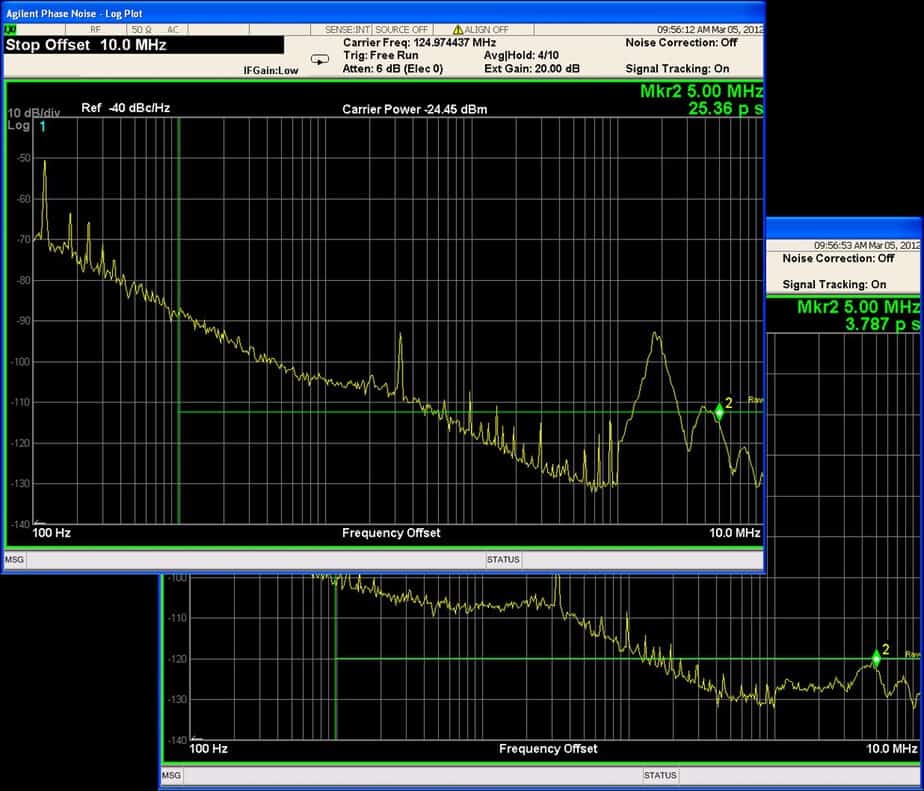

在图4中,J2111A电流脉冲连接到线性稳压器的输入。墙上适配器的有限阻抗将电流信号转换为电压频谱,然后电压通过PSRR通过线性稳压器并传输到时钟,产生抖动。电容器的增加降低了阻抗,从而降低了时钟的噪声电压。重要的是要确保电容器不与可能导致高Q谐振的电感器,磁珠或其他电路电抗共振,这会增加时钟的噪声水平。

图4 - 壁式适配器为LM317供电,增加一个30mA 150kHz 5%占空比电流脉冲,在稳压器输入端连接(底部),无(顶部)增加一个0.47uF稳压器输入电容

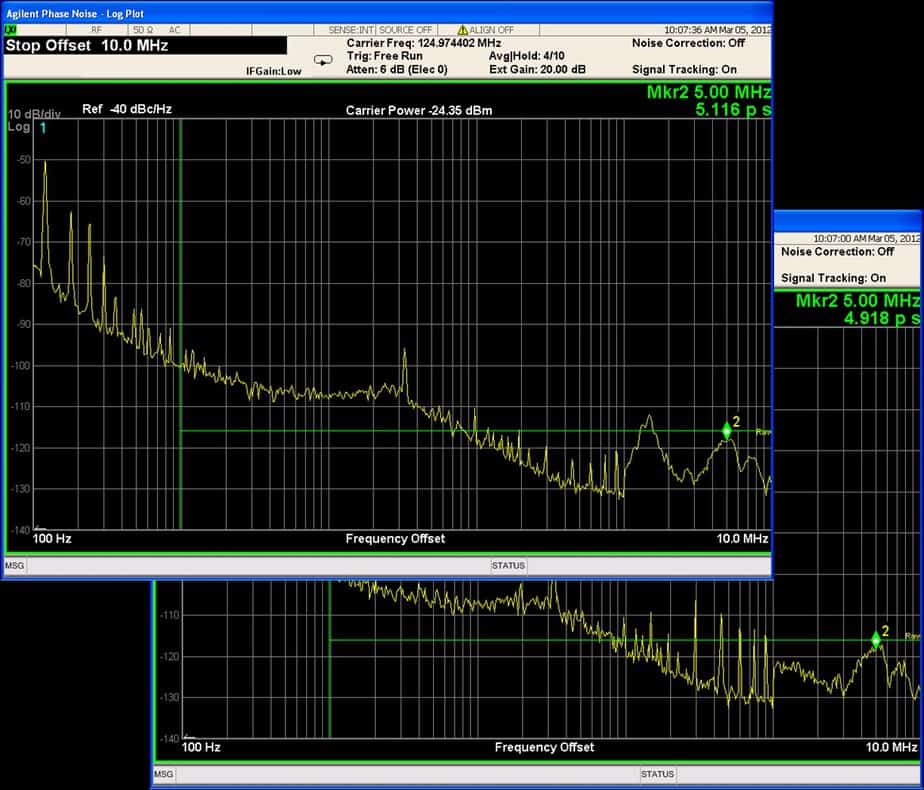

在图5中,来自J2111A电流注入器的电流脉冲连接到线性稳压器的输出端,再次有限稳压器阻抗变压器将此电流转换为噪声电压然后传递给时钟添加抖动。从图5中可以看出,高带宽定制调节器具有低于1MHz的低阻抗,这可以通过更大的降低的杂散幅度来证明,而高带宽调节器也会在1.5MHz附近显示谐振,这会导致抖动,并且两个调节器都会产生共振接近5MHz,导致抖动。

图5 - J2111A电流注入器用于在稳压器输出端提供30mA 150kHz 5%占空比电流脉冲LM317(顶部)和定制设计的线性稳压器(底部)。

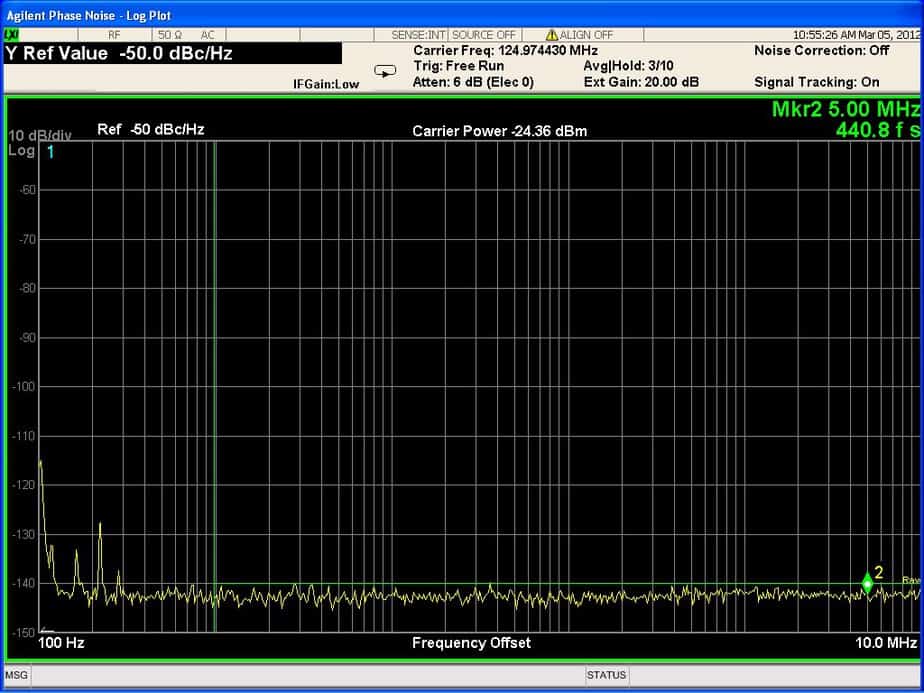

为了确保有效性并确定测量限制,显示的平均噪声水平( DANL)如图6所示。本底噪声约为-143 dBc,相应的抖动为441f S。

图6显示测量设置的平均噪音水平(DANL)。

我们通过简单的测量表明,时钟抖动对时钟电源端子上的噪声电平很敏感。我们还证明了稳压器输入和输出端的有限非零阻抗电平可以极大地促成外部激励导致的时钟抖动。虽然线性稳压器的PSRR是时钟抖动灵敏度的关键术语,但还需要考虑所有其他术语。

为时钟或LNA供电的一些基本设计指南是:

最小化稳压器输入和输出时钟的阻抗。这样可以最大限度地降低对外部信号的敏感度。

最大化稳压器的PSRR,以便尽可能地衰减输入信号。

确保阻抗中没有相位不连续(高Q谐振) )在调节器输入或输出处。这些阻抗应始终在整个感兴趣的频率范围内进行测量。

使用RF磁珠将振荡器与外部噪声隔离时要小心。珠子可以是非常诱导的并且可以导致相位不连续,这可能适得其反。虽然磁珠会衰减来自稳压器的噪声,但它也会增加阻抗,使得时钟更容易受到负载电流引起的抖动的影响。

最后,不要操作任何其他动态设备。与时钟相同的调节器。与时钟调节器共用一个公共输入的任何其他稳压器的稳定性或相位不连续性可能导致串扰引入另一条时钟抖动路径。

-

电源

+关注

关注

185文章

18992浏览量

264608 -

时钟

+关注

关注

11文章

2000浏览量

135248 -

相位噪声

+关注

关注

2文章

198浏览量

23807

发布评论请先 登录

减少相位噪声和抖动对系统对性能影响的方法介绍

测量较低时钟频率的相位噪声和相位抖动资料下载

相位噪声处理:时钟抖动或结束时钟抖动的最佳方法是什么?资料下载

时钟抖动性能和相位噪声测量

时钟抖动性能和相位噪声测量

评论