数字信号(包括串口和 GPIO 口)的走线注意事项如下:

1. 数字信号应尽量远离晶体和 RF 走线。

2. 数字信号应尽可能用地围起来,以减少相互串扰。

3. 在布线不合理或走线太长情况下,串口 CSB,FCSB,SDIO,SCLK 管脚容易受到干扰,功率输出(20dBm)越大,工作频率越低,受干扰的概率越大。

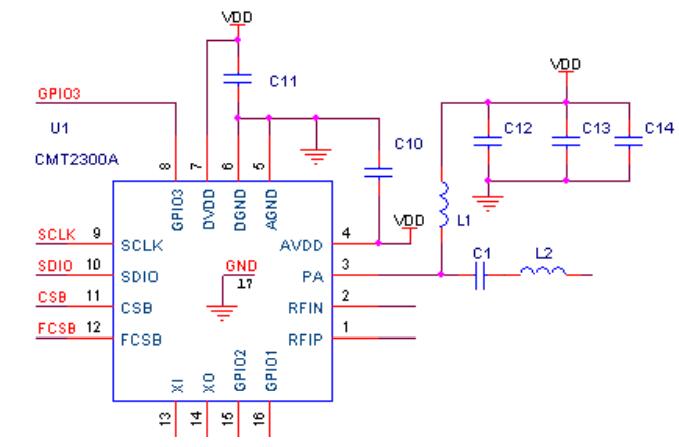

为了减轻电源上的噪声纹波对芯片的影响,及 PA 输出对电源的影响,用户应当在以下几处设计滤波电容。

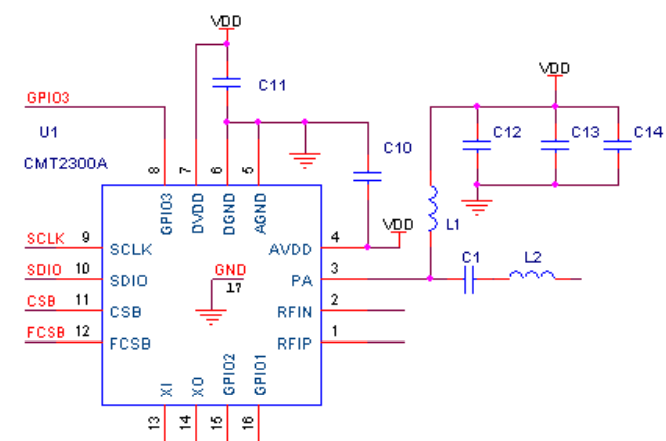

1. C10 靠近芯片的 AVDD 管脚处。

2. C11 靠近芯片的 DVDD 管脚处。

3. C12, C13 靠近扼流电感, 建议 C13 保留以应对高次谐波。

4. C14 根据 PA 输出功率和供电电路性能,推荐值 4.7 - 10uF。

铺地设计

说明如下:

1. 参考地层:射频走线需要在相邻层有大片的连续地做参考平面,以实现高效的功率输出和最佳接收灵敏度。

2. 射频走线两侧包地并打过孔到参考地平面以减小杂散辐射。

3. 各层地网络打过孔到参考地层,减小回路路径,从而使回路的辐射减少。

4. 线路板边沿尽量铺地,且过孔间距不超过 λ/10,从而减小辐射和增强抗 ESD 能力。

5. IC 衬底一定要有几个过孔到地层,有利于提升芯片的射频性能指标。

6. 晶体电路对干扰敏感,用包地隔离。

-

芯片

+关注

关注

455文章

50812浏览量

423587 -

滤波电路

+关注

关注

46文章

636浏览量

69670 -

GPIO

+关注

关注

16文章

1204浏览量

52093

发布评论请先 登录

相关推荐

CMT2300A无线数据收发模块资料

电源地 信号地 模拟地 数字地 射频的分析与布局

为什么说CMT2300A是Sub-1GHz超低功耗的射频收发器

超低功耗Sub-1GHz性价比首选方案:CMT2300

超低功耗Sub-1GHz性价比首选方案:CMT2300

DSP芯片外围电路典型设计(数字信号处理器芯片TMS320F

CMT2300A 超低功耗Sub-1GHz射频收发器的详细中文资料免费下载

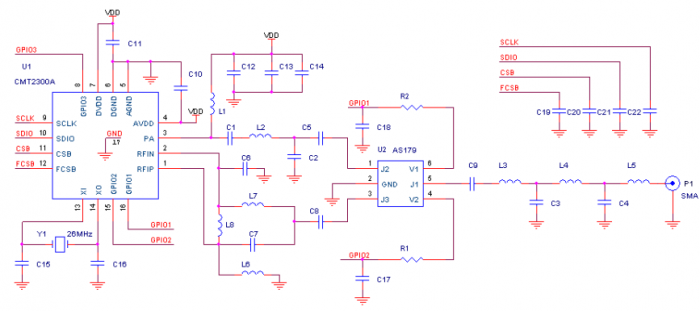

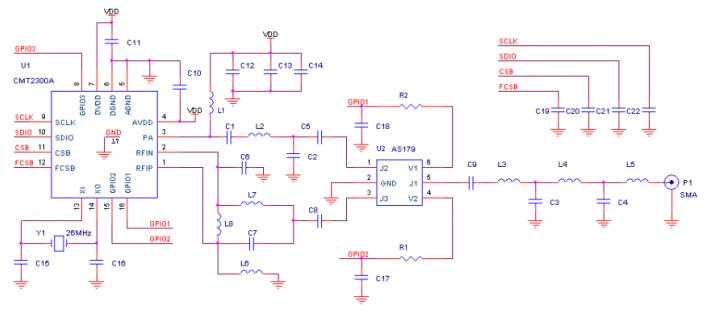

使用CMT2300A芯片设计开关射频匹配网络电路的详细概述

CMT2300A的开关射频匹配网络电路设计

CMT2300A 433MHz无线收发芯片

使用CMT2300A芯片设计射频匹配网络的数字信号和电源滤波电路与铺地

使用CMT2300A芯片设计射频匹配网络的数字信号和电源滤波电路与铺地

评论