声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

pcb

+关注

关注

4336文章

23275浏览量

402696 -

视频

+关注

关注

6文章

1964浏览量

73356

发布评论请先 登录

相关推荐

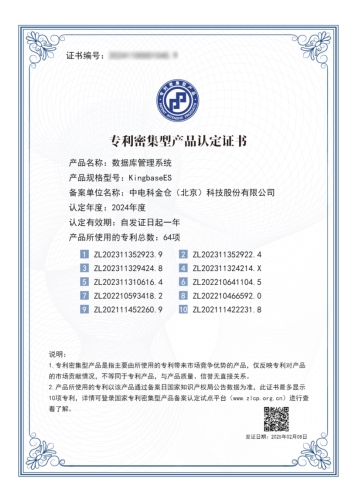

金仓数据库入选《2024年度专利密集型产品名单》

2月8日, 国家专利密集型产品备案认定试点平台公布了《2024年度专利密集型产品名单》,由电科金仓自主研发的金仓数据库管理系统(KingbaseES)凭借扎实的技术积淀与市场验证,成功入选该名

时序约束一主时钟与生成时钟

的输出,对于Ultrascale和Ultrascale+系列的器件,定时器会自动地接入到GT的输出。 1.2 约束设置格式 主时钟约束使用命令create_clock进行创建,进入Timing

人员定位系统对生产密集型企业的重要意义

发电、供电、石油化工、钢铁冶金行业为生产设备密集型企业,生产现场错综复杂,稍有不慎便会发生危险;建筑工地现场施工作业中,存在着人员流动性大、现场状况杂乱、安全隐患难以察觉等问题;工厂安全管理

广和通端侧AI解决方案驱动性能密集型场景商用型场景商用

2024世界机器人大会期间,广和通宣布:基于高通QCS8550平台的广和通端侧AI解决方案高效使能性能密集型场景。该端侧AI解决方案整合强大AI算力、边缘侧AI数据分析及Wi-Fi 7连接方式,可为自主移动机器人、工业无人机、云服务器和AI边缘计算盒子等物联网应用提供端侧AI部署能力。

PCB设计与PCB制板的紧密关系

。以下是它们之间的关系: PCB设计与PCB制板的关系 1. PCB设计: PCB设计是指在电子产品开发过程中,设计工程师使用专业的电子设计软件创建

Cadence快板PCB培训

Allegro环境介绍Allegro环境设定 焊盘制作 元件封装制作 电路板创建PCB叠层设置和网表导入 约束规则管理布局 布线 覆铜PCB设计

发表于 07-02 17:22

•0次下载

Xilinx FPGA编程技巧之常用时序约束详解

今天给大侠带来Xilinx FPGA编程技巧之常用时序约束详解,话不多说,上货。

基本的约束方法

为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。最普遍的三种路径以及异常路径为

发表于 05-06 15:51

时序约束实操

添加约束的目的是为了告诉FPGA你的设计指标及运行情况。在上面的生成约束之后,在Result àxx.sdc中提供约束参考(请注意该文件不能直接添加到工程中,需要热复制到别的指定目录或者新建自己的SDC文件添加到工程)。

Xilinx FPGA的约束设置基础

LOC约束是FPGA设计中最基本的布局约束和综合约束,能够定义基本设计单元在FPGA芯片中的位置,可实现绝对定位、范围定位以及区域定位。

发表于 04-26 17:05

•1533次阅读

Xilinx FPGA编程技巧之常用时序约束详解

今天给大侠带来Xilinx FPGA编程技巧之常用时序约束详解,话不多说,上货。

基本的约束方法为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。最普遍的三种路径以及异常路径为

发表于 04-12 17:39

鸿蒙OS开发实例:【ArkTS类库多线程CPU密集型任务TaskPool】

CPU密集型任务是指需要占用系统资源处理大量计算能力的任务,需要长时间运行,这段时间会阻塞线程其它事件的处理,不适宜放在主线程进行。例如图像处理、视频编码、数据分析等。

基于多线程并发机制处理CPU密集型任务可以提高CPU利用率,提升应用程序响应速度。

鸿蒙OS开发实例:【ArkTS类库多线程I/O密集型任务开发】

使用异步并发可以解决单次I/O任务阻塞的问题,但是如果遇到I/O密集型任务,同样会阻塞线程中其它任务的执行,这时需要使用多线程并发能力来进行解决。

I/O密集型任务的性能重点通常不在于CPU

博泰“车联网云服务平台”入选2023年度专利密集型产品名单

近日,中国专利保护协会首次组织开展了专利密集型产品认定工作,并于近期发布2023年专利密集型产品名单,博泰的“车联网云服务平台”入选2023年度专利密集型产品名单。

如何创建和管理约束密集型、高度约束的PCB设计

如何创建和管理约束密集型、高度约束的PCB设计

评论