声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

pcb

+关注

关注

4319文章

23080浏览量

397496 -

设计

+关注

关注

4文章

818浏览量

69888 -

PADS

+关注

关注

80文章

808浏览量

107776

发布评论请先 登录

相关推荐

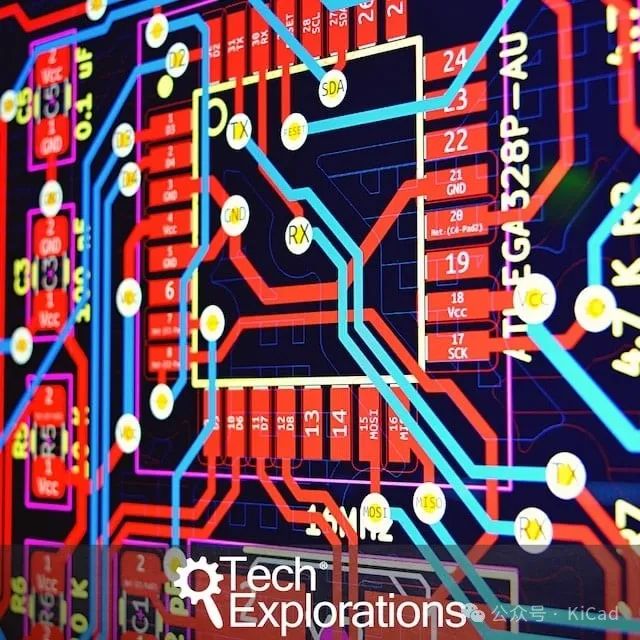

和 Dr Peter 一起学 KiCad 4.3:轮廓与约束 (Edge cut板框)

“ 在本节中,您将学会如何绘制 PCB 的板框。 ” 4 .3. 2- 轮廓与约束 (Edge cut板框) 在本章中,我们将完成在本书第三部分第二章中学到的 PCB 工作流程的第二步。在这

时序约束一主时钟与生成时钟

的输出,对于Ultrascale和Ultrascale+系列的器件,定时器会自动地接入到GT的输出。 1.2 约束设置格式 主时钟约束使用命令create_clock进行创建,进入Timing

常用时序约束使用说明-v1

为了防止约束失败,我们在Tcl输入框中验证,没有告警或者错误说明约束的写法是正确的set_max_delay 5.00 -from [get_cells key2_detect_inst/state

电路的两类约束指的是哪两类

包括欧姆定律、基尔霍夫定律、电容和电感的特性等。电气约束确保电路在正常工作状态下,能够按照预期的方式运行。 电气约束的特点 (1)普遍性:电气约束适用于所有电路系统,无论是简单的电阻电

PCB设计与PCB制板的紧密关系

。以下是它们之间的关系: PCB设计与PCB制板的关系 1. PCB设计: PCB设计是指在电子产品开发过程中,设计工程师使用专业的电子设计软件创建

两种SR锁存器的约束条件

基本约束条件: SR锁存器是一种基本的数字逻辑电路,用于存储一位二进制信息。它有两个输入端:S(Set)和R(Reset),以及两个输出端:Q和Q'(Q的反相)。以下是SR锁存器的基本约束

Cadence快板PCB培训

Allegro环境介绍Allegro环境设定 焊盘制作 元件封装制作 电路板创建PCB叠层设置和网表导入 约束规则管理布局 布线 覆铜PCB设计

发表于 07-02 17:22

•0次下载

PCB设计的EMC有哪些注意事项

是否满足ESD或者EMI防护设计要求,撇开原理图设计,PCB设计一般需要我们从PCB布局和PCB布线两个方面进行审查,接下来为大家介绍关于PCB

Xilinx FPGA编程技巧之常用时序约束详解

的关系。

1. 系统同步输入约束System Synchronous Input

在系统同步接口中,同一个系统时钟既传输数据也获取数据。考虑到板子路径延时和时钟抖动,接口的操作频率

发表于 05-06 15:51

时序约束实操

添加约束的目的是为了告诉FPGA你的设计指标及运行情况。在上面的生成约束之后,在Result àxx.sdc中提供约束参考(请注意该文件不能直接添加到工程中,需要热复制到别的指定目录或者新建自己的SDC文件添加到工程)。

Xilinx FPGA的约束设置基础

LOC约束是FPGA设计中最基本的布局约束和综合约束,能够定义基本设计单元在FPGA芯片中的位置,可实现绝对定位、范围定位以及区域定位。

发表于 04-26 17:05

•1185次阅读

Xilinx FPGA编程技巧之常用时序约束详解

。

1. 系统同步输入约束System Synchronous Input在系统同步接口中,同一个系统时钟既传输数据也获取数据。考虑到板子路径延时和时钟抖动,接口的操作频率不能太高

发表于 04-12 17:39

FPGA物理约束之布局约束

在进行布局约束前,通常会对现有设计进行设计实现(Implementation)编译。在完成第一次设计实现编译后,工程设计通常会不断更新迭代,此时对于设计中一些固定不变的逻辑,设计者希望它们的编译结果

PADS约束管理系统创建、审查和验证PCB设计约束

PADS约束管理系统创建、审查和验证PCB设计约束

评论