很容易验证间隙,高速,制造的约束,并通过计算最大的焊盘和可测试性极限。建立、保存和使用验证方案。只有两次鼠标点击,违规行为才能以直观的形式发生。自动从电子表格中选择一个冲突,以放大和更正该冲突,并快速重新验证已修复该冲突。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

计算

+关注

关注

2文章

452浏览量

38889 -

PADS

+关注

关注

80文章

808浏览量

107996 -

焊盘

+关注

关注

6文章

558浏览量

38263

发布评论请先 登录

相关推荐

PADS逻辑教程

PADSlogic9.6电路图设计资料手册(中文教程)为motor Graphics公司软件提供的原本中文手册,用于PADSlogic软件电路图设计参考使用。PADS Logic用户界面旨在提高

发表于 12-16 14:33

•0次下载

时序约束一主时钟与生成时钟

的输出,对于Ultrascale和Ultrascale+系列的器件,定时器会自动地接入到GT的输出。 1.2 约束设置格式 主时钟约束使用命令create_clock进行创建,进入Timing

常用时序约束使用说明-v1

为了防止约束失败,我们在Tcl输入框中验证,没有告警或者错误说明约束的写法是正确的set_max_delay 5.00 -from [get_cells key2_detect_inst/state

急!!!!求助大佬。PADS LAYOUT软件BUG问题

Window11系统,PADS VX2.3版本,

之前PADS软件是正常的,突然用不了鼠标的放大缩小功能,键盘快捷键也没用,并且pads里的功能键都进不去,比如点击pads页面显示颜色

发表于 09-23 14:16

两种SR锁存器的约束条件

基本约束条件: SR锁存器是一种基本的数字逻辑电路,用于存储一位二进制信息。它有两个输入端:S(Set)和R(Reset),以及两个输出端:Q和Q'(Q的反相)。以下是SR锁存器的基本约束

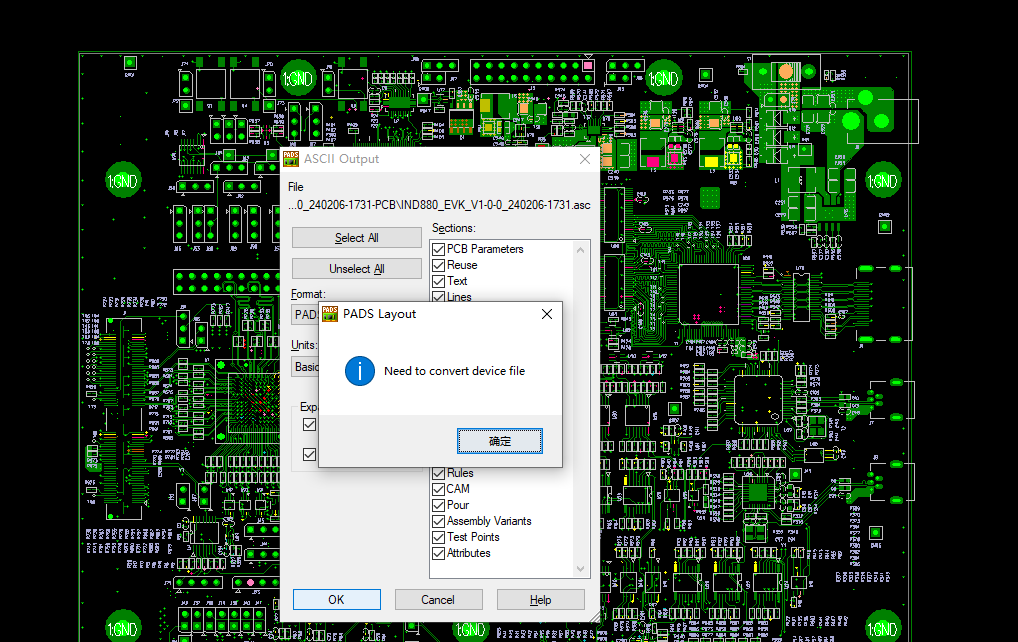

pads闪退故障解决方案 PADS报Need to convert device file然后Open error:devices.dat确定闪退

PADS 报Need to convert device file, 然后Open error:devices.dat 确定闪退

Xilinx FPGA编程技巧之常用时序约束详解

今天给大侠带来Xilinx FPGA编程技巧之常用时序约束详解,话不多说,上货。

基本的约束方法

为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。最普遍的三种路径以及异常路径为

发表于 05-06 15:51

时序约束实操

添加约束的目的是为了告诉FPGA你的设计指标及运行情况。在上面的生成约束之后,在Result àxx.sdc中提供约束参考(请注意该文件不能直接添加到工程中,需要热复制到别的指定目录或者新建自己的SDC文件添加到工程)。

Xilinx FPGA的约束设置基础

LOC约束是FPGA设计中最基本的布局约束和综合约束,能够定义基本设计单元在FPGA芯片中的位置,可实现绝对定位、范围定位以及区域定位。

发表于 04-26 17:05

•1395次阅读

Xilinx FPGA编程技巧之常用时序约束详解

今天给大侠带来Xilinx FPGA编程技巧之常用时序约束详解,话不多说,上货。

基本的约束方法为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。最普遍的三种路径以及异常路径为

发表于 04-12 17:39

PADS的视觉约束验证

PADS的视觉约束验证

评论