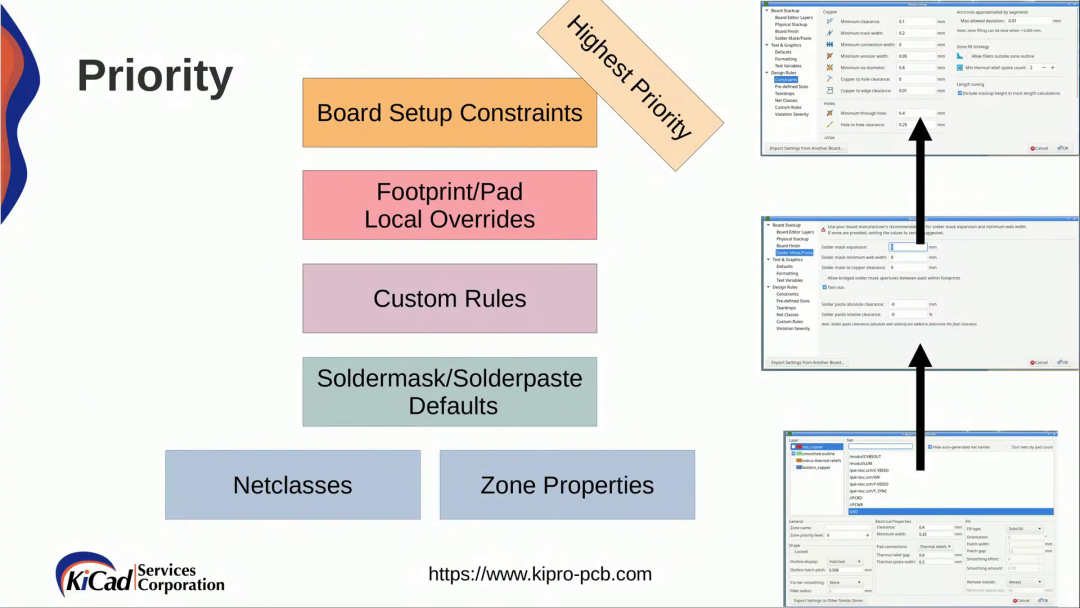

参加这次研讨会,学习如何轻松地管理您的设计规则和约束。我们将研究如何创建约束网、网类、和间隙集,如何建立规则的层次结构,等等。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

pcb

+关注

关注

4421文章

24024浏览量

427013 -

设计

+关注

关注

4文章

830浏览量

71523

发布评论请先 登录

相关推荐

热点推荐

安达发|是什么让日化行业瞬间“开挂”?原来是APS软件!

的优势,逐渐成为日化行业的智能新宠。 APS软件是什么? APS 即高级计划与排程(Advanced Planning and Scheduling)软件,它是一种基于供应链管理和约束理论的先进计划与排产工具。与传统的生产计划方法不同,APS软件能够综合考虑企业的各种资源

Vivado时序约束中invert参数的作用和应用场景

在Vivado的时序约束中,-invert是用于控制信号极性的特殊参数,应用于时钟约束(Clock Constraints)和延迟约束(Delay Constraints)中,用于指定信号的有效边沿或逻辑极性。

输入引脚时钟约束_Xilinx FPGA编程技巧-常用时序约束详解

基本的约束方法

为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。最普遍的三种路径以及异常路径为:

输入路径(Input Path),使用输入约束

寄存器到寄存器路径

发表于 01-16 08:19

如何查看电能质量在线监测装置的数据自动清理规则参数设置是否成功?

远程管理平台,直接查看已配置的自动清理规则参数,确保与预期一致。 1. 本地 LCD / 按键操作(现场快速核对) 操作步骤 界面路径 核对要点 1. 登录管理界面 主菜单→系统设置→存储管理

时序约束问题的解决办法

Time 是否满足约束。

我们要留意的是 WNS 和 WHS 两个数值,如果这两个数值为红色,就说明时序不满足约束。下面将解释怎么解决这个问题。

1. Setup Time 违例

Setup

发表于 10-24 09:55

关于综合保持时间约束不满足的问题

1、将 nuclei-config.xdc 和 nuclei-master.xdc 加入到项目工程中,综合得到时序约束报告如下:

保持时间约束不满足,分析原因,发现所有不满足均出现在

发表于 10-24 07:42

技术资讯 I Allegro 设计中的走线约束设计

本文要点在进行时序等长布线操作的时候,在布线操作的时候不管你是走蛇形线还是走折线,约束管理器会自动帮你计算长度、标偏差,通过精确控制走线长度,来实现信号的时序匹配。约束设计就是一套精准的导航系统

Jtti防火墙规则配置指南:从入门到精通的全面解析

探讨规则优先级设置、协议过滤技巧以及异常流量识别等关键环节,让您掌握专业级防火墙管理能力。 防火墙规则基础原理与架构 防火墙规则配置的本质是

技术资讯 I 图文详解约束管理器-差分对规则约束

本文要点你是否经常在Layout设计中抓瞎,拿着板子无从下手,拿着鼠标深夜狂按;DDR等长没做好导致系统不稳定,PCIe没设相位容差造成链路训练失败……这些都是血泪教训,关键时刻需要靠约束管理器救命

Altium Designer 25.7.1 版本发布,Altium Designer 25.7.1新功能说明

自动刷新 当从原理图向 PCB 推送变更并访问 ECO 对话框时,约束管理器会根据对规则 / 类所做的更改自动刷新。此功能无需访问约束管理

KiCad 中的自定义规则(KiCon 演讲)

“ Seth Hillbrand 在 KiCon US 2025 上为大家介绍了 KiCad 的规则系统,并详细讲解了自定义规则的设计与实例。 ” 演讲主要围绕 加强 KiCad 中的自定义

如何轻松地管理您的设计规则和约束

如何轻松地管理您的设计规则和约束

评论