GAL的基本结构_GAL的逻辑结构

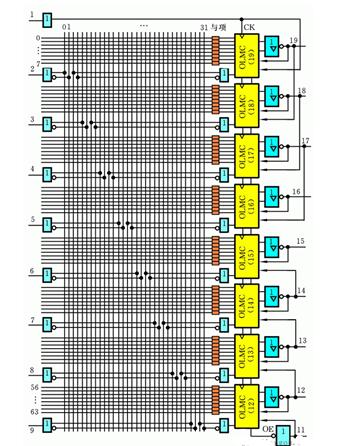

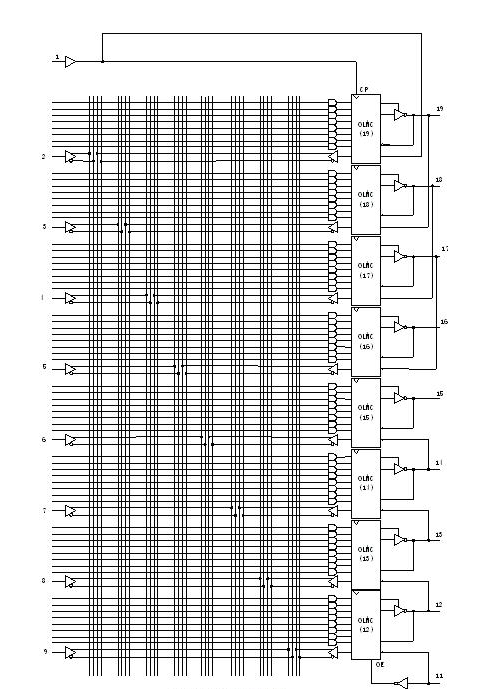

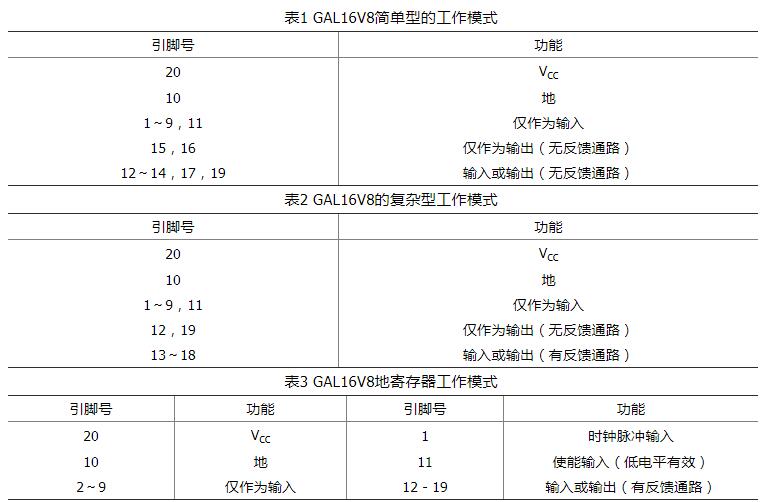

根据GAL器件的门阵列结构,可以把现有的GAL器件分为两大类:一类与PAL器件基本相同,即与门阵列可编程,或门阵列固定连接,这类器件有GAL16V8,ispGAL16Z8等;另一类GAL器件的与门阵列和或门阵列都可编程,GAL39V18就属于这类器件。前一类GAL器件具有基本相同的电路结构。通用型GAL包括GAL16V8和GAL20V8器件。其中GAL16V8是20脚器件,器件型号中的16表示最多有16个引脚作为输入端,器件型号中的8表示器件内含有8个OLMC,最多可有8个引脚作为输出端。同理,GAL20V8的最大输入引脚数是20,GAL20V8是24脚器件。下面以GAL16V8为例,说明GAL的电路结构和工作原理。图1为GAL16V8的逻辑结构图,由五部分组成:

(1) 8个输入缓冲器(引脚2~9作固定输入);

(2)8个输出缓冲器(引脚12~19作为输出缓冲器的输出);

(3)8个输出逻辑宏单元(OLMC12~19,或门阵列包含在其中);

(4)可编程与门阵列(由8×8个与门构成,形成64个乘积项,每个与门有32个输入端);

(5)8个输出反馈/输入缓冲器(即中间一列8个缓冲器)。

图1 GAL16V8的逻辑结构图

除以上5个组成部分外,该器件还有1个系统时钟CK的输入端(引脚1),一个输出三态控制端OE(引脚11)一个电源VCC端和一个接地端(引脚20和引脚10,图中未画出。通常VCC=5V)。

GAL的逻辑结构

GAL16V8芯片是具有8个固定输入引脚、最多可达16个输入引脚,8个输出引脚,输出可编程的一种GAL器件。其逻辑结构如图1所示。

由图可见,它由8个输入缓冲器、8个反馈输入缓冲器、8个输出逻辑宏单元OLMC,8个输出三态缓冲器、与阵列和系统时钟、输出选通信号等组成。其中,与阵列包含32列和64行,32列表示8个输入的原变量和反变量及8个输出反馈信号的原变量和反变量;64行表示与阵列可产生64个与项, 8个输出,每个输出包括8个与项。

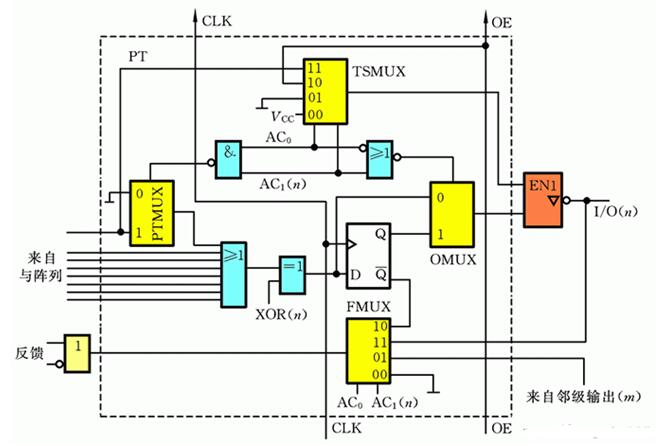

(1)输出逻辑宏单元OLMC

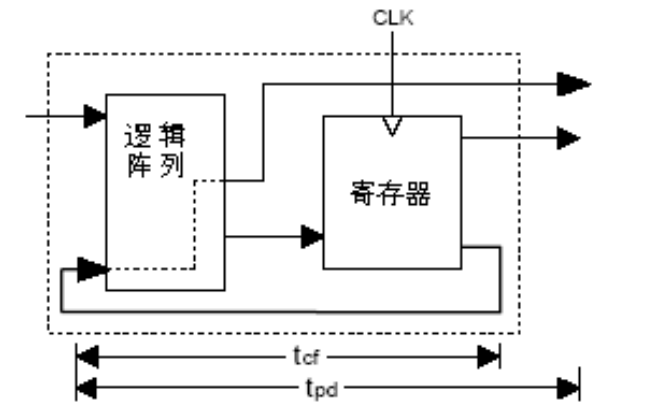

OLMC的逻辑结构示意图如图2所示。它由一个8输入或门、极性选择异或门、D触发器、4个多路选择器等组成。

图中,只要恰当地给出各控制信号的值,就能形成OLMC的不同组态。因此,在适应不同要求方面,OLMC给设计者提供了最大的灵活性。具体各控制信号的值是由GAL结构控制字中的相应可编程位的状态决定的。

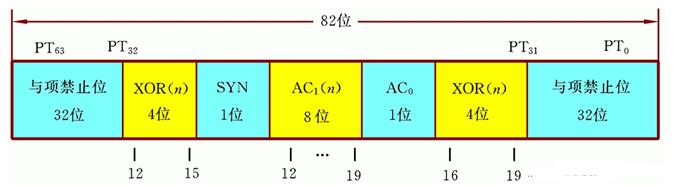

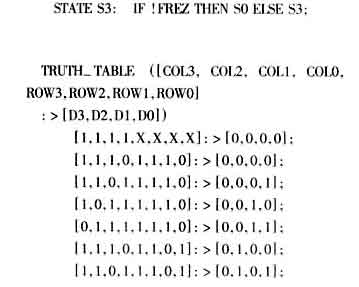

(2)结构控制字

GAL16V8由一个82位的结构控制字控制着器件的各种功能组合状态。控制字中各位的功能如图3所示。图中,XOR(n)和AC1(n)字段下面的数字分别对应器件的输出引脚号,指相应引脚号对应的宏单元。

通过编程结构控制字中的SYN、AC0和AC1(n),输出逻辑宏单元OLMC(n)可以组成以下5种组态。

① 专用输入方式(SYN·AC0·AC1(n)=101)。

② 专用组合型输出方式(SYN·AC0·AC1(n)=100)。

③ 组合型输出方式(SYN·AC0·AC1(n)=111)。

④ 寄存器型器件中的组合逻辑输出方式(SYN·AC0·AC1(n)=011)。

⑤ 寄存器型输出方式(SYN·AC0·AC1(n)=010)。

上述OLMC组态的实现是由开发软件和硬件完成的。开发软件将选择与配制控制字的所有位,并自动检查各引线的用法。

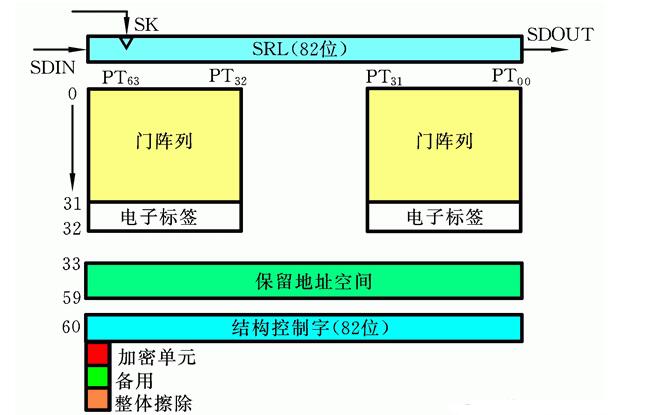

(3)行地址布局

GAL器件的可编程阵列包括与阵列、结构控制字、保密位及整体擦除位等。对其进行编程时是由行地址进行映射的。GAL16V8的行地址布局如图4所示。

-

可编程

+关注

关注

2文章

871浏览量

39861 -

器件

+关注

关注

4文章

312浏览量

27875

发布评论请先 登录

相关推荐

通用阵列逻辑(GAL)电路结构设计分析

基于GAL器件的步进电机控制器的研究与设计

GAL使用教程

通用阵列逻辑GAL实现基本门电路的设计

新型GAL原理和应用

基于GAL6002芯片的去抖编码键盘电路的设计

通用阵列逻辑GAL简介

通用阵列逻辑GAL器件优缺点分析

一文知道GAL的工作模式

GAL16V8芯片的数据手册免费下载

GAL的基本结构_GAL的逻辑结构

GAL的基本结构_GAL的逻辑结构

评论