高速ADC的进步,直接促使3G基站(如WCDMA ,TD-SCDMA,UMTS)接收(RX)和发送(TX)通路的性能改善。随着新基站设计要求低功率工作和小尺寸,对信号链路元件的热性能提出额外的要求。要求ADC低功率,高性能小尺寸。节省板空间的热耗。

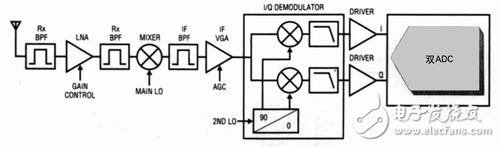

根据终端用户要求,不同制造商所选择的RX通路发生基本的变化。单载波接收机通常采用双ADC取样来自信号信道解调的I和Q,通过单RX通路在中频IF(70MHz-140MHz)直接取样。只要两个ADC之间有足够隔离,采用双ADC才可能。

具有110dB信道隔离性能的双14位80Msps ADC

Linear 公司的低功率高速双ADC,具有-110dB交扰信道隔离和低功耗(每个通道仅444mW,222mW)。73dB SNR(信噪比)和85dB SFKR(无寄生动态范围)的信能,对于基站应用是理想的。除基站应用外,这些低功率双ADC对于其他通信和高端媒体图像处理设备也是适合的。

用于功放线性化的高速ADC

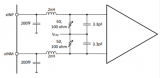

在TX通路,功效(PA)失真是使系统具有更多性能的限制因素,所以,采用不同的方法来线性化PA输出。采用高速ADC和快速数字信号处理方法,用一个反馈通路数字化预改变PA输出(图2)来补偿功放的非线性。

PA线性化的取样率依赖于被数字化的谐波数量和信号带宽。一些PA设计需要185Msps和12位分辨率的ADC。

Linear 公司的LTC2220-1是一款12位185MSPS ADC,具有67.5dB SNR 80dB SFDR、775MHz全功率带宽。这些特性对于功放线性化的数字预变化应用是理想的。对于蜂窝基站收发器间的微波链路也是理想的器件。

除ADC良好的AC性能外,最佳化的逻辑接口对低噪声也是重要的。输入输出可以是低EMI的差分LVDS或单端CMOS。一个分离的数字输出电源,允许CMOS输出摆幅范围0.5V~3.3V,这能匹配低电压DSP,使开关噪声最小。

图1 采用解调I和Q的接收器结构

高SF2R的正交解调器

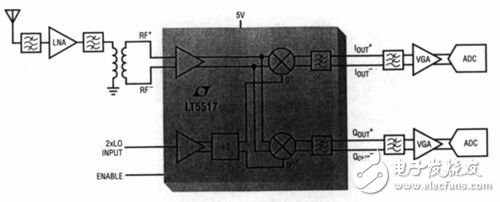

对图1中双ADC之前的信号链路元件也有相同的要求。Linear公司新的、非常高线性度和低噪声I/Q解调器为高线性度和低燥声I/Q调制解调器为记性能接收机提供无线信号到基带的直接变频和IF变频(见图3)。LT5517 I/Q解调器具有23.5dBmIIp3(输入3阶截听点)、9.5dB噪声因数(在200MHz),这些性能适合检测微弱信号,基至在高干扰情况下。此性能导致SFDR超过80dB。LT5517集成有精确的0°和90°分相器,在40MHz~900MHz范围内提供精确RF信号的I(同相)和Q(90°相移)解调,直接到基带。

LT5517非常适合高性能无线基础架构接收器应用中的IF和RF解调。其他应用包括微基站、中继器单元、RFID读机和宽带固定无线接入。

LT5517包含一对匹配的高线性度混频器,带片上正交相位产生器和分相器。I和Q信号通路通常增益匹配到0.03dB,典型的相位失匹为0.7°,这导致高精度I和Q解调。差分I和Q输出具有小的DC偏移(典型值0.5mV,)而内置的130MHz低通滤波器能去除带外噪声。

内部正交分相器采用来自除2电路的本振(LO)。相应地,ZXLO输入口接收2倍 LO频率的信号,因而使得到RF口的LO漏电最小。另外,LT5517具有良好的口间RF漏电,这降低了外部RF滤波器要求。ZXLO输入仅需要-5dBm驱动电平,而且内部与50Ω匹配,因此,能提供一个简单的单端接口。

图2 用85MSPSADC数字预改变PA线性化

图3 单载波接收机的I/Q解调器

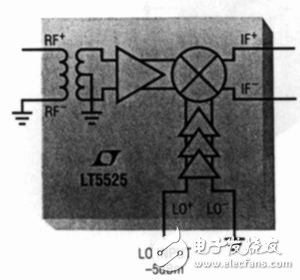

图4 低功率混频器有良好线性性能

RF有源混频器

用单ADC,I/O解调器设计多载波接收机是在数字域进行。LT5525和LT5526有源混频器把高线性度与低功率结合起来。LT5526具有16.5dBmIIP3(在900MHz)和11dB噪声因数。此性能补充0.6dB转换增益。另外LT5526只需要-5dBmLO驱动,而且口间LO漏电低到-65dBm,这降低了外部滤波要求。LT5526具有完全差分输入和输出,并工作在100KHz~2GHz宽范围带宽内。此器件在很多应用中可作为下变频混频器或上变频混频器。

LT5525具有片上RF输入变压器,并在RF和LO输入提供内部50Ω阻抗匹配元件,可以单端驱动这些输入,而不需用外部阻抗匹配元件,因此,便于采用和降低成本(见图4)。LT5525的IIP3为21dBm(在900MHz),噪声因数为14dB(转换增益为-2.6dB)。

LT5525和LT5526都工作在单电源(3.5V~5.3V),工作电流典型值为28mA。

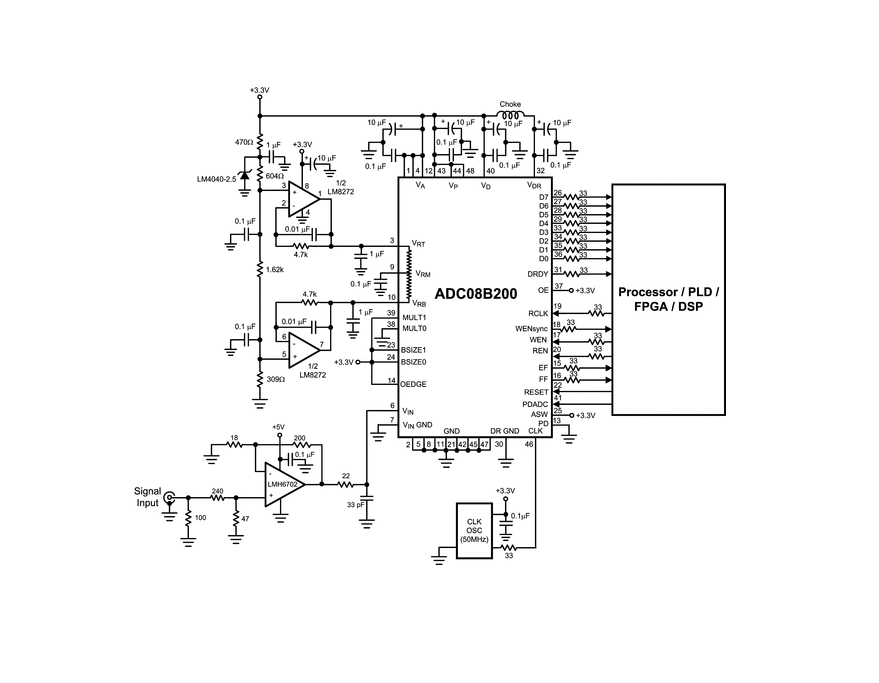

低失真低噪声差分ADC驱动器

LT1993-2是一款低失真低噪声差分放大器,作为ADC驱动器(70MHz输入频率,800MHz -3dB带宽)。特别低的输入噪声和低失真分量,使LT1993-2成为驱动高速12位和14位ADC的理想器件。除额定的非滤波输出外,LT1993-2具有内置175MHz差分低通滤波器和另一对滤波输出,这在驱动高速ADC时,减少外部滤波元件。通过VOCM引脚可以容易地设置共模电压,这样,在很多应用中消除输出变压器或AC耦合电容器。

LT1993-2设计用于满足通信收发器应用的要求。它可以用作为差分ADC驱动器,一个通用增益单元或其他任何应用所需的差分驱动。

责任编辑:zl

-

dsp

+关注

关注

561文章

8288浏览量

368913 -

接口

+关注

关注

33文章

9633浏览量

157770 -

adc

+关注

关注

100文章

7973浏览量

557323

发布评论请先 登录

12位高速IF采样ADC——AD9433的技术解析与应用指南

12 位高速 ADC AD9432:性能剖析与应用指南

16位15Msps SAR ADC LTC2387-16:高速高精度的理想选择

AD9695:高速ADC的卓越之选

AD4087:高速低噪SAR ADC的卓越之选

AD4084:高速低噪SAR ADC的卓越之选

ADC1175:低功耗高速A/D转换器的卓越选择

ADC08B200:高速8位A/D转换器的设计与应用指南

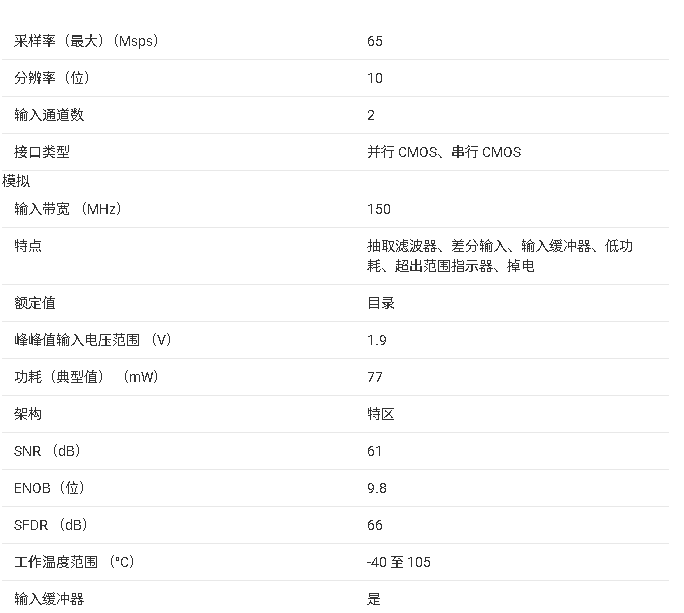

ADC3910D065 10 位高速低功耗 ADC 技术文档总结

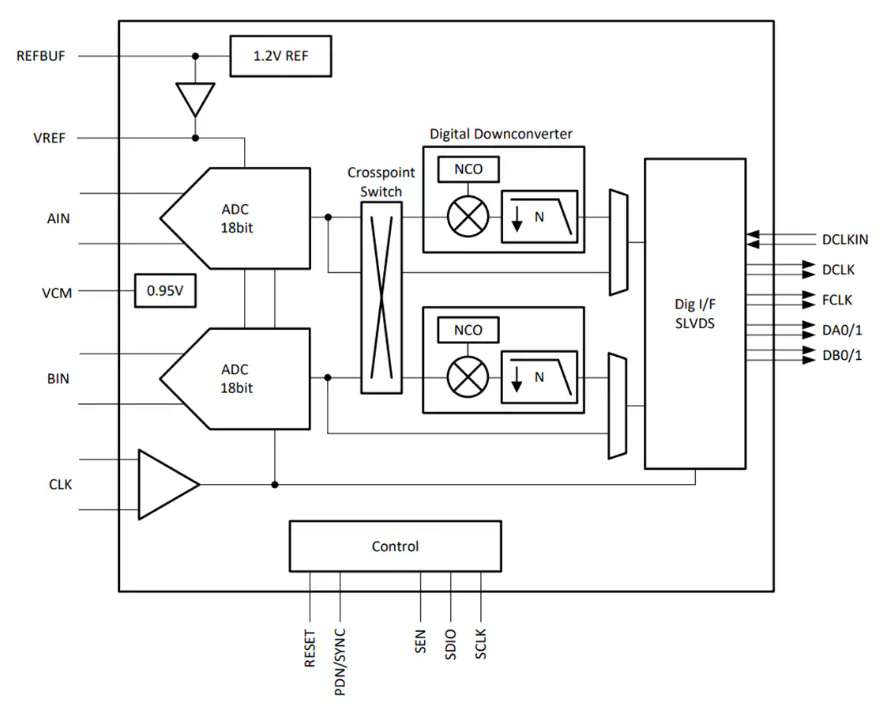

Texas Instruments ADC368x系列:低噪声、低功耗18位高速ADC的技术解析

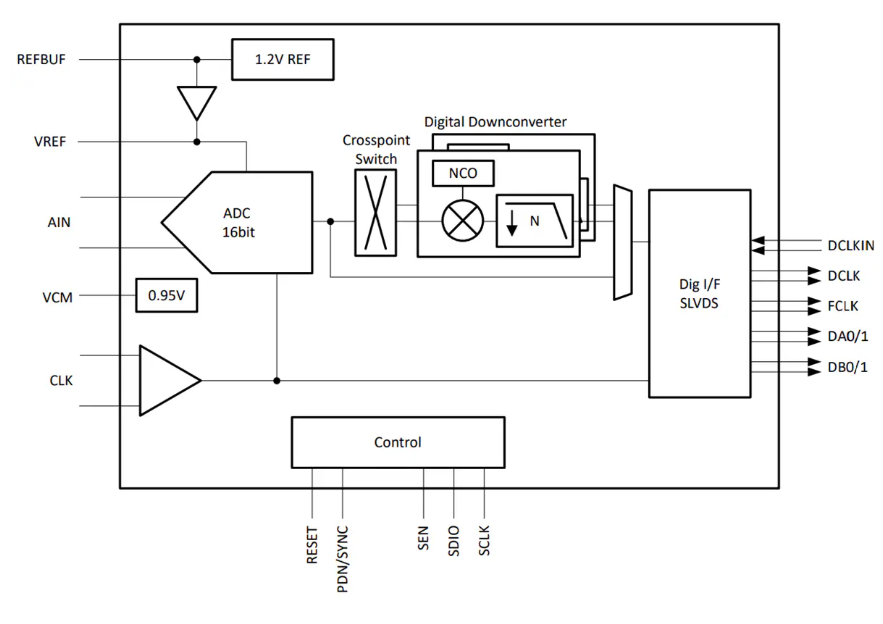

ADC356x系列16位高速ADC技术解析与应用指南

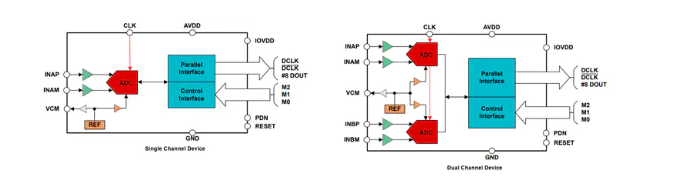

Texas Instruments ADC3908Dx/ADC3908Sx 8位高速ADC数据手册

高速ADC的选择与应用

高速ADC的选择与应用

评论