到底什么是传统的串行工程,什么又是并行工程呢?

这就类似电路中的串联与并联,若用电器逐个依次首尾相连,属于串联,若首首并连,属于并联。举个简单的例子,Layout工程师在设计一款产品时时,所有工作由一个人完成,先布局电源部分,再布局功能部分,最后布局功能小板,这就是串行工程;而同一款产品设计,由3个不同的工程师分别布局电源,功能,功能小板,最后整合,这就是并行工程。

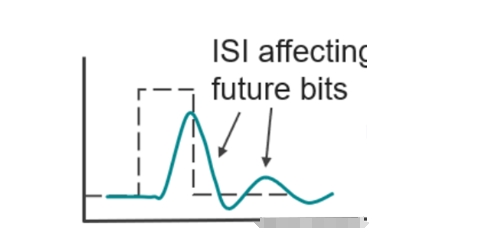

串行与并行开发流程,以PCB设计为例,如下图:

传统的串行开发模式有一个糟糕的开局,也就必然会有后续不断的设计更改、设计优化等。在很多批量生产的设计实践中,一开始参与的人数非常少,没有考虑制造、测试、装配、成本、质量等因素,在临近发布日期的时候人数增长到了峰值,很多人参与到了解决问题的过程中。然而,这些问题本应该在一开始就要被清理干净。

如果一个项目没有早期被纳入DFX,那么在后期想要使产品具有可制造性、可装配性,可测试性,可维护性,成本优化,可维护性等等,那将变得异常困难,即产品开发的墨菲定律。在紧张的时间压力下,面对着通过更改订单实施DFX的艰巨难题,团队只会进行简单的修改,导致产品的可制造性、产品质量等更为不可靠。

简单归纳:

- 并行工程要求:产品在一开始就考虑产品整个生命周期中从概念形成到产品生命周期结束的所有因素,包括制造、装配、测试、质量、成本、进度计划和用户要求等

- 目标:并行工程的目标为提高质量、降低成本、缩短产品开发周期和产品上市时间。

- 具体做法:在产品开发阶段,组织多种职能协同工作的项目组,并使用并行工具,使有关人员从一开始就获得对新产品需求的要求和信息,积极研究涉及本部门的工作业务,并将所需要求提供给设计人员,使许多问题在开发早期就得到解决,从而保证了设计的质量,避免了大量的返工浪费.

然而,决定并行工程成败的关键因素是资源的可获得性,充足的资源能够让多功能型团队的各领域专家在早期集结并开始工作。

发布评论请先 登录

相关推荐

请问如何接收并处理ads8411的2Msps@16bit并行数据?

高速并行总线的工作原理是什么 高速并行总线有哪些

请问ESP32的io作业和cpu作业是并行进行的吗?

如何设置ESP32C3的I2S LCD多路并行信号输出?

CMOS四段并行输入/并行输出移位寄存器CD4035B TYPES 数据表

并行ad转换器的特点有哪些

如何在AMD Vivado™ Design Tool中用工程模式使用DFX流程?

DFX——并行工程2

DFX——并行工程2

评论