全球最大容量FPGA记录被再度刷新。

早前,已有一些客户陆续收到Intel一款号称全球容量最大的FPGA样品。近日,Intel正式宣布这款Stratix 10 GX 10M FPGA已量产,它拥有1020 万个逻辑单元,433亿颗晶体管,采用14nm制程,是目前已发布的全球密度最高的FPGA产品,是上一代Stratix 10 GX 1SG280 FPGA 密度的 3.7 倍,实现I/O 2倍扩展,功耗降低40%。

这一产品的推出,打破了Xilinx全球三代最大容量FPGA的保持纪录,其最新一代大容量FPGA是今年夏天推出的Virtex UltraScale+ VU19P,采用16nm工艺,基于Arm架构,拥有350亿颗晶体管。

谁在推动FPGA容量不断攀高?

FPGA(Field-Programmable GateArray)现场可编程门阵列,由于其硬件并行加速能力和可编程特性,在传统通信领域和IC设计领域很受欢迎。特别是伴随着全球通信市场的发展壮大,FPGA以“万金油”的优势迅速找到了用武之地,成为数字系统中的通用组件。FPGA潜力之巨大、前景之诱人,使得当时不乏IBM、摩托罗拉、飞利浦这些行业巨头前仆后继去尝试,但由于其开发门槛太高,没有坚实的技术积累和长时间的投入,很难形成有竞争力的产品。最终仅以美国硅谷四家公司Xilinx、Altera、Lattice、Microsemi为代表,牢牢占领着主要份额,并铸就了高耸的专利围墙。2015年6月,Intel以167亿美元收购全球第二大FPGA厂商Altera,才算正式进入这一市场,这也创下了Intel有史以来最贵的一笔收购。

伴随5G、AI等发展,FPGA在推动创新方面的优势越来越显著,主要体现在三方面:它可以作为先进的多功能加速器;凭借其灵活性能够打造出高度差异化的产品;其硬件可编程性能够满足不断变化的市场要求和标准。

而除此之外,FPGA在另一个领域的需求也水涨船高。

一颗芯片从设计到量产,流片环节占据大额支出。芯片完全设计出来后,需要按照图纸在晶圆上进行蚀刻,采用什么样的制程工艺、多大尺寸的晶圆,以及芯片的复杂程度,都会影响这颗芯片的流片成功率。许多芯片往往需要进行多次流片才能获得较为理想的效果,这些失败流片构成了一大笔费用支出。此外,当芯片制造完成后,如果需要修复硬件设计缺陷,通常需要昂贵的重新设计的费用以及额外的时间支出。特别是当设备制造出来并交付给终端客户的情况下,解决这些问题的成本会更高,甚至远远超出金钱本身的估量。

正因为以上问题带来如此之高的风险,流片前的仿真和原型设计系统越来越普及,因为在风险如此之高的情况下,没有哪个设计团队敢于忽视这项谨慎又必要的验证性投资。它能够帮助半导体厂商在芯片制造前发现问题,避免代价高昂的软硬件设计缺陷,带来数百万美元的费用节省。

由于ASIC 仿真和原型设计系统可以帮助设计团队大幅降低设计风险。包括Intel在内的很多大型半导体公司都开发了自定义原型设计和仿真系统,并在流片前使用该系统来验证自身大规模、高复杂度、高风险的 ASSP 和 SoC 设计。

ASIC 仿真和原型设计系统支持很多与 IC 和系统开发相关的工作,包括:

那么,超大容量FPGA又能满足哪些应用需求?

随着半导体制造技术不断的前进、相应的设计规模以及复杂度在飞速增长,使得传统的软件仿真已不可能完全解决功能验证的问题。而且一些需要处理大量实时数据的应用(如视频)也越来越多,因此要求能够在接近实时的条件下进行功能验证。FPGA在实现高效的仿真和功能验证方面,被寄予厚望。

ASIC原型设计和仿真市场迫切需要容量更大的FPGA。目前,市场上已经有数家供应商提供商用现成 (COTS) ASIC原型设计和仿真系统,对于这些供应商而言,如果能够将更大容量的FPGA 用于其 ASIC 仿真和原型设计系统中,就意味着他们能够在尽可能少的 FPGA 设备中纳入大型 ASIC、ASSP 和 SoC 设计。据了解,使用Intel最新的Stratix 10 GX 10M FPGA,能够用于耗用亿级 ASIC 门的数字 IC 设计。

如下是该产品在ASIC原型设计、仿真,满足具体的需求方面,与上一代产品相比带来的性能提升:

超大容量FPGA是如何实现的?

Intel最新发布的这款元件密度极高的Stratix 10 GX 10M FPGA,是基于现有的Stratix 10 FPGA 架构以及先进的嵌入式多芯片互连桥接 (EMIB) 技术。正是通过EMIB 技术,才融合了两个高密度Stratix 10 GX FPGA 核心逻辑晶片(每个晶片容量为 510 万个逻辑单元)以及相应的 I/O 单元,这也是第一款使用 EMIB 技术将两个 FPGA构造晶片在逻辑和电气上实现整合的Intel的FPGA。数万个连接通过多颗 EMIB 将两个 FPGA 构造晶片进行连接,从而在两个单片 FPGA 构造晶片之间形成高带宽连接。可以说,Intel推出这款世界上最大型的FPGA不仅仅是产品级的超越和创新,更是综合实力的体现。

Intel网络与自定义逻辑事业部副总裁兼 FPGA电源产品营销总经理Patrick Dorsey在采访中表示,独有的封装技术,以及能够整合不同半导体晶片的能力,包括 FPGA、ASIC、eASIC 结构化 ASIC、I/O 单元、3D 堆叠内存单元和光子器件等。Intel具备将不同类型的设备整合到封装系统 (SiP) 中的能力,能够满足特定的客户需求,这些先进技术彼此结合,构成了Intel独特、创新且极具战略性的优势。

此前,Intel已经通过使用EMIB 技术将 I/O 和内存单元连接到 FPGA 构造晶片,从而实现了Stratix 10 FPGA 家族的规模和种类不断扩张。例如:Stratix 10 MX 集成了 8 GB 或 16 GB的 EMIB 相连的 3D 堆叠 HBM2 SRAM 单元,最近发布的Stratix 10 DX FPGA 则集成了 EMIB 相连的 P tile,具备 PCIe 4.0 兼容能力。

Stratix 10 GX 10M 的目标受众主要是ASIC 仿真和原型设计的客户,赋能下一代5G、AI、网络ASIC验证。Patrick Dorsey强调,由于在AI和5G领域很多中国企业已经冲在前面,因此这款新品对于中国市场而言非常重要。

高端FPGA未来拼什么?

回顾FPGA的发展,很大程度上是由工艺技术驱动的,很容易把它的进化看成是简单的容量发展。但事实远非如此。正如所有的半导体芯片一样,它对于功耗、面积、成本、性能的追求永不止步,特别是在“异构计算”盛行的现在,在其异构平台上资源整合的能力变得越来越重要。而除了硬件层面的不断进步,软硬件的协同优化非常关键,从某种程度上甚至可以说,软件工具的研发水平决定了硬件规模和性能所能达到的高度。Intel在FPGA仿真和原型设计系统的开发方面,可提供Quartus Prime 软件套件,该套件采用新款专用IP。面向软件开发人员,Intel近来一直在主推oneAPI,它旨在提供统一的编程模型,用于简化不同架构的开发工作。

应对未来挑战,英特尔网络和定制逻辑事业部副总裁兼FPGA和电源产品部门总经理David Moore指出,以数据为中心的时代重要的不仅仅是数据量,数据的类型同样需要关注。以类型划分,数据可分为结构化数据、非结构化数据和最佳处理近源数据。这些数据采用全新的数据并行化方式,具备新的数字格式和精度特性,并对实时和QoS提出了更高的要求。

从边缘到云,数据洪流将将产生深远的影响。这也意味着需要更多硬件和软件的深度定制以及更高灵活性。David Moore表示,Intel FPGA的优势在于拥有先进的多功能加速器支持,自身灵活性可助力客户打造高度差异化产品。基于FPGA,Intel构建了一整套体系,包括IA+FPGA解决方案、合作伙伴和生态系统、软件与IP,以及芯片和主板,覆盖从边缘计算到云端再到网络等领域。

在软件和IP方面,英特尔提供了包括基于 LLVM的SYCL开源编译器、Intel C++ Compiler编译器、OpenVINO工具包等;具体到垂直细分应用层面,Intel FPGA已渗透到嵌入式、边缘计算、物联网、网络连接,以及云和企业等领域。Patrick Dorsey以Intel PAC D5005在AI领域对深度语音识别的加速、PAC Arria 10 GX FPGA对视频分析加速的两大方案为例,指出了Intel不同于其他加速卡产品的最大区别:Intel拥有从端到云的完整加速卡产品线,同时提供较完整的硬件+平台+行业标准的解决方案,能够帮助用户快速将产品推向市场。

此外,Intel形成了包括FPGA、eASIC、ASIC在内的一系列自定义逻辑解决方案组合,凭借可编程性、可扩展性、低时延性、高存储容量等特点,不仅提供更多选择以及跨整个产品生命周期的灵活优化,并且有效帮助客户缩短上市时间,降低总拥有成本。

当然,在这些基础上,重中之重还在于生态系统的建设。Patrick Dorsey在回答高端FPGA开发挑战这个问题时就强调,生态系统的搭建举足轻重。英特尔在做更多FPGA平台级的开发,建立更多软件的堆栈,推动更多主板的开发工作,努力想创造一些新的市场机遇。这也要求FPGA有更多的能力去适应新应用场景,意味着需要和更多的系统集成商、增值服务渠道商合作,共同推动FPGA的发展。

显然,不论是软硬件协同发展,还是扩大生态系统,最终都指向了“易用性”这一终极目标。

易用性对于FPGA的下一个阶段至关重要。如何最大程度释放硬件性能、如何简化跨不同计算架构应用程序的开发工作,成为为数不多的FPGA玩家共同面临的难题。

至于这种易用性如何实现?是通过更好的软件工具,更高级的设计规划,还是更为先进的工艺、封装技术?也许,答案并不唯一,就像所有的人生经验都需要沉淀,所有的成功都需要积累,经历过应用检验后的产品最终会在市场上大放异彩。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1632文章

21816浏览量

607020 -

容量

+关注

关注

0文章

117浏览量

21291 -

intel

+关注

关注

19文章

3485浏览量

186611 -

AI

+关注

关注

87文章

32008浏览量

270861 -

密度

+关注

关注

0文章

54浏览量

14693 -

5G

+关注

关注

1356文章

48523浏览量

566713

发布评论请先 登录

相关推荐

WaveVision软件根据什么原理对四路数据进行拼数的?

的频率范围为0~600M,不是0~1.2G。为什么频率范围是0~600M??WaveVision 软件根据什么原理对四路数据进行拼数的??谢谢!

发表于 01-03 07:54

大多数FPGA的程序存储器(FLASH)为什么都放在外面呢?FPGA的主要应用

FPGA的主要应用: FPGA由于其较高的价格和成本,决定了FPGA不能像单片机那样被广泛的使用,FPGA的针对于高端处理市场(类如:手机

拼多多第三季度财报发布:营收增长44%

近日,拼多多发布了其截至2024年9月30日的第三季度未经审计财务报告。报告显示,拼多多在该季度实现了总营收993.544亿元人民币,较去年同期增长了44%,但略低于市场预期的1028.3亿元

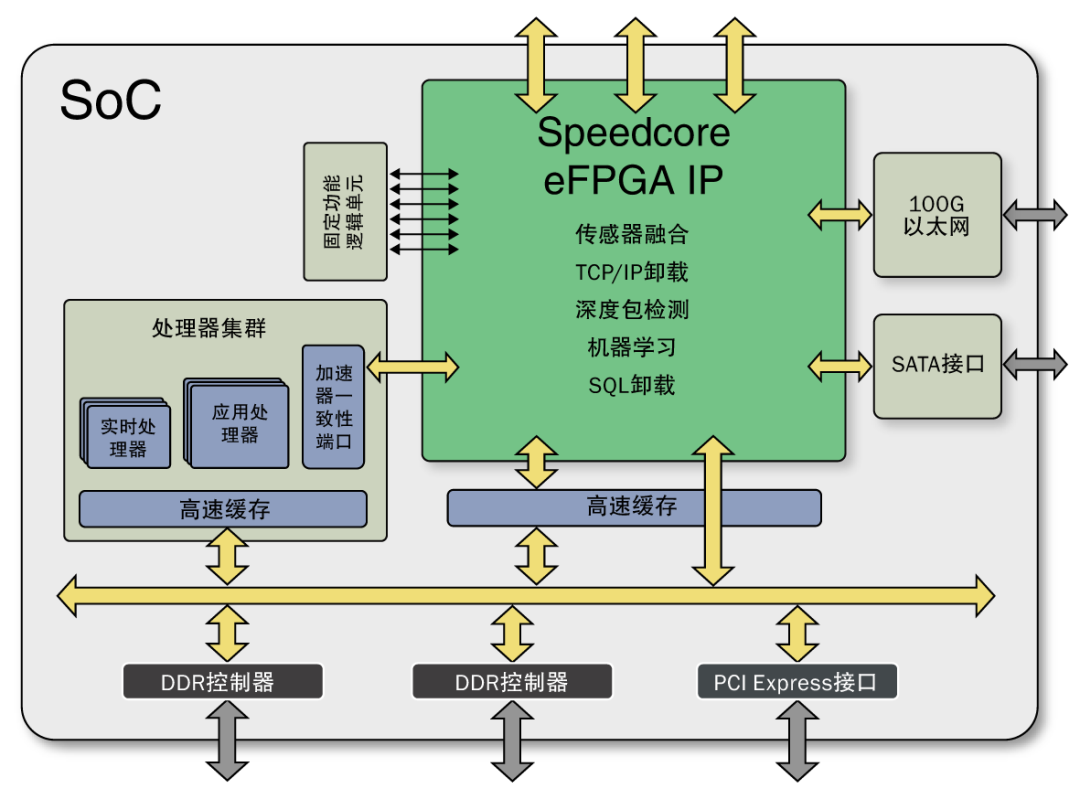

Achronix Speedcore eFPGA的特性和功能

Speedcore嵌入式FPGA(embedded FPGA,eFPGA)知识产权(IP)产品是Achronix公司于2016年推出的颠覆性技术,并于当年开始向最终客户交付,目前出货量

薄板拼焊激光焊接工艺

薄板拼焊激光焊接工艺具有热影响区小、速度快、焊接质量高等优点,广泛应用于汽车、航空航天、电子设备等领域。未来,该工艺将向高效、高精度、智能化方向发展,拓展更多应用领域,推动制造业发展。

莱迪思MachXO5D-NX FPGA的性能

从行业第一颗安全控制FPGA芯片MachXO3D和具备“高端加密功能”的安全控制FPGA Mach-NX,到“增强型安全控制FPGA”MachXO5-NX,再到最新推出的MachXO5

中高端FPGA如何选择

随着国产FPGA的崛起,中低端产品中,很多国产FPGA都是不错的选择,性价比很高。高端FPGA中,往往还是以AMD和Intel为主,但最近这几年,Achronix公司的

发表于 04-24 15:09

Xilinx 7系列FPGA功能特性介绍

Xilinx7系列FPGA由四个FPGA系列组成,可满足一系列系统需求,从低成本、小尺寸、成本敏感的大容量应用到最苛刻的高性能应用的超高端连接带宽、逻辑容量和信号处理能力。

发表于 04-22 10:49

•5963次阅读

FPGA 完整形式

,并且具有更多的门,因此更复杂。它们提供了性能和成本之间的平衡。

高端 FPGA –

它们具有较大的门密度,因此比中端更复杂。它们的性能优于中低端 FPGA 和一些高端

发表于 03-30 11:49

激光拼焊如何提高汽车制造工艺?

随着激光拼焊的技术成熟及推广,激光拼焊也逐步成为汽车行业降低坯料制造成本,提高生产效率,优化模具生产工艺的一项重要技术。激光拼焊与传统电阻焊对比的优点 激光拼焊技术在汽车生产制造中的主

为何高端FPGA都非常重视软件

在本系列的第1部分中,我们研究了Xilinx,Intel和Achronix的新型高端FPGA系列,并讨论了它们的底层半导体工艺,可编程逻辑LUT结构的类型和数量,DSP /算术资源的类型和数量以及

发表于 03-23 16:48

Achronix的FPGA有何优势?为什么能挑战AMD在高端FPGA的地位?

随着国产FPGA的崛起,中低端产品中,很多国产FPGA都是不错的选择,性价比很高。

FPGA与MCU的区别

寄存器的作用,单片机用途比较广,一般用在控制流水线上。

FPGA 它的结构是查找表结构,其程序不用去太考虑芯片的结构,要注意的是时序上问题,它的结构比较复杂,功能也很强大,一般应用在**通信**领域等比较高端

发表于 03-16 07:14

AMD进军低成本FPGA市场,满足边缘应用需求

虽然赛灵思主攻高端FPGA市场,但其对低成本FPGA市场的投入也不容小觑。此次发布的Spartan UltraScale+正是AMD进军低成本FPGA市场的重要战术。

硝烟再起!高端FPGA最终拼什么?

硝烟再起!高端FPGA最终拼什么?

评论