(文章来源:半导体投资联盟)

随着中美贸易摩擦日益加剧,中国半导体产业的发展受到了一定程度的影响。美国提出其技术成分超过25%的产品就有可能受到美国出口管制的限制,因此芯片研发的自主可控必会成为我国发展集成电路产业的共同方向。

在ARM和Intel主导的竞争格局中,新的开源指令集架构RISC-V近两年的发展如同异军突起。随着以RISC-V为主体的开源芯片生态逐步建立,IoT、AI、自动驾驶以及移动终端等领域的芯片创新热情也持续升温。11月12日-13日,中国第一届RISC-V论坛在深圳举行。2017年图灵奖得主、加州伯克利大学教授、计算机体系结构领域享誉世界的科学家大卫·帕特森(David Patterson)出席论坛并发表了演讲。

帕特森教授在其主题演讲中提到,RISC-V指令集是一个不受出口管制的开源指令集。这个对于中国自主可控CPU的开发是非常关键的。

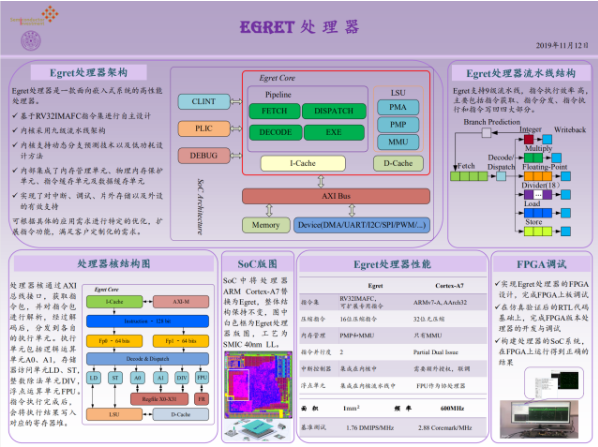

值得关注的是,厦门半导体投资集团有限公司携手清华大学在本次论坛上发布了一款基于RISC-V架构的处理器芯片——Egret(意为“白鹭”)。Egret是一款32位单核处理器,采用中芯国际40nm工艺,主要应用于边缘计算领域。值得注意的是,由于这款处理器对标ARM Cortex-A7,在保持功耗性能与其持平的同时,两者的处理器接口也保持一致。

集微网在对何虎教授的采访中得知,相比ARM Cortex-A7来说,Egret的优势在于,使用RISC-V架构免去了授权费,达到降本的效果;同时更加灵活,能够实现定制化的服务;并且处理器接口与ARM能够兼容,客户替换所需的各项成本非常低。据悉,Egret处理器将于下个月流片。

据何虎教授介绍:“首款Egret处理器是一颗32位的单核处理器,对标的是ARM一颗中端处理器(Cortex-A7)。我们了解到,目前32位的处理器在国内需求非常大,所以我们在明后两年内还会陆续推出双核、四核的产品。同时,根据应用和客户需求也会有一些64位的产品发布。在此之后,我们的计划是会推出一些更高性能的处理器,主要面向人工智能这类高端应用,希望能够以开放的格局,探索出支持产业发展的新思路。”

除了这次发布的处理器内核本身以及未来的研发计划,何虎教授还针对目前RISC-V的发展重心及前景发表了见解。事实上在RISC-V迅速发展的当下,也曾面临着ARM提出的关于可扩展指令集可能带来碎片化、成本、生态系统、安全性、设计保证问题等多方面的质疑。

面对这些质疑的声音,何虎教授指出:“除了RISC-V的出现瓜分了ARM在嵌入式市场的利益之外。首先ARM提出的这些质疑的确是有依据和道理的,其次是这对于RISC-V来说,我认为更应该将其视作一个提醒,这些都是很好的建议,也是RISC-V开发路上一定会面临的挑战。”而相比ARM或是X86架构,RISC-V在技术角度来看灵活性是其最大的优势。其这一特性,在当前嵌入式市场的竞争中体现得愈发明显。

何虎教授认为,嵌入式市场是现阶段RISC-V实现发展和进步的一个最好的切入点。在通用市场中,以X86架构为例,有非常非常多的软件都是基于这个架构设计的,如果这个节点让用户更换为RISC-V的架构,那么需要付出的成本是非常高的。相比之下,嵌入式系统的规模更小,更具有灵活性,用户即便是做替换,也不用需要太多的成本。

除了产品进步本身需要面临的问题和挑战,生态的建设对于一个指令集的成功至关重要。当前,全球RISC-V生态的建设刚刚起步。

(责任编辑:fqj)

-

处理器

+关注

关注

68文章

19083浏览量

228729 -

芯片

+关注

关注

452文章

50150浏览量

420492

发布评论请先 登录

相关推荐

基于RISC-V架构的Egret处理器将很快进行量产

基于RISC-V架构的Egret处理器将很快进行量产

评论