(文章来源:机器之心Pro)

TSP 的全称是 Tensor Streaming Processor,专为机器学习等 AI 相关需求打造。该架构在单块芯片上可以实现每秒 1000 万亿(10 的 15 次方)次运算,是全球首个实现该级别性能的架构,其浮点运算性能可达每秒 250 万亿次(TFLOPS)。在摩尔定律走向消亡的背景下,这一架构的问世标志着芯片之争从晶体管转向架构。

250 TFLOPS 浮点运算性能是什么概念?目前的世界第一超级计算机 Summit,其峰值算力为 200,794.9 TFLOPS,它的背后是 28,000 块英伟达 Volta GPU。如果 TSP 达到了类似的效率,仅需 803 块就可以实现同样的性能。Groq 在一份白皮书中介绍了这项全新的架构设计。此外,他们还将在于美国丹佛举办的第 23 届国际超算高峰论坛上展示这一成果。

我们为这一行业和我们的客户感到兴奋,Groq 的联合创始人和 CEO Jonathan Ross 表示。顶级 GPU 公司都在宣称他们有望在未来几年向用户交付一款每秒百万亿次运算性能的产品,但 Groq 现在就做到了,而且建立了一个新的性能标准。就低延迟和推理速度而言,Groq 的架构比其他任何用于推理的架构都要快许多倍。我们与用户的互动证明了这一点。

Groq 的 TSP 架构是专为计算机视觉、机器学习和其他 AI 相关工作负载的性能要求设计的。对于一大批需要深度学习推理运算的应用来说,Groq 的解决方案是非常理想的选择,Groq 的首席架构师 Dennis Abts 表示,但除此之外,Groq 的架构还能用于广泛的工作负载。它的性能和简洁性使其成为所有高性能即数据和计算密集型工作复杂的理想平台。

Groq 的这款架构受到软件优先(software first)理念的启发。它在 Groq 开发的 TSP 中实现,为实现计算灵活性和大规模并行计算提供了一种新的范式,但没有传统 GPU 和 CPU 架构的限制和沟通开销。在 Groq 的架构中,Groq 编译器负责编码所有内容:数据流入芯片,并在正确的时间和正确的地点插入,以确保计算实时进行,没有停顿。执行规划由软件负责,这样就可以释放出原本要用于动态指令执行的宝贵硬件资源。

在传统的体系架构中,将数据从 DRAM 移动到处理器需要大量的算力和时间,而且相同工作负载上的处理性能也是可变的。在典型的工作流中,开发人员通过反复运行工作负载或程序来对其进行配置和测试,以验证和度量其平均处理性能。由于处理器接收和发送数据的方式不同,这种处理可能会得到略有差别的结果,而开发人员的工作就是手动调整程序以达到预定的可靠性级别。

但有了 Groq 的硬件和软件,编译器就可以准确地知道芯片的工作方式以及执行每个计算所需的时间。编译器在正确的时间将数据和指令移动到正确的位置,这样就不会有延迟。到达硬件的指令流是完全编排好的,使得处理速度更快,而且可预测。开发人员可以在 Groq 芯片上运行相同的模型 100 次,每次得到的结果都完全相同。对于安全和准确性要求都非常高的应用来说(如自动驾驶汽车),这种计算上的准确性至关重要。

另外,使用 Groq 硬件设计的系统不会受到长尾延迟的影响,AI 系统可以在特定的功率或延迟预算内进行调整。这种软件优先的设计(即编译器决定硬件架构)理念帮助 Groq 设计出了一款简单、高性能的架构,可以加速推理流程。该架构既支持传统的机器学习模型,也支持新的计算学习模型,目前在 x86 和非 x86 系统的客户站点上运行。

为了满足深度学习等计算密集型任务的需求,芯片的设计似乎正在变得越来越复杂。但 Groq 认为,这种趋势从根本上就是错误的。他们在白皮书中指出,当前处理器架构的复杂性已经成为阻碍开发者生产和 AI 应用部署的主要障碍。当前处理器的复杂性降低了开发者工作效率,再加上摩尔定律逐渐变慢,实现更高的计算性能变得越来越困难。

Groq 的芯片设计降低了传统硬件开发的复杂度,因此开发者可以更加专注于算法(或解决其他问题),而不是为了硬件调整自己的解决方案。有了这种更加简单的硬件设计,开发者无需进行剖析研究(profiling),因此可以节省资源,更容易大规模部署 AI 应用。与基于 CPU、GPU 和 FPGA 的传统复杂架构相比,Groq 的芯片还简化了认证和部署,使客户能够简单而快速地实现可扩展、单瓦高性能的系统。

Groq 的张量流架构可以在任何需要的地方提供算力。与当前领先的 GPU、CPU 相比,Groq 处理器的每个晶体管可以实现 3-6 倍的性能提升。这一改进意味着交付性能的提升、延迟的下降以及成本的降低。结果是,Groq 的架构使用起来更加简单,而且性能高于传统计算平台。

(责任编辑:fqj)

-

谷歌

+关注

关注

27文章

6172浏览量

105622 -

AI芯片

+关注

关注

17文章

1890浏览量

35096

发布评论请先 登录

相关推荐

如何测试晶体管的性能 常见晶体管品牌及其优势比较

晶体管与场效应管的区别 晶体管的封装类型及其特点

晶体管的输出特性是什么

CMOS晶体管的尺寸规则

NMOS晶体管和PMOS晶体管的区别

GaN晶体管和SiC晶体管有什么不同

GaN晶体管的基本结构和性能优势

芯片晶体管的深度和宽度有关系吗

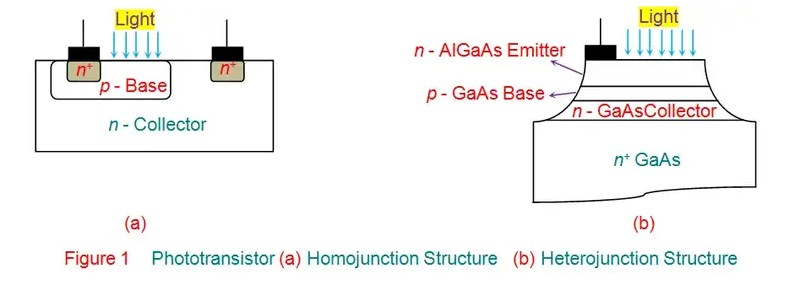

什么是光电晶体管?光电晶体管的工作原理和结构

晶体管测试仪的主要作用

苹果M3芯片有多少晶体管组成

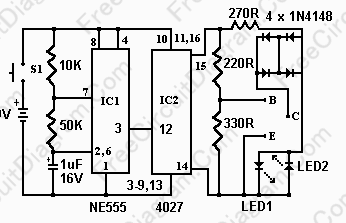

什么是达林顿晶体管?达林顿晶体管的基本电路

谷歌采用全新AI架构,晶体管性能得到巨幅提升

谷歌采用全新AI架构,晶体管性能得到巨幅提升

评论