作为allegro专业layout的我们,由于设计软件的限制,有时候客户提供的原理图可能是AD或Power Logic绘制的,而AD或Power Logic的原理图转成orcad原理图后可能存在丢失网络或器件的风险,无法直接用来输出网表导入Allegro设计。 如果对转换后的原理图进行修正得整个原理图从头到尾彻底检查一遍,这个工作量以及存在的风险对于我们layout工程师和硬件工程师来说可能都不太现实。 如果能将AD或Power Logic原理图产生的网表转成Allegro格式的网表,那就能导入Allegro里面设计了,就不需要转换原理图了,省事又省时,这是最为简单方便又靠谱的方法了。

工程师的巨大福利,首款P_C_B分析软件,点击免费领取

Allegro网表的调法有两种:

一种是第一方网表;

另一种是第三方网表。

第一方网表需要通过Orcad Capture来产生,也是绝大部分人使用的导入方法。 第三方网表可以通过各种原理图设计软件来产生(如protel、AD、Power Logic、DxDesigner、Eagle等)。 第一方网表的调入比较严谨,要求原理图与PCB封装必须完全一一对应,其网表格式也相对复杂。 但是第三方网表的调入就相对没那么严谨,封装的器件管脚只要不比原理图器件管脚少就可以了,器件管脚数量可以不需要一样多,其网表格式相对比较简单有规律性。 因此,我们可以通过将AD或Power Logic原理图产生的网表内容转换成符合Allegro第三方网表的格式,然后导入Allegro即可!

Allegro第三方网表封装定义的标准格式 其中,感叹号和分号是分隔符,Value可有可无,给value添加单引号可屏蔽value值里面的一些非法字符,如下图所示:

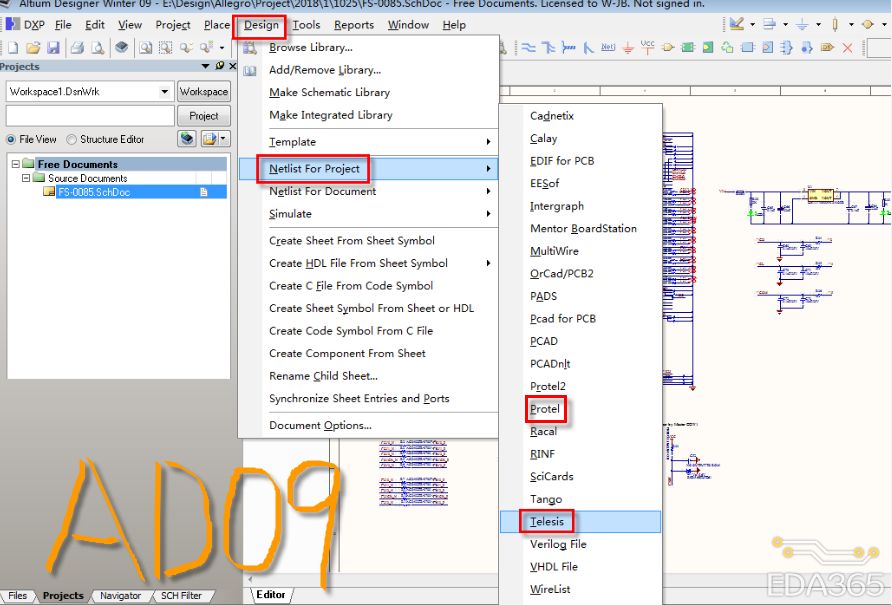

另一种格式的第三方网表 1、输出网表:A. Protel或AD原理图输出的网表可以有两种选择:protel或telesis。

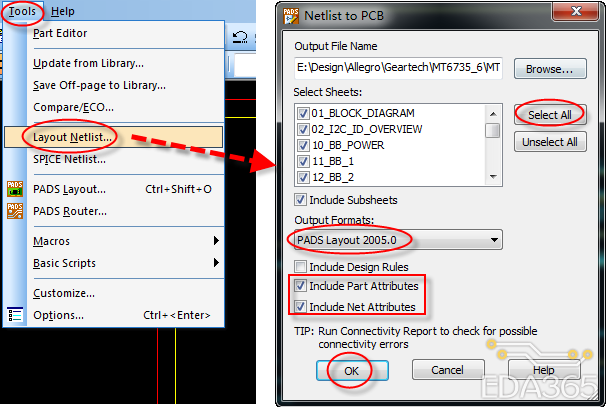

B. Power Logic原理图输出网表:

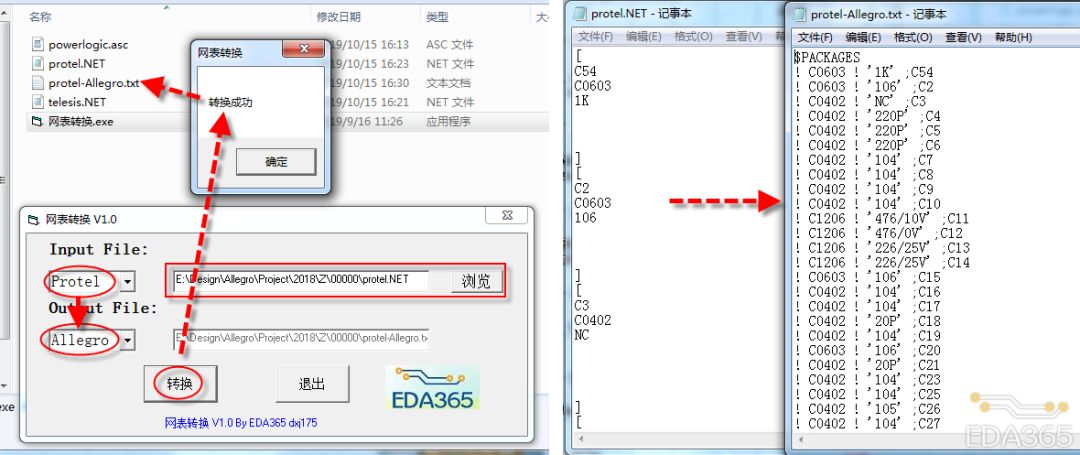

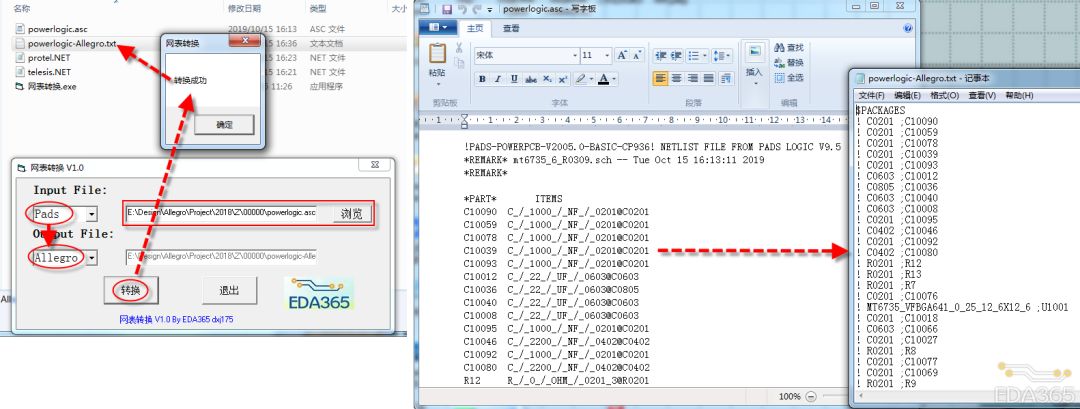

2、将AD或Power Logic输出的网表转换成Allegro格式的第三方网表:使用附件里面的“网表转换.exe”工具将对应格式的网表转成Allegro格式的第三方网表。

注意:“网表转换.exe”工具如果对应网表的格式选择不对,转换出来的网表文件里面的内容是空的。该程序Protel转Allegro网表会将器件的Value值带入,而pads转Allegro网表器件的Value值是不会带入的。

如果是Telesis格式的网表,由于该程序里面没有Telesis格式的网表转Allegro第三方网表,我们可以到以下载一个skill加载使用即可。

注意:文末有下载方式,文章“Protel格式网表转换Allegro格式网表的Skill程序”是一个对skill程序的讲解。

3、Allegro的第三方网表调入与第一方网表调入不同,第三方网表调入还需要器件的device才行。因此我们还需要生成器件的device文件,也就是后缀为txt的封装文件,加载附件里面的skill文件“auto_create_device.il”,然后随便打开封装库里面的任意一个dra文件,在命令栏里面输入命令“create_device_batch”即可将当前目录下的所有dra自动生成psm,pad和txt文件;

skill的加载方法:

将附件里面的“auto_create_device.il.il”放到cadenceSPB_16.6sharelocalpcbskill目录下,用记事本打开cadenceSPB_16.6sharelocalpcbskill目录下的allegro.ilinit文件,(如果没有这个文件就自己新建一个txt文本文档,然后将文件名称和后缀修改为allegro.ilinit即可),在里面独立一行添加一行代码:load("auto_create_device.il.il"),然后保存文件,再重启软件即可!

4、指定库路径:将下图的三个库路径指定到封装库路径下。

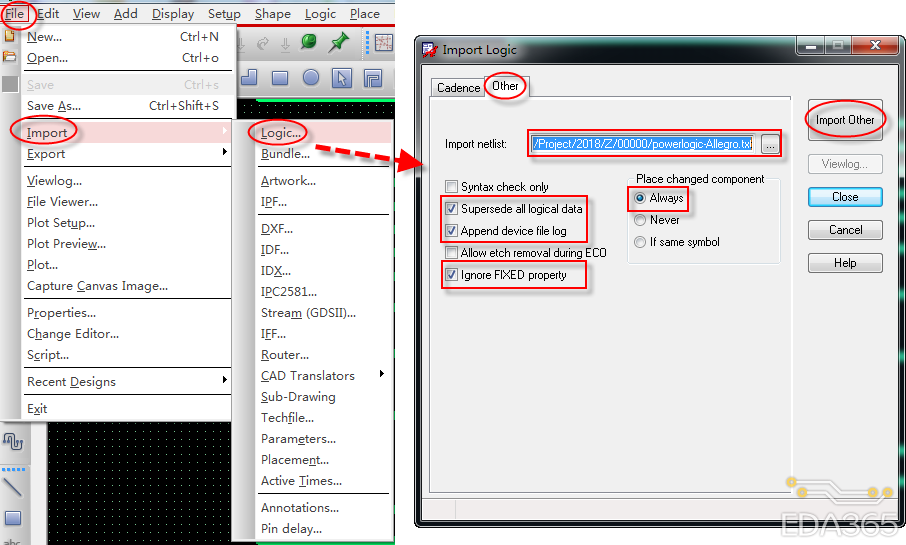

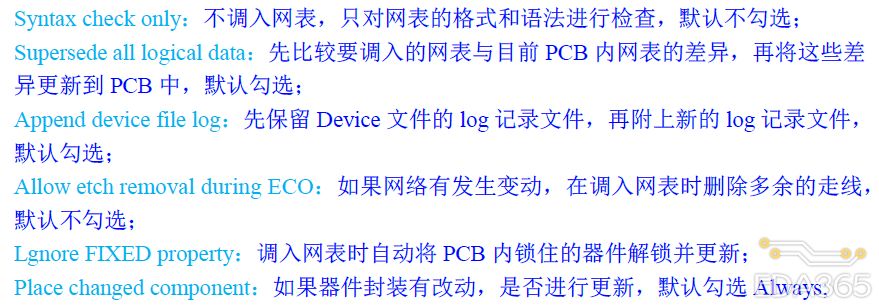

5、导入转换后的第三方网表:按照下图选择转换后的网表文件,并按下图勾选对应的选项,然后导入即可。 如有报错则根据当前目录下生成的netin.log报表查找关键词“error”,并根据error提示解决问题即可。

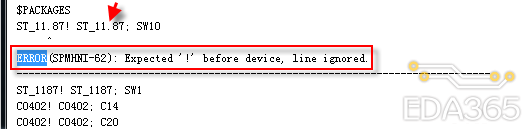

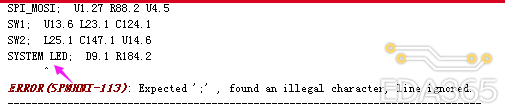

与第一方网表调入相比,第三方网表调入报错的问题都比较清晰易懂,不难解决,以下是第三方网表调入报错的一些常见问题类型和解决方法:A. 原理图封装名称中带有非法字符(如小数点、空格、@、#、¥、%、&、*、(、)、+等)。

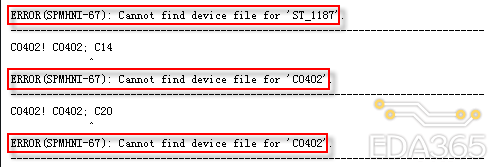

解决方法:根据提示的位号和封装名称将原理图上对应器件的封装名称中的非法字符统一修改为下滑杠。B. 所有封装都有了,但是导入还是报错:没有指定库路径。

解决方法:导入前先将devpath、padpath和psmpath三个库路径设置到封装库所在的目录,再导入网表。C. 所有封装都有了,库路径也指定了,但导入也还报错:器件的封装没有生成device文件。解决方法:先将封装库生成device文件后再导入。D. 库路径里面带有非法字符,软件无法识别库路径。解决方法:将文件目录里面的非法字符改掉。E. PCB封装名称中带有非法字符,造成PCB封装名称与原理图器件封装名称对不上。解决方法:将PCB封装名称修改为原理图器件封装的名称,与之对应。

注意:C、D、E的报错类型提示跟B是一样的。

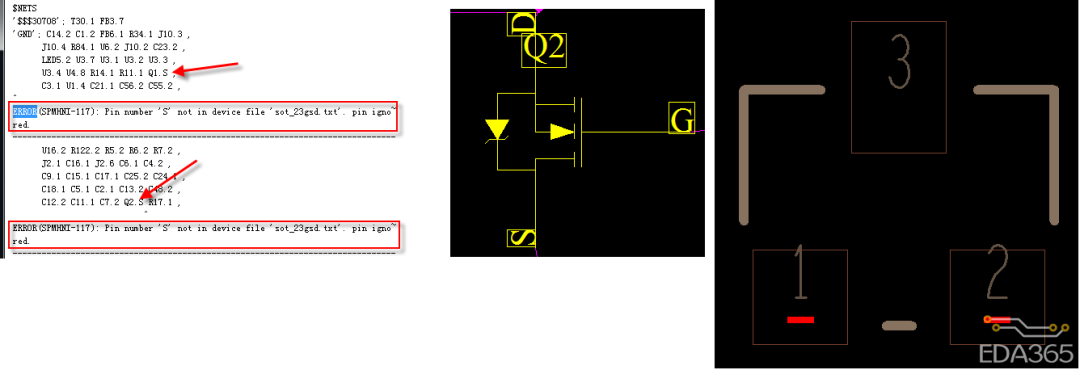

F. PCB封装的pin number与原理图器件的pin number不匹配(原理图三极管使用的pin number是:GSD ,而PCB封装是:123)。

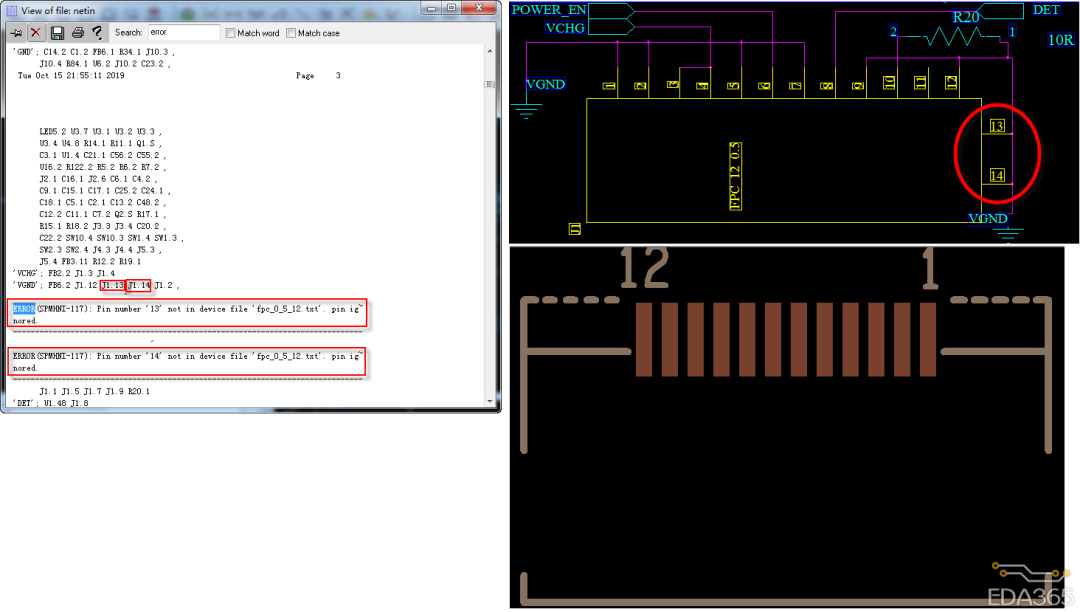

解决方法:修改原理图或PCB封装,使其pin number对应即可。G. PCB封装的pin管脚比原理图的少(如下图原理图多了13和14两个固定脚,而PCB封装则没有)。

解决方法:检查对应的封装管脚,如少了则给PCB封装加上。H. 原理图网络名称带有空格。

解决方法:将原理图上带有空格的网络名称中的空格去掉或修改为下滑杆。 以上为常见的第三方网表导入报错问题,可以根据问题报错提示进行排查。 另外,有时候由于AD或PADS原理图封装命名的不规范性造成网表里面带有大量非法字符,修改原理图太麻烦的话可以转换网表后在第三方网表里面进行字符替换。 然后保存后再导入,不过这样每次更新网表都得这样替换一次,比较麻烦,建议有时间最好修改下原理图与PCB对应比较好,这样后续更新网表就可以转换后直接导入了,而不需要每一次都要替换非法字符。

注意:第三方网表调入与第一方网表调入的区别:

1、第三方网表导入是需要器件的device文件的,如果没有device文件是导入不了的,库路径里面的devpath也必须指定。

2、必须先解决所有的报错问题才能成功导入;

3、第三方网表调入的PCB是不支持与Orcad原理图直接交互的;

4、文件名称和路径中不要使用非法字符。Allegro中所说的非法字符就是除了数字、字母、中杆和下滑杆以外的其它所有字符,包括空格。

Allegro有些操作是不支持非法字符的,乱用非法字符有时候就是这么一个不起眼的坏习惯都能折腾你半天时间还找不到问题所在,养成良好的设计习惯能让你少走弯路。

-

原理图

+关注

关注

1357文章

6431浏览量

247716 -

封装

+关注

关注

128文章

9374浏览量

149182 -

PCB设计

+关注

关注

396文章

4944浏览量

96043 -

allegro

+关注

关注

42文章

775浏览量

150676 -

可制造性设计

+关注

关注

10文章

2066浏览量

16548 -

华秋DFM

+关注

关注

20文章

3516浏览量

6620 -

可制造性设计分析

+关注

关注

4文章

866浏览量

6491

原文标题:教你如何将 AD 或 PADS 的原理图导入 Allegro 做 Layout

文章出处:【微信号:eda365wx,微信公众号:EDA365电子论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

03. 如何把 PCB 板上的线变成铜皮?| 芯巧Allegro PCB 设计小诀窍

KiCad 10 探秘(三):引入三大全新导入器:Allegro、PADS 与 gEDA

【产品介绍】PADS软件

如何将 GPIO PWM 和 GPIO Capture 驱动程序导入 Linux 内核,实现 PWM 输出并检测引脚的变化状态?

AD、Allegro、Pads的快捷键有什么不同

Allegro更新原理图导入网表后,Xnet混乱何解?

KiCad 已支持导入 Altium 工程(Project)

Allegro Skill字符功能之导入LOGO

如何将AD或PADS的原理图导入Allegro做Layout

如何将AD或PADS的原理图导入Allegro做Layout

评论