通常我们在layout时完成所有的布线工作后,会在PCB上闲置的空间作为基准面进行铺铜处理。这是几乎所有的PCB工程师都知道的一个常识,却很少有人能够说出其中具体的意义。如果有面试问到或者笔试环节有这样的问题:PCB中铺铜的好处有哪些?大概可以这么回答:

1.数字电路中存在大量尖峰脉冲电流,而地网络的干扰能量U=I*R,因此降低地线阻抗尤为重要。所谓抗干扰有很大一部分是通过降低地线阻抗实现的,因此大量的铺铜或者完整的地平面能够降低地线阻抗,从而增强系统的抗干扰能力;

2.对于电源来说,其传输路径包括电源路径和回流路径地,整个传输路径的压降U=I*R,该路径上的直流电阻R越低,压降就越低。因此大量的铺铜能够降低电源传输路径上的直流电阻,从而降低其压降,提高电源的传输效率。

3.对于电源的回流来说,地线和铺铜相连,能让电源最大限度的找到一个最短的回流路径,从而减小电源回路面积,提高系统的抗干扰能力。

4.通过铺地对重要信号和高速信号进行保护和隔离。

5.铜皮是能够传播热量的,大量的铺地铜皮结合地过孔,能大大的改善系统的散热。芯片热焊盘的处理就是一个很好的通过铜皮和过孔散热的体现。

对于数字系统,理论上铜皮铺的越多,对地线的阻抗,直流电阻,电源回路,散热等的作用越有利。但是,往往一个多层板会有多个地平面,这些个地平面应该足够满足这些阻抗,电阻,回路,散热等问题...那信号层空余地方的铜到底铺or不铺?不铺,好像关系也不大;铺,又浪费时间,好纠结...

其实以上针对铺铜的意义都是基于电气性能的考虑,从工艺的角度来说,为了保证电镀效果,或者层压不变形,在走线层空白地方也是要进行铺铜的。我们以层压为例。

压合厚度的计算说明:

1,厚度=单张pp理论厚度-填胶损失

2,填胶损失=(1-A面内层铜箔残铜率)X内层铜箔厚度+(1-B面内层铜箔残铜率)X内层铜箔厚度

3,内层残铜率=内层走线面积/整板面积

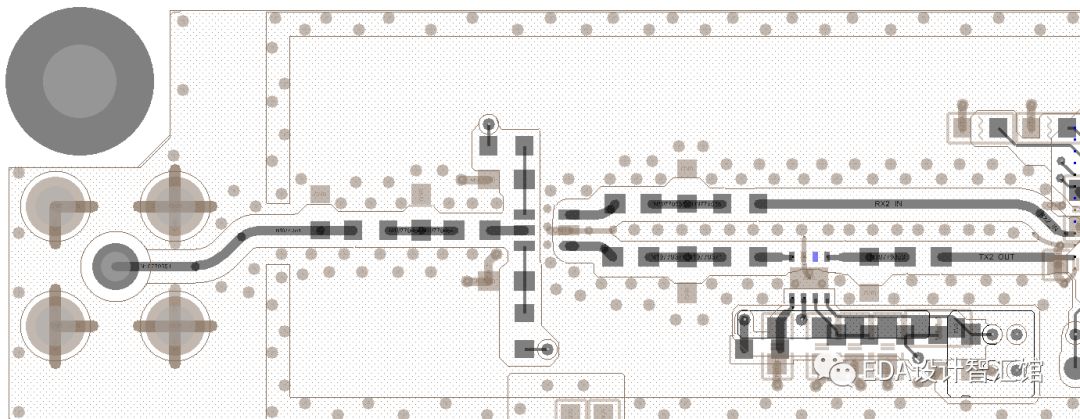

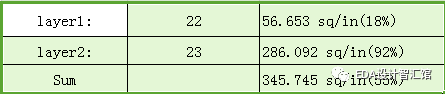

上图两个内层的残铜率如下表格所示注:Sq/in是面积单位,平方英尺

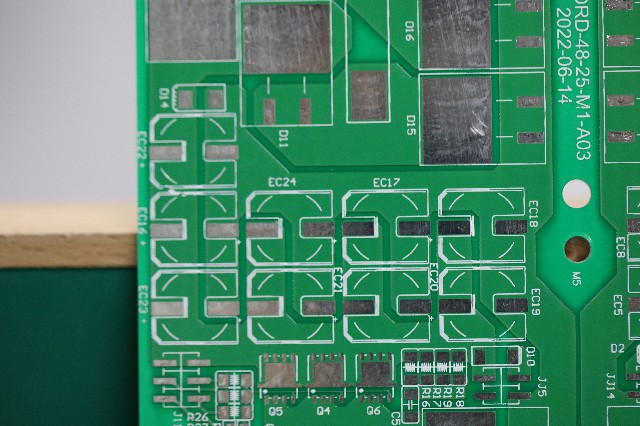

理论的层压厚度都是基于百分之一百的残铜率进行计算的,但是如果走线层的走线比较少,并且没有铺铜,那么该走线层的残铜率会比较小,最终的压合厚度就偏离理论厚度的值就会越大。我们以一个四层板为例,来看下实际的层压厚度该如何计算。

层叠结构说明:

1.半盎司铜厚=0.7mil

2.Pp压合厚度=100%残铜压合厚度-内层铜箔(1-残铜率)

3.内层core要确认内层芯板厚度是含铜厚还是不含铜厚,若不含铜厚则要算上内层铜箔的厚度

4.Pp压合厚度=100%残铜压合厚度-内层铜箔(1-残铜率)

5.半盎司铜厚=0.7mil

中间的Core(芯板)压合结构为39.4mil(含铜厚),外层铜厚为半盎司,pp为用7628RC50%,厂商提供该种pp100%残铜压合厚度为4.5mil。

从已知条件可以得出:

1.外层铜厚为半盎司:即Hoz=0.7mil,外层有两层即1.4mil

2.所用芯板为39.4mil(含铜厚):即芯板厚度为39.4mil(因为内层铜厚已包含在39.4mil中故内层铜箔厚度不用再计算);

3.假设一内层铜面积为80%,即内层残铜率为80%,另一层铜面积为70%

4.内层为1盎司铜厚即1.38mil

Pp压合厚度=4.5-1.38*(1-80%)=4.5-1.38*0.2=4.5-0.276=4.224

Pp压合厚度=4.5-1.38*(1-70%)=4.5-1.38*0.3=4.5-0.414=4.086

则压合后的厚度=0.7+4.224+39.4+4.086+0.7=49.11mil=1.25mm

假设39.4mil是不含铜厚的芯板,则要将两层内层的铜厚加入压合厚度中。

则压合后的厚度=0.7+4.224+1.38+39.4+1.38+4.086=51.87mil=1.32mm。

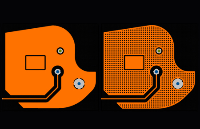

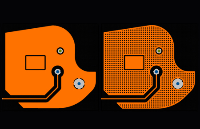

所以,为了层压不变形或者让我们的理论计算包括阻抗计算和板厚计算尽可能的接近实际成品值,应该让内层的走线残铜率接近百分之一百。那空白的地方还是把铜铺上吧。

-

pcb

+关注

关注

4338文章

23280浏览量

402971 -

数字电路

+关注

关注

193文章

1635浏览量

81168 -

铺铜

+关注

关注

2文章

35浏览量

19689

原文标题:层板的内层信号层铺铜or不铺铜?

文章出处:【微信号:PCBTech,微信公众号:EDA设计智汇馆】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

PCB设计中填充铜和网格铜有什么区别?(更新版)

PCB设计中填充铜和网格铜有什么区别?

PCB设计中填充铜和网格铜有什么区别?

PCB设计中填充铜和网格铜究竟有什么区别?

深度解析:PCB死铜问题的根源与处理方法

PCB设计有必要去掉死铜吗?死铜能带来什么问题?

浅谈PCB设计中铺铜的必要性

PCB中铺铜的好处有哪些?

PCB中铺铜的好处有哪些?

评论