结合排查之前pio_writeReadBack_test0测试出现的问题,需要参考前人写的相关博客,大部分都是基于BMD64,而我的示例是基于BMD128。

pio_writeReadBack_test0测试HOST发起一个MEM32写,然后再启动MEM32读回,所以先要探究MEM32写,分析BMD RX 引擎(用于接收、解析TLP)。下图是https://blog.csdn.net/ningjinghai11/article/details/80924209博文中给出的BMD64模式下的MEM32写时序仿真图,可以看到存储器写请求TLP有2个,所以相应的bmd_64_rx_state分别有MEM_WR32_QW1和MEM_WR32_WT两个状态对应。

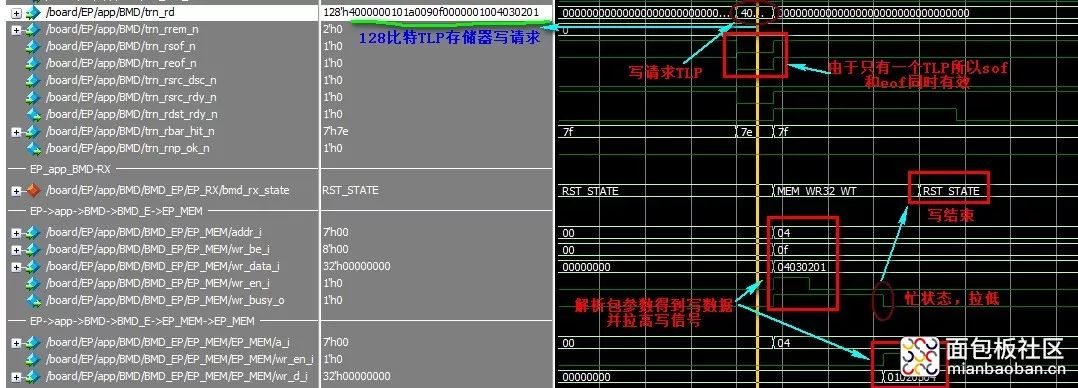

而我在仿真BMD128模式时,由于数据位宽为128bit,所以存储器写只有一个128bit的TLP就足够,而bmd_rx_state只一个MEM_WR32_WT就结束并进入RST状态,具体时序图如下:

(注:BMD_MEM_RD32_FMT_TYPE 和BMD_MEM_WR32_FMT_TYPE 两种标头对应的TLP是以PIO的模式传输,所以只会传输一个DW数据,再加上3DW标头;所以在BMD64模式下,一共两帧数据,而在上一个状态已经传输了一帧,本状态传输最后一帧数据,所以需要判断trn_reof_n 帧结束信号,同样需要主、从设备都准备好,即trn_rsrc_rdy_n 和trn_rdst_rdy_n 同时有效才能传输。而在BMD128模式下,只需一帧数据就足够了。这可以从上面两个时序图中可以清晰看出来。)

下面比较下BMD64和BMD128的RX引擎中对几个状态机的定义。

先来看看BMD64:

//接收引擎关键状态机的8个状态 `define BMD_64_RX_RST 8'b00000001//接收引擎复位状态 `define BMD_64_RX_MEM_RD32_QW1 8'b00000010//存储器读状态 `define BMD_64_RX_MEM_RD32_WT 8'b00000100//等待存储器读结束 `define BMD_64_RX_MEM_WR32_QW1 8'b00001000//存储器写状态 `define BMD_64_RX_MEM_WR32_WT 8'b00010000//等待存储器写结束 `define BMD_64_RX_CPL_QW1 8'b00100000//不带数据的完成 `define BMD_64_RX_CPLD_QW1 8'b01000000//带数据完成 `define BMD_64_RX_CPLD_QWN 8'b10000000//带数据完成 //接收引擎4种标头 `define BMD_MEM_RD32_FMT_TYPE 7'b00_00000//存储器读请求:TLP头大小为3个双字,不带数据 `define BMD_MEM_WR32_FMT_TYPE 7'b10_00000//存储器写请求:TLP头大小为3个双字,带数据 `define BMD_CPL_FMT_TYPE 7'b00_01010//完成报文:TLP头大小为3个双字,不带数据;包括存储器、配置和I/O写完成 `define BMD_CPLD_FMT_TYPE 7'b10_01010//带数据完成报文:TLP头大小为3个双字;包括存储器读、配置读、I/O读和原子读操作完成先来看看BMD128:

//定义了8种关键状态机状态 `define BMD_128_RX_RST 8'b00000001 `define BMD_128_RX_MEM_RD32_STRAD 8'b00000010 `define BMD_128_RX_MEM_RD32_WT 8'b00000100 `define BMD_128_RX_MEM_WR32_STRAD 8'b00001000 `define BMD_128_RX_MEM_WR32_WT 8'b00010000 `define BMD_128_RX_CPL_STRAD 8'b00100000 `define BMD_128_RX_CPLD_STRAD 8'b01000000 `define BMD_128_RX_CPLD_QWN 8'b10000000 //定义了4种标头 `define BMD_MEM_RD32_FMT_TYPE 7'b00_00000 `define BMD_MEM_WR32_FMT_TYPE 7'b10_00000 `define BMD_CPL_FMT_TYPE 7'b00_01010 `define BMD_CPLD_FMT_TYPE 7'b10_01010

-

FPGA

+关注

关注

1664文章

22545浏览量

640420 -

存储器

+关注

关注

39文章

7768浏览量

172386

原文标题:FPGA图文笔记:BMD64与BMD128比较

文章出处:【微信号:gh_bee81f890fc1,微信公众号:面包板社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

2.7寸单色128x64 OLED显示模块使用指南

探秘MCF51JM128 ColdFire微控制器:功能、特性与电气参数详解

深入解析MCF51JF128:功能特性与设计要点

深入剖析Freescale MC9S08JE128系列MCU:高效节能的理想之选

深入剖析ATxmega128A1U/ATxmega64A1U:特性、应用与设计要点

Atmel ATxmega128B3/ATxmega64B3微控制器:高性能之选

AT90CAN32/64/128:高性能8位微控制器的深度剖析

AT90CAN32/64/128:高性能8位微控制器的技术剖析

深入剖析Atmel AT90USB64/128微控制器:特性、应用与挑战

Atmel AVR ATUC64/128/256L3/4U微控制器:高性能与低功耗的完美结合

深入解析Microchip 25AA128/25LC128 128K SPI总线串行EEPROM

NVIDIA Omniverse USD插件开发中的UI卡顿问题复现及分析

W25Q128JVSIM与GD25Q128ESIGR引脚兼容分析

BMD64与BMD128比较

BMD64与BMD128比较

评论