日前,在斯坦福大学举行的IEEE Hot Chips研讨会上,创业公司Cerebras推出了有史以来最大的芯片。按照他们的说法,这个大致是硅晶片尺寸的系统旨在将AI训练时间从几个月缩短到几分钟。

这是自二十世纪八十年代Trilogy Systems任务失败以来,业界再一次出现对晶圆级处理器的商业尝试。

下面,我们来谈一下有关这个芯片,你必须知道的六点::

数据

作为有史以来最大的芯片,Cerebras的Wafer Scale Engine(WSE)自然带有一堆最高级的。这是当中的一部分:

尺寸:46,225平方毫米。这大约是一张信纸大小的纸张的75%,但却是最大GPU的56倍。

晶体管:1.2万亿。Nvidia的GV100 Volta仅为21亿。

处理器核心:400,000。而GV100只有5,660。

内存:18千兆字节的片上SRAM,大约是GV100的3000倍。

内存带宽:每秒9 PB。据Cerebras称,这是我们最喜欢的GPU的10,000倍。

你为什么需要这个怪物?

Cerebras在其白皮书中提出了一个非常好的案例,为什么这么大的芯片有意义。

基本上,该公司认为,训练深度学习系统和其他人工智能系统的需求已经失控。该公司表示,训练将出现一种新模式——创建一个这样的系统,那就是一旦经过训练,就可以识别人或赢得Go游戏。但这在过去需要花费数周或数月的时间,并耗费数十万美元的计算时间。这个成本意味着实验的空间很小,这会扼杀新的想法和创新。

这家公司的答案是,全世界需要更多,更便宜的训练计算资源。而训练也需要几分钟而不是几个月,为此,您需要更多内核,更多靠近这些内核的内存,以及内核之间的低延迟,高带宽连接。

这些目标将对AI行业中的每个人造成影响。但是Cerebras也承认,这个想法推向了它的逻辑极端。一块大芯片为处理器内核和需要依赖它的内存提供了更多的硅片面积。只有当数据永远不必离开芯片上的短而密集的互连时,才能实现高带宽,低延迟的连接。因此这也是他们打造这样一个大芯片的原因。

在这400,000个内核中有什么?

根据该公司的说法,WSE的内核专门用于人工智能,但仍然具有可编程性,那就意味着该芯片并不会仅仅被限定在AI当中。这就是他们所谓的稀疏线性代数(Sparse Linear Algebra:SLA)核心。这些处理单元专门用于“人工智能”工作的“张量”操作,但它们还包括一项减少工作的功能,特别是对于深度学习网络。据该公司称,深度学习训练集中所有数据的50%至98%为zero。因此,非零数据“Sparse ”。

SLA核心通过简单地不将任何东西乘以零来减少工作量。内核具有内置的数据流元素,可以根据数据触发计算操作,因此当数据遇到零时,不会浪费时间。

他们是怎么做到的?

Cerebras庞大的单芯片背后的基本理念已经存在了几十年,但它也是不切实际的。

早在20世纪80年代,并行计算的先驱 Gene Amdahl就制定了加速大型机计算的计划——硅片大小的处理器。换句话说,就是将大部分数据保留在处理器本身而不是将其通过电路板推送到存储器和其他芯片。这样的计算将更快且更节能。

借助从风险投资家手上拿到的2.3亿美金,Amdahl创立了Trilogy Systems,并实现了他的愿望。但我们不得不承认,“晶圆级整合”的第一次商业尝试是一场灾难,据当时报道,它成功地将动词“to crater”引入金融新闻词典。

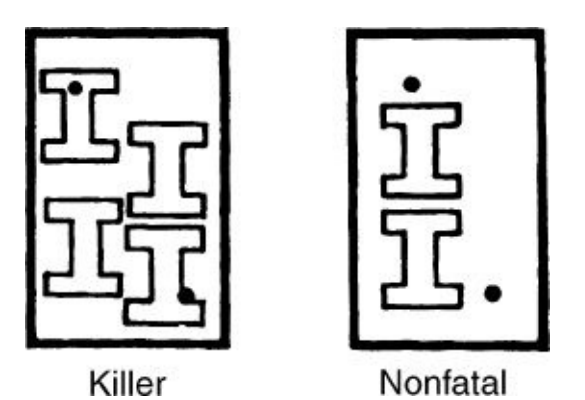

最基本的问题是芯片越大,良率越差。从逻辑上讲,这应该意味着晶圆级芯片将无利可图,因为您的产品总会存在缺陷。Cerebras的解决方案是添加一定量的冗余。据EE Times称,Swarm通信网络具有冗余链路,让产品工作时可以绕过受损核心。据透露,当中大约有1%的核心是备用的。

Cerebras还必须解决一些关键的制造限制问题。例如,芯片工具设计用于将其特征定义图案投射到相对较小的矩形上,并在晶圆上完美地反复进行。由于在晶片上的不同位置铸造不同图案的成本和难度,仅此一点就会使许多系统不能构建在单个晶片上。

但WSE就像一个典型的晶圆,完全由相同的芯片组成,就像你通常制造的一样。最大的不同之处在于他们与台积电合作开发了一种方法,用于在芯片之间的空间建立连接,这个区域称为scribe lines。而这个空间通常留空,因为芯片沿着那些线切割。

根据Tech Crunch的说法,Cerebras还必须发明一种方法,为芯片提供15千瓦的电源和冷却系统,并创造新的连接器,以便在加热时处理它扩展的方式。

这是制作晶圆级计算机的唯一方法吗?

当然不是。例如,加利福尼亚大学洛杉矶分校和 Illinois Urbana-Champaign的团队正在研究一种类似的系统,该系统也构建了裸处理器并进行了测试,并将它们安装在已经图案化所需的密集互连网络的硅片上。这种称为硅互连结构的概念允许这些小芯片紧密相连(相隔100微米),这就使得芯片间通信接近单个芯片的特性。

“这是我们一直在进行验证的研究”,伊利诺伊大学的 Rakesh Kumar说。

Kumar认为硅互连结构方法与Cerebras的单片晶圆级方案相比具有一些优势。首先,它允许设计师混合和匹配技术,并为每个技术使用最佳制造工艺。单片方法意味着为最关键的子系统逻辑选择最佳的制程,并将其用于存储器和其他原件,即使不适合它们。

Kumar建议,在这种方法中,Cerebras可以限制它可以放在处理器上的内存量。“他们在晶圆上有18千兆位的SRAM。也许这对今天的某些型号来说已经足够了,但明天和后天的型号呢?“

什么时候出来?

据“财富”杂志报道,Cerebras9月份将会向客户发货首批系统。据EE Times称,部分系统已经收到原型。该公司计划在11月的超级计算大会上公布完整系统的结果。

-

处理器

+关注

关注

68文章

19506浏览量

231667 -

芯片

+关注

关注

458文章

51478浏览量

429171 -

晶体管

+关注

关注

77文章

9823浏览量

139294

原文标题:对于这颗有史以来最大的芯片,这六点你需要知道!

文章出处:【微信号:icbank,微信公众号:icbank】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

AMC1210对AMC1305进行数字抽取滤波,输出后的数据是否需要用处理器进行一次平均和移位处理?

盛显科技:投影融合处理器连接出现超时,该怎么办?

碳化硅晶圆和硅晶圆的区别是什么

一次消谐器的构造

英特尔二季度对酷睿Ultra处理器供应受限

隆基再一次蝉联PV Tech组件可融资性最高评级

业界再一次出现对晶圆级处理器的商业尝试

业界再一次出现对晶圆级处理器的商业尝试

评论