本应用说明旨在帮助用户利用能够实现优良 RF 性能的设计实践,设计 EFR32 Wireless Gecko Series 2产品组合的PCB。

匹配原则载于应用说明 AN930.2:EFR32 Series 2 2.4 GHz匹配指南。以下应用说明详细介绍了MCU 相关的主题:AN0918.2:Wireless Gecko Series 1 至Series 2 兼容性和迁移指南,AN0948:电源配置和 DC-DC 以及 AN0955:CRYPTO。

Silicon Labs MCU 和无线入门套件以及 Simplicity Studio 提供强大的开发和调试环境。为利用自定义硬件的功能和特性,Silicon Labs 推荐在自定义硬件设计中包含调试和编程接口连接器。有关包含这些连接器接口的详细信息和优点在 AN958:自定义设计的调试和编程接口中有详细阐述。

EFR32 的电源配置载于 AN0002.2:EFR32 Wireless Gecko Series 2 硬件设计注意事项。RF 性能很大程度上依赖于 PCB 布局以及匹配网络的设计。

此应用指南支持以下EFR32 Series 2设备:

EFR32Mighty Gecko (EFR32MG21)

EFR32 BlueGecko (EFR32BG21)

为实现最佳性能,Silicon Labs 建议使用下列部分所述的 PCB 布局设计指南。

内容要点

提供参考示意图和 PCB 布局

列出并描述所有主要设计原则

提供所有设计原则的摘要对照表

免费下载中文版EFR32第二代无线平台布局设计指南:https://www.silabs.com/documents/public/application-notes/an928.2-efr32-series2-layout-design-guide-cn.pdf

EFR32第二代无线SoC平台的设计建议已使用 Silicon Labs 提供的参考设计完成广泛测试。建议设计者按原样使用参考设计,因为其能够尽可能减小寄生现象导致或不良元件布置和 PCB 排线产生的失谐作用。EFR32 参考设计文件位于Simplicity Studio 的“套件文档”选项卡下。

设计的紧凑型 RF 部分(不包括 50 Ω 单端天线)以蓝框圈出,强烈建议使用圈出的 RF 布局,以避免出现任何可能的失谐作用。下图显示了设计中圈出的紧凑型 RF 部分。

BRD4180A 无线电板的顶层(左侧)和 RF 部分的组装图(右侧)

MCU VDD 滤波电容的布局也应尽可能参照参考设计。如果布局无法遵循参考设计(由于 PCB 尺寸和形状限制),建议采用下列部分所述的布局设计规则。

EFR32第二代无线SoC平台的布局设计指南设计 RF 相关布局以实现优良 RF 性能的一般指南如下:

对于自定义设计,请尽可能使用与参考设计相同数量的 PCB 层。与参考PCB 层数出现偏差会导致不同的 PCB 寄生电容,无法实现匹配网络的最佳形态。如果需要层数与参考设计不同的设计,请确保顶层和内部第一层之间的距离与参考设计相似,因为这个距离决定了接地的寄生电容值。否则可能会出现匹配网络失调,可能需要微调元件值。

请使用尽可能连续和统一的接地层金属,特别是顶层和底层。

避免接地层金属分离,尤其是在匹配网络的底层和 RFIC GND 引脚/裸焊盘之间。

请使用尽可能多的接地孔(尤其是在 GND 引脚附近),以尽可能降低不同层的接地灌流和 GND 引脚之间的串联寄生电感。

请沿 PCB 边缘和内部 GND 金属灌流边缘使用一系列 GND 针脚孔。孔之间的最大距离应小于第 10 次谐波的 Lambda/10(参考无线电板上孔之间的距离一般为 40–50 mil)。该距离能够在这些边缘的弥散场造成的高谐波下降低 PCB 辐射。

对于两层以上的设计,建议在内层放置尽可能多的走线(甚至是数字走线),确保顶层和底层有大规模的连续 GND 灌流。

避免使用长和/或薄的传输线连接与 RF 相关的元件。否则由于分布式寄生电感,可能发生某些失谐作用。此外,请尽可能缩短互连线,降低接地的并联寄生电容。但是,相邻分立元件的偶联可能会增加。

在不同宽度(即不同阻抗)的传输线之间使用递变线路,以减少内部反射。

避免使用回路和长线,以消除共振。它们还可用作不良辐射体,尤其是在谐波上。

请使用一些旁路电容确保优良的 VDD 滤波(尤其是工作频率范围)。电容的串联自谐应靠近滤波频率。过滤最高频率的旁路电容应最接近 EFR32 的 VDD 引脚。除基础频率外,应过滤晶体/时钟频率及其谐波(最高3次),以避免向上变频激励。

使用多个孔将晶体壳接地,避免未接地部件的辐射。请勿断开和悬空任何可能是不良辐射体的金属。请避免引导电源走线靠近晶体或在晶体下方,或者与晶体信号或时钟走线并联。

请避免 GPIO 线路靠近 RF 线、天线或晶体或在其下方,或者与晶体信号并联。请使用 GPIO 线上尽可能最低的偏差率,降低对 RF 或晶体信号的串扰。

请使用尽可能短的 VDD 走线。VDD 走线可以是隐藏的不良辐射体,以便尽可能简化 VDD 布线,并使用带有很多针脚孔的大规模连续 GND 灌流。要简化 VDD 布线,请尽量避免 VDD 走线的星形拓扑(即避免连接一个通用点中的所有 VDD 走线)。

在天线附近使用丝网会对天线的绝缘环境造成轻微的影响。尽管这一影响通常可以忽略,但是请尽量避免在天线或天线灌流遮挡区使用丝网。

基于 BRD4180A 20 dBm 无线电板的 2.4 GHz EFR32 Series2 无线平台布局该部分中显示的示例基于20 dBm BRD4180A无线电板的布局。主布局设计概念与此布局一同显示,用于展示基本原理。尽管这些规则将通过使用5元素匹配的设计显示,但是类似的设计实践也应通过 3 元素匹配网络进行应用。BRD4180A无线电板的 RF 部分布局结构示意图如下。

BRD4180A无线电板的 RF 部分布局(顶层)

-

电源

+关注

关注

185文章

17953浏览量

252753 -

pcb

+关注

关注

4333文章

23223浏览量

401854 -

连接器

+关注

关注

98文章

14824浏览量

137779

原文标题:【应用指南】EFR32第二代无线平台布局设计技巧

文章出处:【微信号:SiliconLabs,微信公众号:Silicon Labs】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

简单认识第二代高通3D Sonic传感器

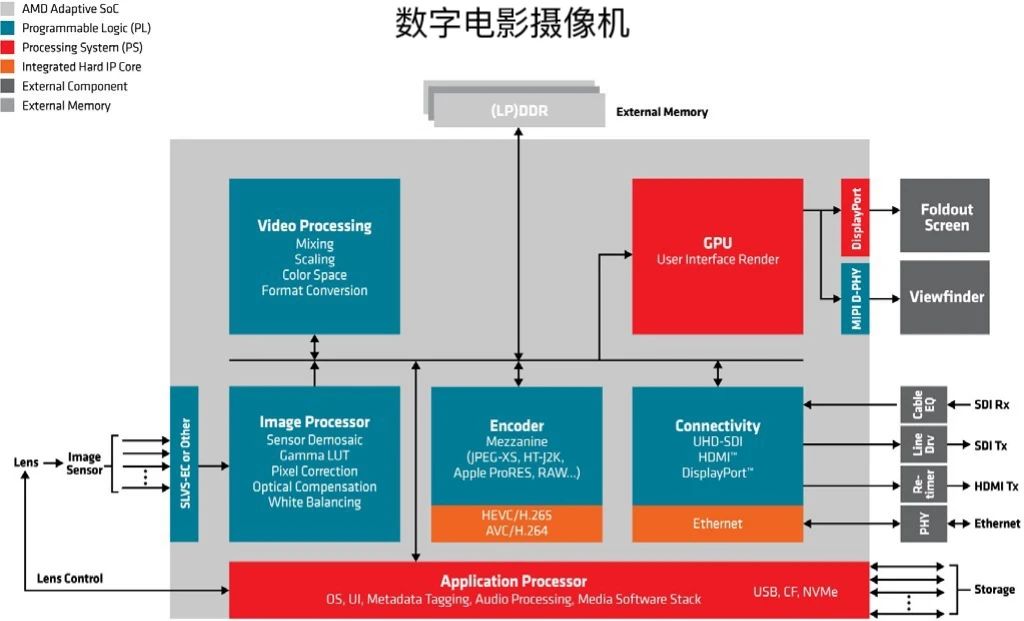

第二代AMD Versal Premium系列器件的主要应用

第二代AMD Versal Premium系列产品亮点

简单认识高通第二代骁龙XR2+平台

简单认识第二代高通Oryon CPU

AMD推出第二代Versal Premium系列

AYANEO Pocket EVO搭载第二代骁龙G3x游戏平台

一加正式发布第二代东方屏,获全球首个DisplayMate A++认证

第二代AMD Versal Prime系列自适应SoC的亮点

EFR32第二代无线平台布局设计技巧

EFR32第二代无线平台布局设计技巧

评论