前言

很多人第一次接触Altera Cyclone系列FPGA的时候,可能会被其复杂的专用管脚给搞混淆,在这里我们Altera Cyclone系列FPGA的专用管脚一一列出供您参考,希望对您的设计有帮助。本文适用于Altera Cyclone III系列FPGA,对Cyclone II以及IV绝大部分的是适用的,但是个别的管脚,例如MSEL等不适用。具体到您的设计,还请您仔细查看您器件的Datasheet。

Altera Cyclone系列FPGA配置模式

Altera公司的Cyclone系列低端FPGA的特殊管脚基本都是用于配置用途,其支持以下几种配置模式:

Active parallel (AP) for Cyclone III devices only

Passive serial (PS)

Fast passive parallel (FPP)

Joint Test Action Group (JTAG)

在大部分设计中,出于成本以及节约IO的考虑采用的是串行FLASH-AS模式+JTAG。以下就是所用到的一些管脚的说明:

Altera Cyclone系列FPGA专用管脚说明

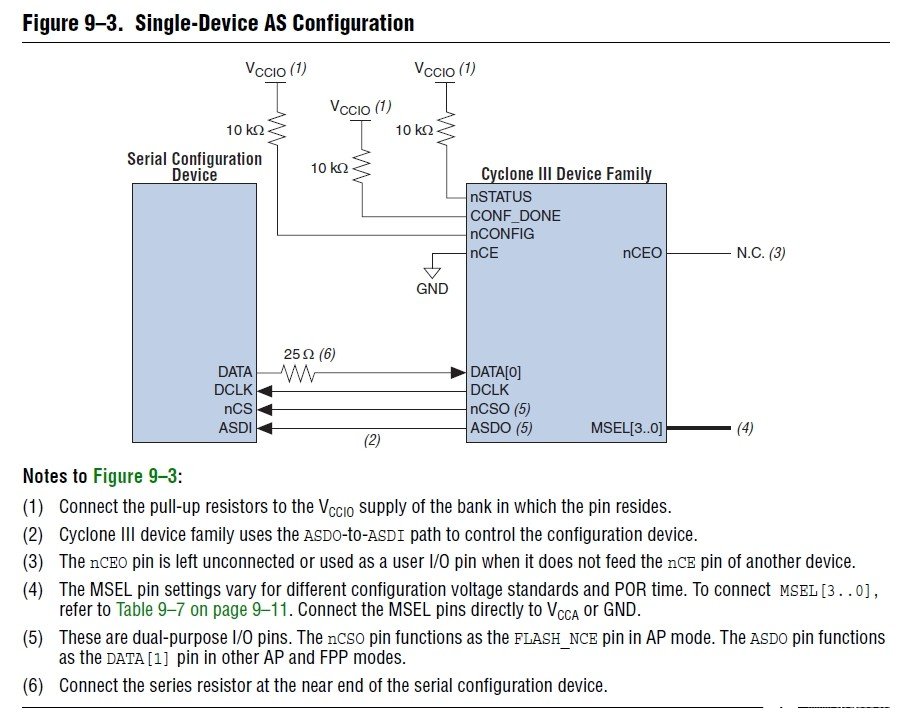

AS配置引脚接线图

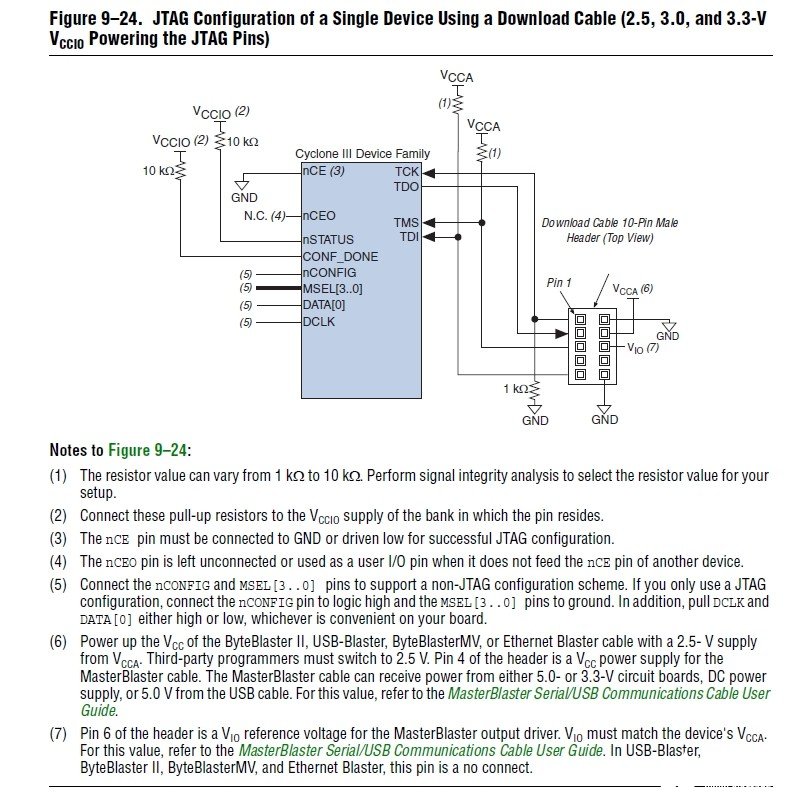

JTAG引脚接线图

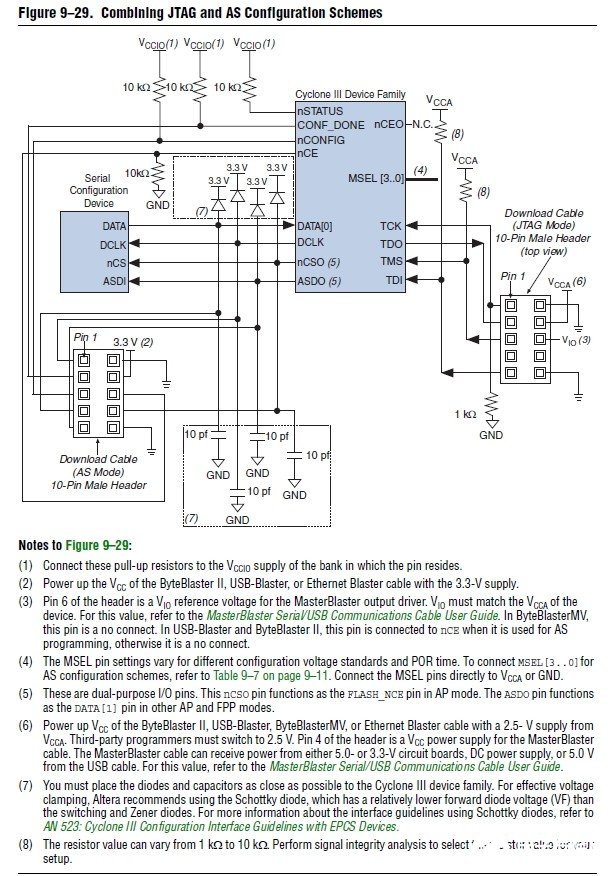

完整的JTAG+AS接线图

以下就是Altera Cyclone系列FPGA专用管脚说明:

1.I/O,nCSO

在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用。在AS 模式下,这个脚是CIII 用来给外面的串行配置芯片发送的使能脚。在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效。这个脚是低电平有效的。直接接到配置芯片的/CS 脚(第1脚)。

2.I/O, ASDO

在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用。在AS 模式下,这个脚是CIII 向串行配置芯片发送控制信号的脚。也是用来从配置芯片中读配置数据的脚。在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效,配置完成后,该脚就变成三态输入脚。ASDO 脚直接接到配置芯片的ASDI 脚(第5 脚)。

3.I/O,CRC_ERROR

当错误检测CRC 电路被选用时,这个脚就被作为CRC_ERROR 脚,如果不用默认就用来做I/O。但要注意,这个脚是不支持漏极开路和反向的。当它作为CRC_ERROR 时,高电平输出则表示出现了CRC 校验错误(在配置SRAM 各个比特时出现了错误)。CRC 电路的支持可以在setting 中加上。这个脚一般与nCONFIG 脚配合起来用。即如果配置过程出错,重新配置。

4.I/O,CLKUSR

当在软件中打开Enable

User-supplled start-up clock(CLKUSR)选项后,这个脚就只可以作为用户提供的初始化时钟输入脚。在所有配置数据都已经被接收后,CONF_DONE 脚会变成高电平,CIII 器件还需要299 个时钟周期来初始化寄存器,I/O 等等状态,FPGA 有两种方式,一种是用内部的晶振(10MHz),另一种就是从CLKUSR 接进来的时钟(最大不能超过100MHz)。有这个功能,可以延缓FPGA 开始工作的时间,可以在需要和其它器件进行同步的特殊应用中用到。

5.I/O,VREF

用来给某些差分标准提供一个参考电平。没有用到的话,可以当成I/O 来用。

6. DATA0

专用输入脚。在AS 模式下,配置的过程是:CIII 将nCSO 置低电平,配置芯片被使能。CIII然后通过DCLK 和ASDO 配合操作,发送操作的命令,以及读的地址给配置芯片。配置芯片然后通过DATA 脚给CIII 发送数据。DATA 脚就接到CIII 的DATA0 脚上。CII接收完所有的配置数据后,就会释放CONF_DONE 脚(即不强制使CONF_DONE 脚为低电平),CONF_DONE 脚是漏极开路(Open-Drain)的。这时候,因为CONF_DONE 在外部会接一个10K 的电阻,所以它会变成高电平。同时,CII 就停止DCLK 信号。在CONF_DONE 变成高电平以后(这时它又相当于变成一个输入脚),初始化的过程就开始了。所以,CONF_DONE 这个脚外面一定要接一个10K 的电阻,以保证初始化过程可以正确开始。 DATA0,DCLK,NCSO,ASDO 脚上都有微弱的上拉电阻,且一直有效。在配置完成后,这些脚都会变成输入三态,并被内部微弱的上拉电阻将电平置为高电平。在AS 模式下,DATA0就接到配置芯片的DATA(第2 脚)。主语,DATA0需要接一个25欧的电阻,用来减少过冲。

7. DCLK

PS 模式下是输入,AS 模式下是输出。在PS 模式下,DCLK 是一个时钟输入脚,是外部器件将配置数据传送给FPGA 的时钟。数据是在DCLK 的上升沿把数据,在AS 模式下,DCLK脚是一个时钟输出脚,就是提供一个配置时钟。直接接到配置芯片的DCLK 脚上去(第6脚)。无论是哪种配置模式,配置完成后,这个脚都会变成三态。如果外接的是配置器件,配置器件会置DCLK 脚为低电平。如果使用的是主控芯片,可以将DCLK 置高也可以将DCLK 置低。配置完成后,触发这个脚并不会影响已配置完的FPGA。这个脚带了输入Buffer,支持施密特触发器的磁滞功能。

8. nCE

专用输入脚。这个脚是一个低电平有效的片选使能信号。nCE 脚是配置使能脚。在配置,初始化以及用户模式下,nCE 脚必须置低。在多个器件的配置过程中,第一个器件的nCE 脚要置低,它的nCEO 要连接到下一个器件的nCE 脚上,形成了一个链。nCE脚在用JTAG编程模式下也需要将nCE 脚置低。 这个脚带了输入Buffer,支持施密特触发器的磁滞功能。

9. nCONFIG

专用的输入管脚。这个管脚是一个配置控制输入脚。如果这个脚在用户模式下被置低,FPGA就会丢失掉它的配置数据,并进入一个复位状态,并将所有的I/O 脚置成三态的。nCONFIG从低电平跳变到高电平的过程会初始化重配置的过程。如果配置方案采用增强型的配置器件或EPC2,用户可以将nCONFIG 脚直接接到VCC 或到配置芯片的nINIT_CONF 脚上去。这个脚带了输入Buffer,支持施密特触发器的磁滞功能。实际上,在用户模式下,nCONFIG信号就是用来初始化重配置的。当nCONFIG 脚被置低后,初始化进程就开始了。当nCONFIG脚被置低后,CIII 就被复位了,并进入了复位状态,nSTATUS 和CONF_DONE 脚被置低,所有的I/O脚进入三态。nCONFIG 信号必须至少保持2us。当nCONFIG 又回到高电平状态后,nSTATUS 又被释放。重配置就开始了。在实际应用过程中可以将nCONFIG 脚接一个10K 的上拉电阻到3.3V.

10. DEV_OE

I/O 脚或全局I/O 使能脚。在Quartus II 软件中可以使能DEV_OE 选项(Enable Device-wideoutput Enable),如果使能了这一个功能,这个脚可以当全局I/O 使能脚,这个脚的功能是,如果它被置低,所有的I/O 都进入三态。

11. INIT_DONE

I/O 脚或漏极开路的输出脚。当这个脚被使能后,该脚上从低到高的跳变指示FPGA 已经进入了用户模式。如果INIT_DONE 输出脚被使能,在配置完成以后,这个脚就不能被用做用户I/O 了。在QuartusII 里面可以通过使能Enable INIT_DONE 输出选项使能这个脚。

12. nCEO

I/O 脚或输出脚。当配置完成后,这个脚会输出低电平。在多个器件的配置过程中,这个脚会连接到下一个器件的nCE 脚,这个时候,它还需要在外面接一个10K 的上拉电阻到Vccio。多个器件的配置过程中,最后一个器件的nCEO 可以浮空。如果想把这个脚当成可用的I/O,需要在软件里面做一下设置。另外,就算是做I/O,也要等配置完成以后。

13. nSTATUS

这是一个专用的配置状态脚。双向脚,当它是输出脚时,是漏极开路的。在上电之后,FPGA立刻将nSTATUS 脚置成低电平,并在上电复位(POR)完成之后,释放它,将它置为高电平。作为状态输出脚时,在配置过程中如果有任何一个错误发生了,nSTATUS脚会被置低。作为状态输入脚时,在配置或初始化过程中,外部控制芯片可以将这个脚拉低,这时候FPGA就会进入错误状态。这个脚不能用作普通I/O 脚。nSTATUS 脚必须上拉一个10K 欧的电阻。

14. CONF_DONE

这是一个专用的配置状态脚。双向脚,当它是输出脚时,是漏极开路的。当作为状态输出脚时,在配置之前和过程中,它都被置为低电平。一旦配置数据接收完成,并且没有任何错误,初始化周期一开始,CONF_DONE 就会被释放。当作为状态输入脚时,在所有数据都被接收后,要将它置为高电平。之后器件就开始初始化再进入用户模式。它不可以用作普通I/O来用。这个脚外成也必须接一个10K 欧的电阻。

15. MSEL[3:0]

这些脚要接到GND或电源,表示高电平或低电平。AS模式分为快速和标准,此外,IO电源电压不同,MSEL也不尽相同, JTAG 模式跟MSEL 无关,即用JTAG模式,MSEL 会被忽略,一般3.3VAS模式采用0010。

16.DEV_CLRn

I/O 或全局的清零输入端。在QuartusII 里面,如果选上Enable Device-Wide Reset(DEV_CLRn)这个功能。这个脚就是全局清零端。当这个脚被置低,所有的寄存器都会被清零。这个脚不会影响到JTAG 的边界扫描或编程的操作。

-

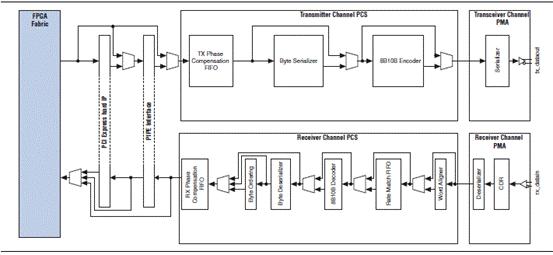

FPGA

+关注

关注

1629文章

21729浏览量

602968 -

Altera

+关注

关注

37文章

781浏览量

153919 -

串行

+关注

关注

0文章

237浏览量

33832

发布评论请先 登录

相关推荐

怎样为自己的设计选择Altera Cyclone V FPGA?

在高清晰LCD HDTV 中使用Cyclone III FPGA

什么是Altera系列低成本Cyclone IV FPGA?

MCU配置Altera-Cyclone系列FPGA的相关资料下载

开源硬件-TIDA-00604-采用 TPS65023 的 Altera Cyclone III FPGA 电源 PCB layout 设计

Altera Cyclone III HSMC视频方案

利用高级Cyclone III FPGA PLL,提高灵活性

Altium推出采用Altera Cyclone III F

Altium推出采用Altera Cyclone III的最

低功耗Cyclone IV FPGA

ETL-002 Altera Cyclone III系列FPGA开发板简介

Altera Cyclone IV GX系列FPGA开发方案

Altera Cyclone III系列FPGA开发板的库文件免费下载

Altera Cyclone III系列FPGA的专用管脚参考

Altera Cyclone III系列FPGA的专用管脚参考

评论