十多年来,半导体制造行业一方面一直在期待EUV能够拯救摩尔定律,但另一方面又担心该技术永远都不会出现。不过最终,它还是来了,而且不久便将投入使用。

摩尔定律渐远下的提升

半个多世纪以来,半导体行业按照摩尔定律不断发展,驱动了一系列的科技创新、社会改革以及生产效率的提高。

随着器件尺寸越来越逼近物理极限,摩尔定律对新一代工艺节点研发是否依然奏效是现在全行业都在关注的问题。

DRAM制程工艺进入20nm以后,由于制造难度越来越高,内存芯片制造厂商对工艺的定义已经不是具体的线宽。

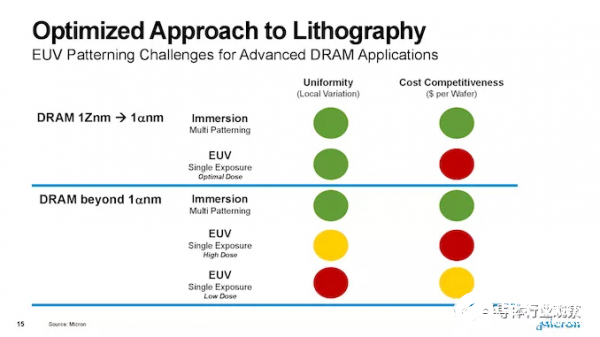

目前,行业DRAM三巨头都没有大规模使用EUV,但随着制程工艺的提升,节点的进一步微缩,同时,EUV的性能和成本也在不断优化,DRAM将迎来EUV爆发期。

DRAM制造商采用EUV的可能性极有可能与逻辑芯片制造商相似。最初,EUV设备仅用于几层,随着制程节点、层数逐渐增加,将全面转向EUV设备。

被称为“突破摩尔定律的救星”

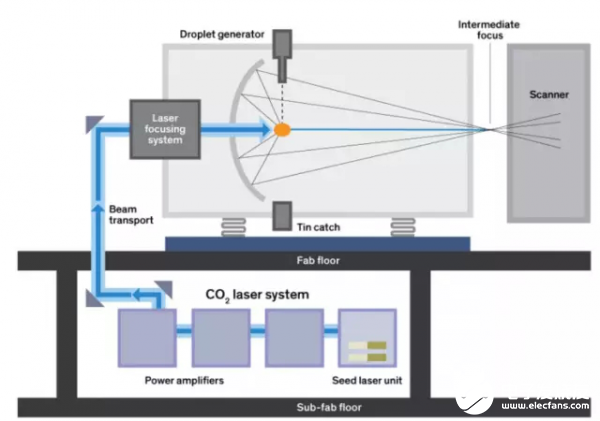

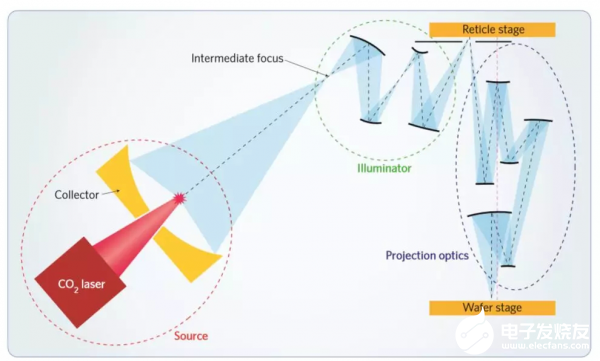

EUV 作为现在最先进的光刻机,是唯一能够生产 7nm 以下制程的设备,因为它发射的光线波长仅为现有设备的十五分之一,能够蚀刻更加精细的半导体电路,所以 EUV 也被成为“突破摩尔定律的救星”。

从2019年半导体芯片进入 7nm 时代开始(现在我们处于 10nm 时代),EUV 光刻机是绝对的战略性设备,没有它就会寸步难行。

而中芯国际斥巨资预定EUV设备,虽然技术落后三星、台积电两到三代,现在还在 28nm 和 14nm 上挣扎,但是拥有 EUV 光刻机之后,对于中国自主研发半导体技术是有着重大意义的。

光刻成为摩尔定律的前沿

在半导体产业中,由于不同种类芯片的晶体结构和工作模式存在差异,工艺发展进程也不尽相同。

在DRAM领域,全球三大DRAM原厂均停滞在18nm-15nm之间,仍没有突破10nm物理极限;在逻辑芯片制造领域,以台积电和三星为代表,已经引入EUV技术。

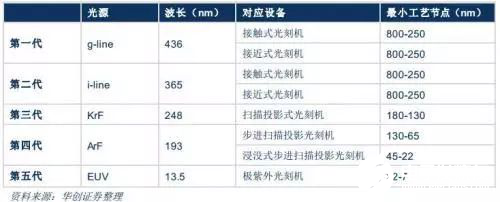

但在所有半导体产品制造中,都需要通过光刻技术将电路图形转移到单晶表面或介质层上,光刻技术的不断突破推动着集成电路密度、性能不断翻倍,成本也愈加优化。近年来,随着工艺节点的不断缩小,光刻技术主要经历了紫外光刻技术(UV)、深紫外光刻技术(DUV)和极紫外光刻技术(EUV)。

在EUV技术中,采用的光波长仅为13.5nm,因此能够将图案分辨率降低到10nm以下,这是目前主流的DUV技术无法达到的。

不过,因为晶片制程的持续推进,电路要再进行微缩的难度愈来愈高,成本的提升速度也愈来愈快。

EUV有足够的时间追赶

半导体厂商在步履艰难地减小线路尺寸的同时维持成本;每一代芯片成功流片的时间拉的更长;芯片工艺尺寸的减小也不像以往那样激进。这些困难可能会给 EUV 一个机会,摩尔定律的变缓可能真的会给EUV足够的时间迎头赶上。

足够的时间,也就是在摩尔定律被成本折磨到止步之前。EUV 可能会走到它被广泛接受而且能降低生产成本的那一天。到了那个时候,下一代的先进芯片的制造成本可能过高,而所带来的性能优势不够明显,以致于半导体厂商不会选择这种技术。

大厂对EUV的响应速度

EUV光刻机主要客户有英特尔、三星和台积电,而台积电的订单最多。存储方面DRAM的产量和工艺提升都需要用到EUV光刻机了, 而随着物联网的发展,相信也会给EUV设备带来增量。

光刻机领域的龙头老大是荷兰ASML,并已经占据了高达80%的市场份额,垄断了高端光刻机市场——最先进的EUV光刻机售价曾高达1亿美元一台,且全球仅仅ASML能够生产。

三星是第一个声称将使用EUV工具生产芯片的公司,并称将在2018年下半年投入使用。

英特尔发言人表示,一旦这项技术以有效的成本准备就绪,他们将致力于把EUV投入生产。研究指出,英特尔已经购买了比任何其他公司更多的EUV设备。

对于其7nm的EUV工艺,格罗方德将用5步取代15步。

台积电在7nm+ EUV节点之后,5nm工艺将更深入地应用EUV极紫外光刻技术,综合表现全面提升,官方宣称相比第一代7nm EDV工艺可以带来最多80%的晶体管密度提升,15%左右的性能提升或者30%左右的功耗降低。

中芯国际已经向荷兰芯片设备制造商 ASML 购买了一台 EUV 光刻设备,价值1.2亿美元。这也几乎花掉了中芯国际2017年的所有利润,该公司去年的净利润为1.264亿美元。不过在大家了解到 EUV 设备有多重要之后,就知道这笔钱花的有多值了。

ASML将引领EUV的进程

由于EUV的技术难度、需要的投资金额太高,另外两大微影设备厂──日本的尼康和佳能,都已放弃研发。

目前,这两家主要竞争对手均在规模与技术方面落后于公司,ASML以800亿美元市值建立起来的规模,已经将所有竞争对手(以及潜在竞争对手)远远地甩在了身后。

ASML成为了半导体业能继续冲刺下一代先进制程,开发出更省电、运算速度更快的电晶体的最后希望——如果ASML做不了,全球范围内已没有人可以做,摩尔定律会从此消亡。

制造工艺成主要的瓶颈

数字孔径越大,光刻波长越小,则光刻精度越好。因此在学术界如何提升光刻精度是很清楚的,即使用波长较短的光(如紫外线EUV等)以及增大数字孔径使用浸没式光刻等。

大家知道早晚得用EUV,但是出于成本和工艺成熟度考量大家总是希望越晚用EUV越好,能不用EUV就先撑几代再说。

因此就出现了double-pattern(用在16nm)甚至multi-pattern等办法实现在不使用EUV的情况下也能做到超低特征尺寸下的光刻,代价是工艺的复杂性大大上升。到了7nm终于是撑不住了,巨头纷纷开始宣布使用EUV。

当然之前的multi-pattern也不算是走了弯路,因为即使是用了EUV,在未来更小的特征尺寸下估计还是要上multi-pattern。与此同时,ASML在近日也公布了其路线图,并指出其1.5nm光刻技术将足够支持摩尔定律到2030年。

摩尔定律效应递减的国内机会

随着 ASML 将技术蓝图推展至 1.5 纳米,摩尔定律还有至少 10 年的时间。只是,过往半导体制程是每两年前进一个技术时代,未来可能是3—5年才前进一阶,整个产业的效益放缓是必然趋势,这也带给中国半导体大厂一个很好前进追赶的机会,奋力追上主流的工艺技术。

未来半导体世界的竞争,仍会是第一、第二、第三梯次壁垒分明。5 纳米以下技术可行,但技术难度和投资成本拉高,第一梯次包括台积电、三星、英特尔、 GlobalFoundries 已经申请参赛。

摩尔定律的效应趋缓下,代表前方的道路越来越难突破,这提供给中国半导体厂很好追赶的条件,只是技术持续提升的成本投资会大幅垫高,有机会挤入国际第一梯次队伍,这样的投资报酬率很迷人,更让中国芯片自主可控不再是遥不可及的梦想。

结尾:

摩尔定律的主要动力就是成本下降,而在一次性成本快速提升但平均成本却下降有限的时代,摩尔定律的进一步发展动力就不那么强了,EUV 可能会走到它被广泛接受而且能降低生产成本的那一天。

责任编辑:wv

-

摩尔定律

+关注

关注

4文章

634浏览量

78982 -

光刻

+关注

关注

8文章

319浏览量

30153 -

EUV

+关注

关注

8文章

604浏览量

86000

发布评论请先 登录

相关推荐

击碎摩尔定律!英伟达和AMD将一年一款新品,均提及HBM和先进封装

【「大话芯片制造」阅读体验】+芯片制造过程工艺面面观

后摩尔定律时代,提升集成芯片系统化能力的有效途径有哪些?

简述光刻工艺的三个主要步骤

光刻工艺的基本知识

“自我实现的预言”摩尔定律,如何继续引领创新

封装技术会成为摩尔定律的未来吗?

摩尔定律的终结:芯片产业的下一个胜者法则是什么?

光刻成为摩尔定律的前沿 制造工艺成主要瓶颈

光刻成为摩尔定律的前沿 制造工艺成主要瓶颈

评论