在昨天的GTC China 2019大会上,NVIDIA宣布了一款新核弹产品——DRIVE AGX Orin,这是下一代自驾平台,采用全新的NVIDIA GPU及12核ARM CPU,200TFLOPS的性能是上代Xavier的7倍。

为NVIDIA新一代系统级芯片,Orin芯片由170亿个晶体管组成,集成了NVIDIA新一代GPU架构及12核的Arm Hercules CPU——CPU及GPU的具体信息官方都没公布,下一代GPU应该是Turing之后的Ampere安培了,CPU是ARM Cortex-A77之后的下一代,有可能是Cortex-A78,主要面向7nm及5nm工艺。

正因为Hercules CPU是面向7nm或者5nm工艺的,所以大家对DRIVE AGX Orin是很期待的,有可能首发5nm工艺,最次也得是7nm工艺吧,没想到NVIDIA这次真的是保守到家了——Computerbase网站爆料称DRIVE AGX Orin使用的是三星8nm LPP工艺,没有台积电代工的份儿了。

DRIVE AGX Orin是2022年才会问世的,也就是三年后才量产,而三星的8nm LPP工艺实际上是三星10nm工艺的马甲改进版。要知道到了2022年,5nm工艺都不算最先进了,台积电明年就要量产5nm工艺了。

不过话说回来了,NVIDIA在制程工艺上虽然抠了一点,但是对比Xavier还是有很大进步的,毕竟它也只是台积电12nm工艺生产的,DRIVE AGX Orin用上8nm工艺已经是很大进步了。

毫无疑问,使用三星成熟的8nm LPP工艺可以大幅降低成本,不过能效上显然是不能跟7nm、5nm相比的。根据NVIDIA的数据,L5级别的全自动驾驶可以使用2路DRIVE AGX Orin+2组GPU的方案,性能可达2000TFLOPS,也是2000万亿次,这性能比得上一些超算了。

当然,代价就是功耗,这样的系统功耗能达到750W,对比超算的话能效会很高了,Computerbase网站做了一个能效的计算,可以看看。

-

三星电子

+关注

关注

34文章

15859浏览量

180984 -

gpu

+关注

关注

28文章

4729浏览量

128890 -

英伟达

+关注

关注

22文章

3770浏览量

90985

发布评论请先 登录

相关推荐

锐成芯微推出基于8nm工艺的PVT Sensor IP

三星电子:18FDS将成为物联网和MCU领域的重要工艺

三星电子计划在2026年推出最后一代10nm级工艺1d nm

概伦电子NanoSpice通过三星代工厂3/4nm工艺技术认证

台积电3nm工艺稳坐钓鱼台,三星因良率问题遇冷

三星展望2027年:1.4nm工艺与先进供电技术登场

三星与新思科技携手,备战2nm工艺量产

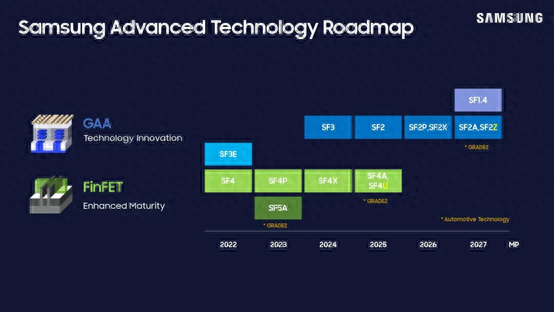

三星公布最新工艺路线图

三星预计2028年AI相关收入将增长九倍

三星电子正按计划推进eMRAM内存制程升级

三星电子开始量产其首款3nm Gate All Around工艺的片上系统

三星电子:加快2nm和3D半导体技术发展,共享技术信息与未来展望

三星电子3nm工艺良率低迷,始终在50%左右徘徊

三星第二代3nm工艺开始试产!

英伟达Orin 的系统结构解析

NVIDIA核弹Orin性能超上代Xavier7倍,使用三星8nm LPP工艺

NVIDIA核弹Orin性能超上代Xavier7倍,使用三星8nm LPP工艺

评论