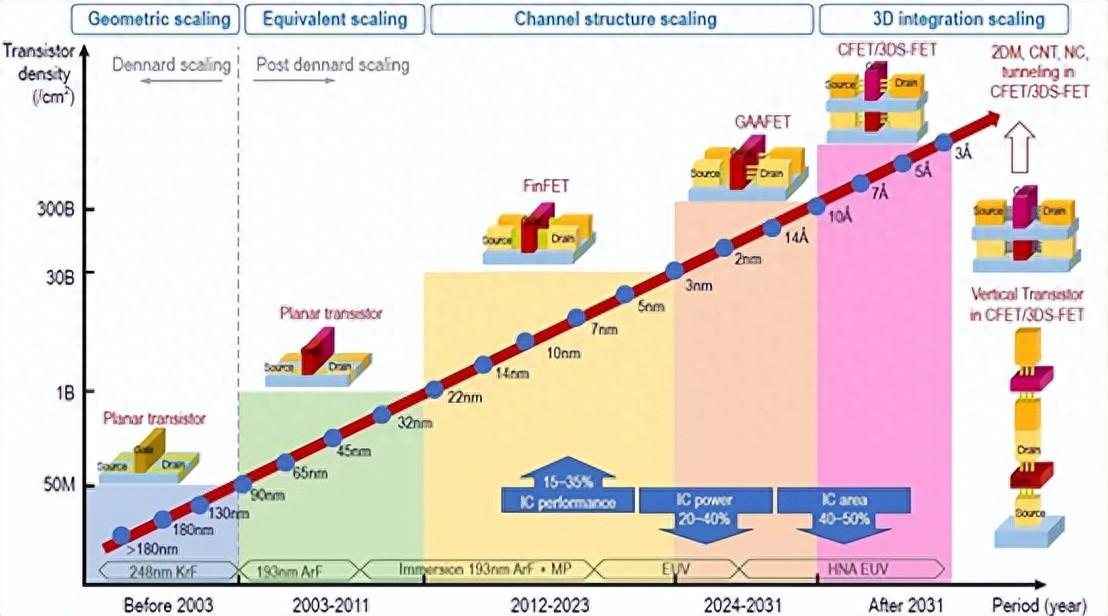

目前,用于计算机处理器的硅集成电路正接近单个芯片上晶体管的最大可行密度,至少在二维阵列中是这样。摩尔定律看似已难以维持。美国密歇根大学一研究团队却另辟蹊径,将晶体管阵列带入三维空间,在最先进的硅芯片上直接堆叠第二层晶体管。这一研究为开发打破摩尔定律的硅集成电路铺平了道路。

摩尔定律认为,集成电路上可容纳的晶体管数目,约每隔两年便会增加一倍。目前硅集成电路的晶体管密度已接近极限。而随着硅晶体管尺寸变得越来越小,它们的工作电压也在不断下降,导致最先进的处理芯片可能会与触摸板、显示驱动器等高电压接口组件不兼容,后者需要在更高电压下运行,以避免错误的触摸信号或过低亮度设置之类的影响。这就需要额外的芯片来处理接口设备和处理器之间的信号转换。

为解决上述问题,密歇根大学研究人员通过附加器件层的单片三维集成,来提高硅互补金属氧化物半导体集成电路的性能。他们首先使用含锌和锡的溶液覆盖硅芯片,在其表面形成均匀涂层,随后短暂烘烤使其干燥,经过不断重复后制成一层约75纳米厚的氧化锌锡膜。使用该氧化锌锡膜制造的薄膜晶体管可以承受比下方硅芯片更高的电压。

为了解决两个器件层之间的电压失配问题,研究人员采用了顶部肖特基、底部欧姆的接触结构,在触点添加的肖特基门控薄膜晶体管和垂直薄膜二极管具有优良的开关性能。测试显示,在集成了高压薄膜晶体管后,基础硅芯片仍然可以工作。

研究人员表示,硅集成电路在低电压(约1伏)下工作,但可以通过单片集成薄膜晶体管来提供高电压处理能力,从而免除了对额外芯片的需求。他们的新方法将氧化物电子学的优势引入到单个硅晶体管中,有助于更紧凑、具有更多功能的芯片的开发。

-

芯片

+关注

关注

455文章

50697浏览量

423040 -

集成电路

+关注

关注

5387文章

11520浏览量

361559 -

摩尔定律

+关注

关注

4文章

634浏览量

78988

发布评论请先 登录

相关推荐

击碎摩尔定律!英伟达和AMD将一年一款新品,均提及HBM和先进封装

奇异摩尔专用DSA加速解决方案重塑人工智能与高性能计算

NMOS晶体管和PMOS晶体管的区别

“自我实现的预言”摩尔定律,如何继续引领创新

3通道达林顿晶体管阵列作用是什么?

微电子所在《中国科学:国家科学评论》发表关于先进CMOS集成电路新结构晶体管的综述论文

封装技术会成为摩尔定律的未来吗?

泰来三维|文物三维扫描,文物三维模型怎样制作

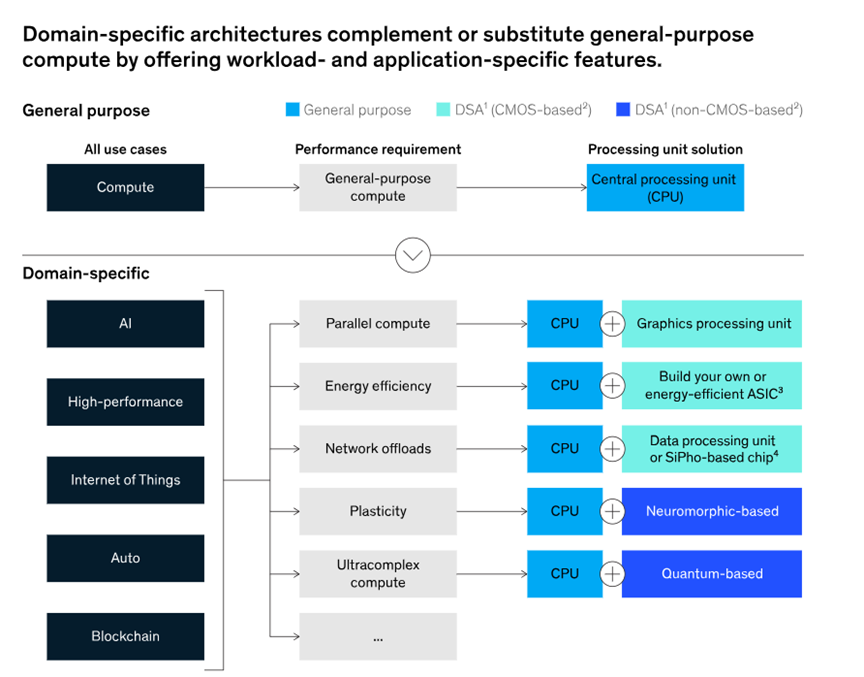

摩尔定律的终结:芯片产业的下一个胜者法则是什么?

三维晶体管阵列有望打破摩尔定律

三维晶体管阵列有望打破摩尔定律

评论