我们设计电路图的时候,器件管脚之间的连线都是理想化的,但在实际的电路板上要通过有一定宽度、长度、厚度的导线进行连接,而且相邻的导线之间还会由于电磁作用互相影响,实际的走线是有一定的阻抗、感抗、容抗的,导致了PCB上一系列干扰、串扰、信号完整性等问题。要保证PCB达到你设计所预期的性能,就要基于电磁场理论对“传输线”进行有效的设计。

相信大家时不时的都会听到传输线(Transmission Line,TL)的概念,在信号完整性分析中占据重要地位。这一期我们就浅显的学习下其基本概念和特性。 电路系统是器件(Device)和连线(Interconnect)的整体。在电路图中经常使用的是理想连线。在集成电路中的制造中,连线的实现可能会用到多晶硅,铝线或者铜线。封装过程中的bonding wire可能会用到铝线或者金线。板级pcb走线通常会用到铜线等等。

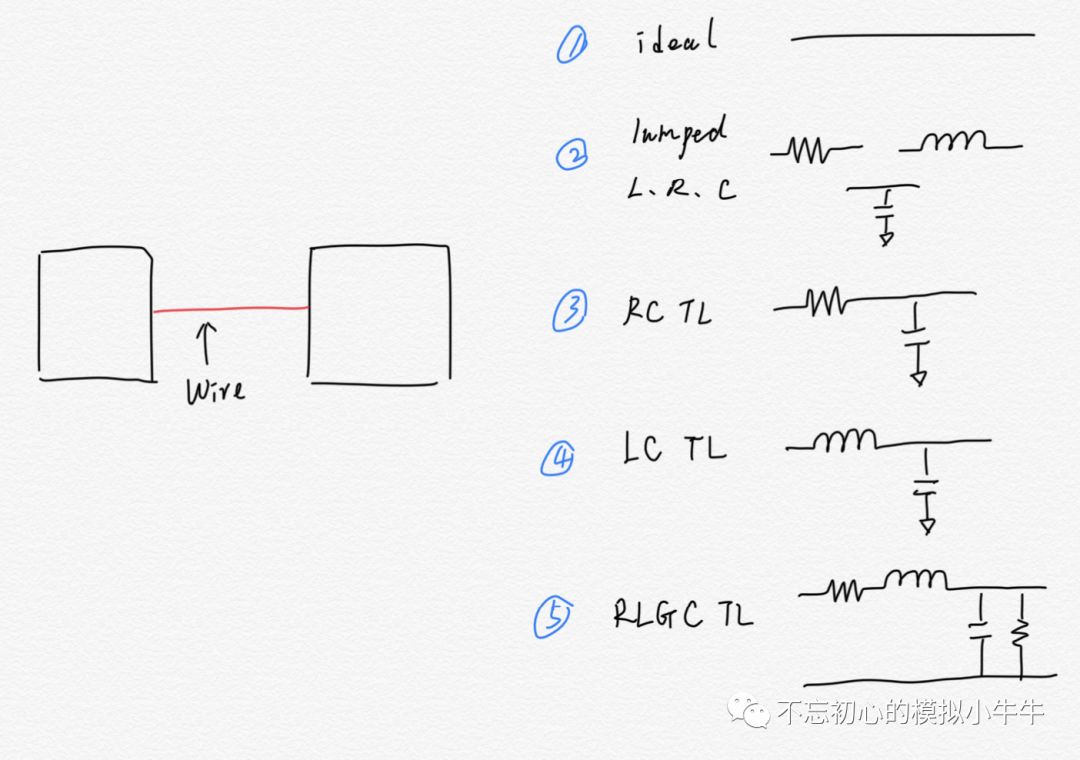

那么实际的互联线的等效模型该怎么表示那?图1给出了简单的示意图。理想走线当然不考虑其走线电阻、电容和电感等电气特性,其特点就是等电势(无延迟)。当然部分场合可根据需要简单等效为集总(lumped)的L、R或C。或者使用复杂的RC模型、LC模型。最后可能是更完整的RLGC模型。

图1 那么是不是什么时候都需要考虑RLGC模型那,当然不是了,这对于电路中成千上万的连线也不现实。图2给出了一些简单的简化等效场景。

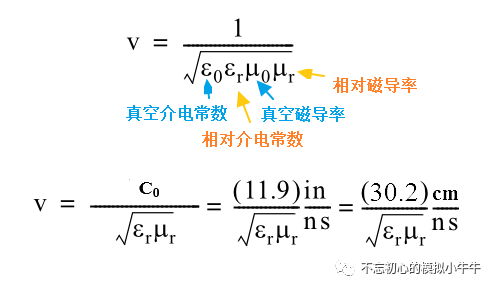

图2 我们都知道信号在导线中的传输,本质上并不是电子的移动,而是电磁场以接近光速进行传播。实际传播速度由材质的相对介电常数εr和相对磁导率μr决定。那么如果知道了传输线的长度l,就可以得到传输线的延迟td=l/v。

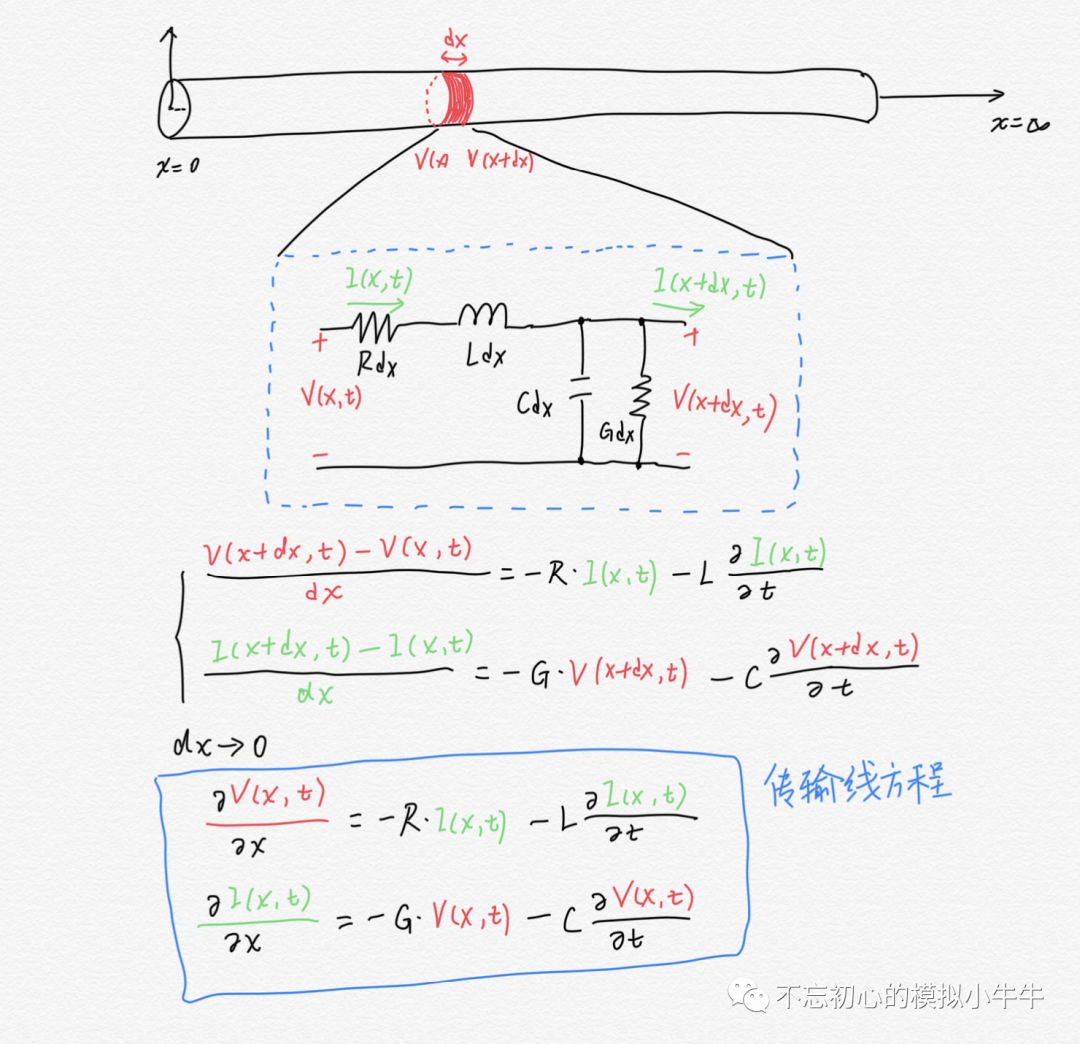

图3 下面重点分析RLGC模型。既然以有限速度传播,那么信号的传播就有先后顺序,图4给出了无限长度传输线中某一点x和无限小增量dx的模型。其中R、L、G和C都是传输线单位长度的电阻、电感、电导和电容。电压和电流都是位置x和时间t的函数,偏微分方程中当位置增量dx无限趋近于0时,能够得到著名的传输线方程,也叫电报方程(telegraph equation )。

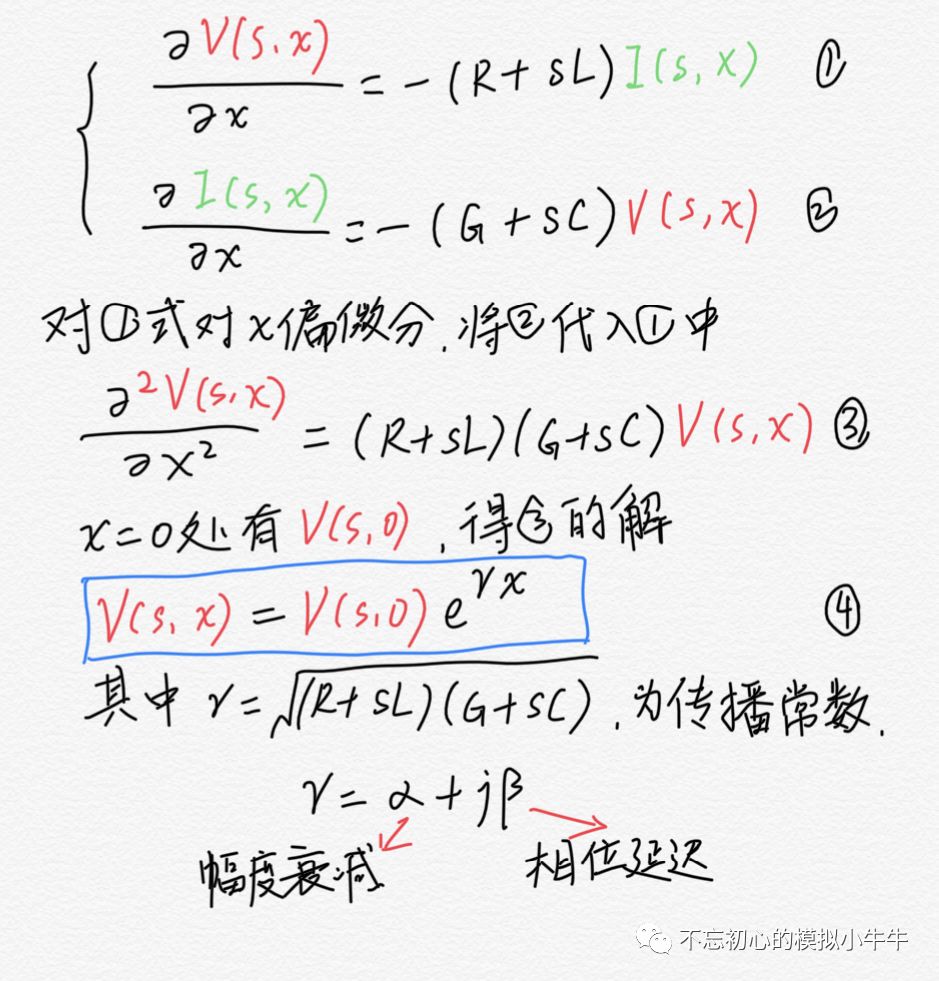

图4 对传输线方程进行拉式变换并求解得到位置为x处的信号和x=0处信号的关系。如图5中④式。其中γ称之为传播常数(propagation constant)。表明信号在传输线上传输时随着传输距离x和频率会发生变化。实部α影响单位距离幅度衰减,虚部β影响单位距离相位延迟。

图5 对于传输线的阻抗计算,图6给出思路,首先假设无限长度传输线的输出阻抗为Z0如图6(a),那么在(a)的基础上,再增加无限小长度dx,取极限dx→0,阻抗仍然应该是Z0,如图5(b)所示。最终我们得到的阻抗Z0的表达式。可以看到这是个和频率及RLGC有关的量。当然如果不考虑R和G,也就是LC模型,也称之为无损传输线(Lossless TL)模型。其阻抗就和频率无关,也就是常说的无损传输线的特征阻抗(L/C)^0.5。

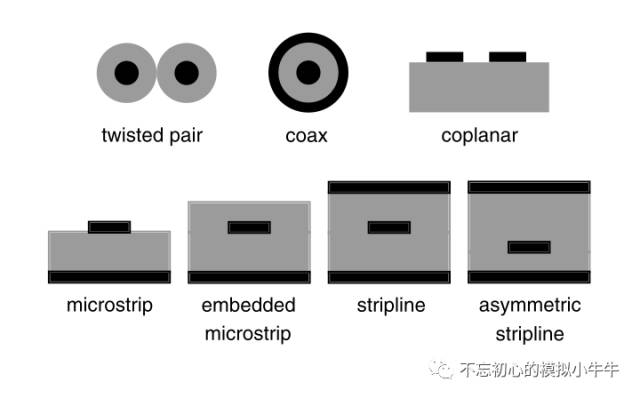

图6 当然对于实际的的传输线为保证其阻抗恒定,避免出现阻抗不连续。需要传输线在其整个长度上具有均匀性(uniform)。图7为一些常见pcb走线(trace)的剖面示意图。包含了常见的双绞线、同轴线,微带线,带状线等剖面图。在需要控制传输线的特征阻抗时,需要通过控制走线的宽度、厚度、间距等来设计L和C,从而达到可控阻抗(Controlled Impedance)的目的。比如常见的50欧姆。

图7 关于阻抗还可以形象地从信号的角度理解,信号在通过传输线的过程中需要对线上电容进行充电,对于一定的输入信号幅度,瞬时电流的大小反映了瞬时阻抗( instantaneous impedance),如果传输线在其传输的路径上是均匀的,信号能"看到"的阻抗就是固定的。如图8所示。

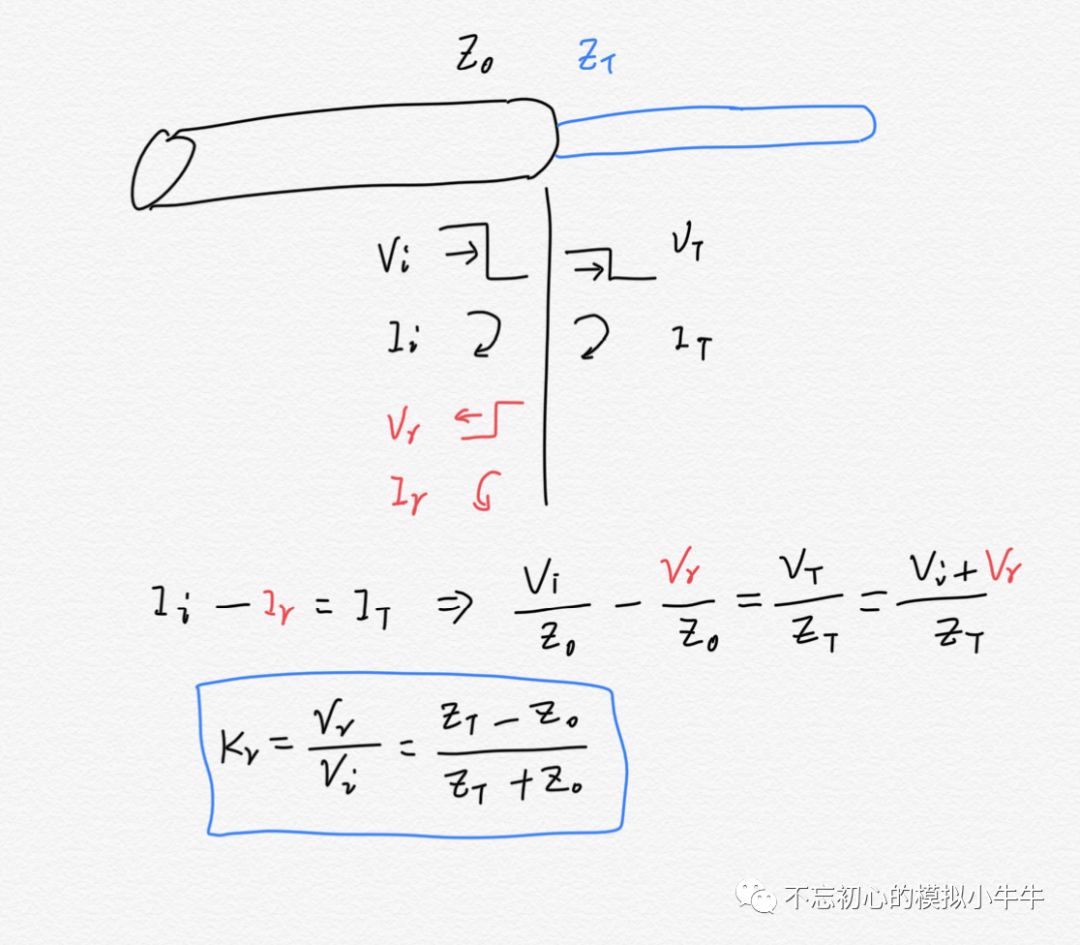

图8 之所以要讨论传输线的特征阻抗,是因为在信号的传输过程遇到了阻抗不连续(不相等)就会出现信号的反射(Reflection)现象。也就是部分信号在不连续点继续前进,部分折返朝源端传播。对于这种情况有反射系数的定义。如图9,当传输线出现阻抗为Z0和ZT的不连续处,需要通过反射电压Vr的定义才能满足边界条。从而得到反射系数Kr的定义,即反射电压Vr和入射电压Vi的比例。

图9 反射现象会影响到信号完整性,在实际的传输线应用中,当传输线设计是均匀一致时,为减小和避免反射问题,通常也需要传输线两端的终端匹配的问题,通过端接电阻达到匹配目的,尽可能的使Kr接近0。降低由阻抗不连续引起的反射量。 所以,理想的连线和现实的导线是有差别的。平时遇到的各种坑,不是说理论就这样,往往需要考虑也实际情况。

-

电路图

+关注

关注

10493文章

10764浏览量

557166 -

电路板

+关注

关注

140文章

5344浏览量

108965 -

连线

+关注

关注

0文章

4浏览量

8329

发布评论请先 登录

深耕电路板加工8年,从踩坑到精通,这些实操经验帮你少走90%弯路

电路板电阻推力测试怎么做?推拉力测试机测试方法与标准解析

电路板维修越修越懵?这些痛点你中了几个,学会少走3年弯路!

Visionfive板和蚀刻SD卡,将电路板连接到HDMI时,什么也没显示,为什么?

探索Broadcom ezPyro™ 背板电路板:开启红外传感评估新旅程

电路板离子污染的核心危害和主要来源

FCT自动测试设备:电路板性能检测利器

了解电路板气密性检测仪,让电路板品控更靠谱-岳信仪器

采购二手 ABB 主板必看:电路板 / 板卡的 5 大避坑检测要点

【案例3.9】电路板无法启动的故障分析

电路板上的连线也存在的坑

电路板上的连线也存在的坑

评论