RS-485总线广泛应用于通信、工业自动化等领域,在实际应中,通常会遇到是否需要加上下拉电阻以及加多大的电阻合适的问题,下面我们将对这些问题进行详细的分析。

一、为什么需要加上下拉电阻?

1.当485总线差分电压大于+200mV时,485收发器输出高电平;

2.当485总线差分电压小于-200mV时,485收发器输出低电平;

3.当485总线上的电压在-200mV~+200mV时,485收发器可能输出高电平也可能输出低电平。但一般总处于一种电平状态,若485收发器的输出低电平,这对于UART通信来说是一个起始位,此时通信会不正常。

当485总线处于开路(485收发器与总线断开)或者空闲状态(485收发器全部处于接收状态,总线没有收发器进行驱动)时,485总线的差分电压基本为0,此时总线就处于一个不确定的状态。同时由于目前485芯片为了提高总线上的节点数,输入阻抗设计的比较高,例如输入阻抗为1/4单位阻抗或者1/8单位阻抗(单位阻抗为12kΩ,1/4单位阻抗为48kΩ),在管脚悬空时容易受到电磁干扰。

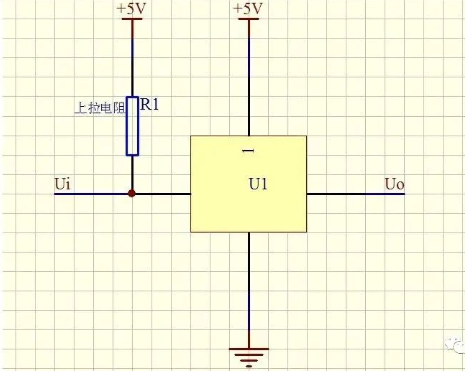

因此为了防止485总线出现上述情况,通常在485总线上增加上下拉电阻(通常A接上拉电阻,B总线下拉电阻)。若使用隔离RS-485收发模块(例如RSM485PCHT),由于模块内部具有上下拉电阻(对于RSM485PCHT,内部上下拉电阻为24kΩ),因此在模块外部一般不需要增加上下拉电阻。

二、什么情况下需要加上下拉电阻?

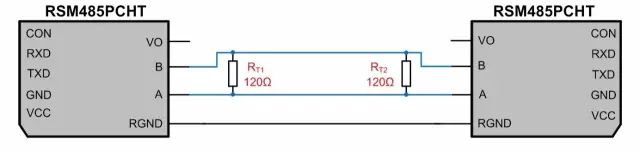

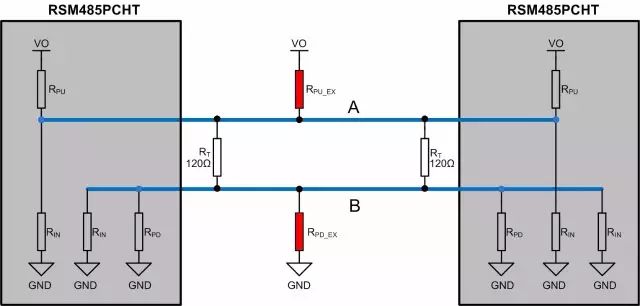

当遇到信号反射问题时,通常会通过增加匹配电阻来避免信号反射,以1对1通信为例,如图1所示。由于485总线通常使用特性阻抗为120Ω的双绞线,因此在485总线的首尾两端增加120Ω终端电阻来避免信号反射问题。

图1:两个RSM485PCHT模块通信电路

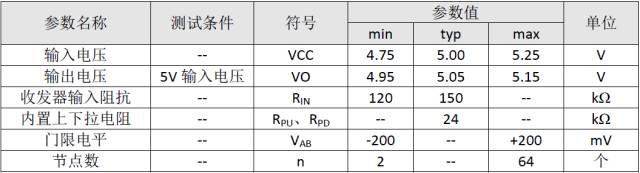

根据RSM485PCHT的具体参数(如表1)可以得到如图2所示等效电路,其中RPU、RPD为模块内部在485总线上加的上下拉电阻,RIN为模块的输入阻抗。

表1 RSM485PCHT参数

图2:RSM485PCHT通信等效示意图

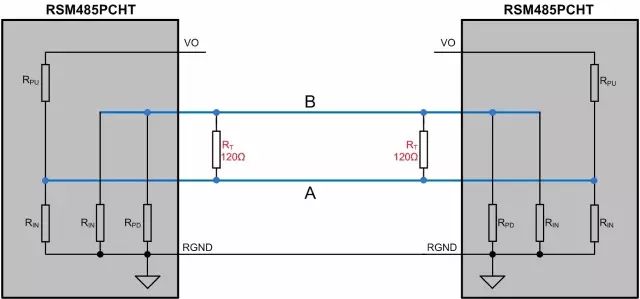

当两个模块都处于接收状态时,可以根据基尔霍夫电流定律对节点A和节点B列出下列公式:

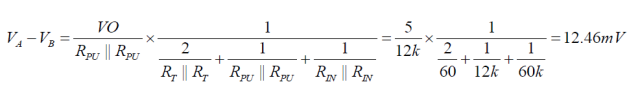

根据上述公式可以计算AB之间的差分电压为:

此时模块已处于不确定状态,模块接收器可能输出为高电平,也可能输出为低电平,这时就需要在模块外部增加上下拉电阻保证模块在空闲时不处于不确定状态。

三、上下拉电阻如何取?

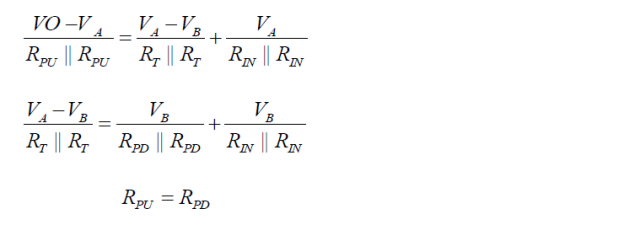

假设模块的输出电源电压V¬O相同,由于RGND接在一起,因此可以认为模块内部的上拉电阻是并联在一起的,为了方便解释,对图2的电路进行整理,如图3所示,在模块外部增加上下拉电阻可以选择只增加一组,也可以选择在每个模块都增加上下拉电阻,为了解释方便,我们在485总线上增加一组上下拉电阻。

图3 :RSM485PCHT通信等效电路图

其中:

RPU为模块内部上拉电阻,RPD为模块内部的下拉电阻,本例中为24kΩ;

RIN为模块接收器输入阻抗,本例取最小值为120kΩ;

RT为终端电阻,本例取120Ω;

RPU_EX为模块外部所加的上拉电阻,RPD_EX为模块外部所加的下拉电阻;

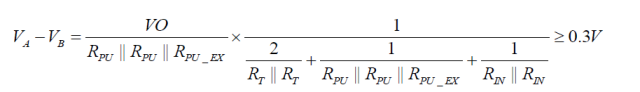

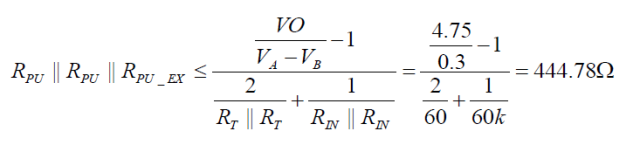

由于RSM485PCHT的门限电平为-200mV~+200mV,一般留有100mV或200mV的电压裕量,本例留有100mV的电压裕量,根据前面所推导的差分电压公式,可以得到下面计算公式:

由于RSM485PCHT在供电电压范围为4.75V~5.25V,取VO=4.75V(最低输入电压VCC=4.75V情况下),可得:

由RPU=24kΩ,可得RPU_EX=RPD_EX=461.9Ω,由于计算出的电阻值为最大值,因此可以选择在485总线上仅加一组410Ω或390Ω的上下拉电阻,或者加两组910Ω上下拉电阻。

四、如何验证上下拉电阻取值?

上述计算仅考虑了485总线空闲状态时不处于不确定状态,并没有考虑485收发器的驱动能力和所用元器件的功耗等问题。外部所加上下拉电阻越小,可以将485总线空闲状态差分电压保持的越高,但与此同时,终端电阻和上下拉电阻的功耗也越大,对485收发器的驱动能力要求也越高,当超过485收发器的驱动能力时,也会导致通信失败。

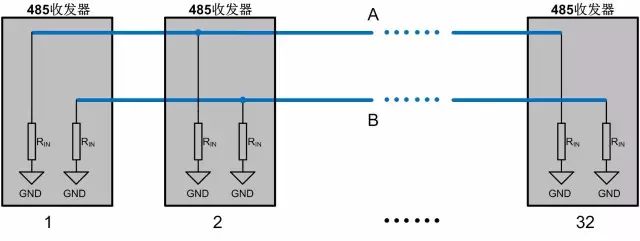

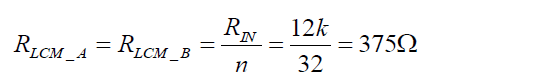

根据RS-485标准,当接收器的输入阻抗为单位阻抗时(最小为12k),总线上最多可以接32个节点,485的差分负载最大为54Ω,此时差分输出电压最小为1.5V。

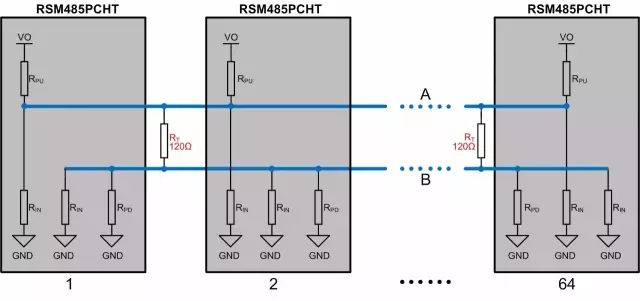

图4 :485总线连接32个节点等效示意图

如图4所示,我们可以看到当485总线上接有32个节点时,总线A或B的共模负载为:

由此可见,对于RS-485的标准来说,A总线或B总线的最大共模负载为375Ω。

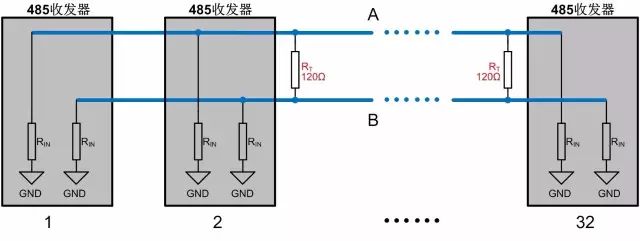

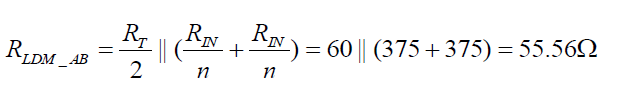

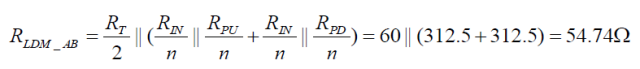

图5 :485总线增加终端电阻等效示意图

当增加终端电阻后,可以发现485总线的共模负载没有发生变化,但差模负载急剧减小,差模负载为:

因此当485总线的节点数达到最多以及增加终端电阻后,485总线的差模负载仍大于54Ω,根据RS-485的标准,差分输出电压最小为1.5V。

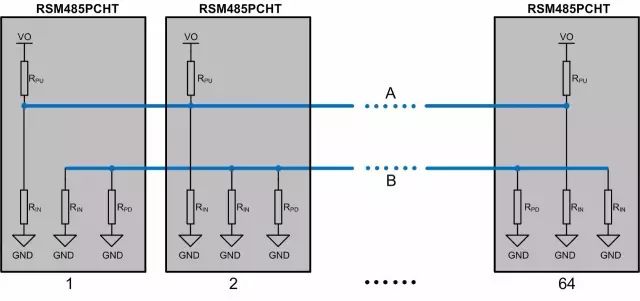

图6 :RSM485PCHT 64个节点等效示意图

以RSM485PCHT为例说明增加上下拉电阻的情况,如图6所示,总线A或B的共模负载为:

实际测试上述情况,驱动输出的最小差分电压3.02V,这个电压远大于RS-485标准规定的最小差分输出电压1.5V。

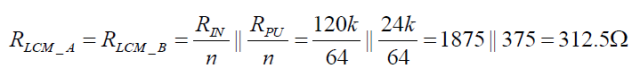

图7 :RSM485PCHT 64个节点增加终端电阻示意图

当在485总线上增加终端电阻时,可以看出总线A或B的共模负载并没有发生变化,而差分阻抗有了较大的变化,此时差模负载为:

计算出的差模负载要略大于RS-485标准规定的最大负载为54Ω,我们对RSM485PCHT进行实际测试,其输出差分电压1.58V,略大于标准规定的最小电压。

当差模负载为54Ω(485总线接两个120Ω终端电阻并且上拉电阻(下拉电阻)与收发器内阻的并联值为270Ω)时,RSM485PCHT的差分输出电压为1.52V(实测值),基本和RS-485标准相同。当差模负载为41.54Ω(485总线接两个120Ω终端电阻并且上拉电阻(下拉电阻)与收发器内阻的并联值为135Ω)时,RSM485PCHT的差分输出电压在1.17V左右(实测值),在这种情况下可以通信。但485收发芯片手册中规定的最大差模负载通常为54Ω,即在485总线上增加两个120Ω后,上拉电阻(下拉电阻)与收发器输入阻抗的并联值应大于270Ω。同时为了保证稳定可靠通信,一般485总线的上拉电阻(下拉电阻)与收发器输入阻抗的并联值应大于375Ω。

五、总结

1.通信线应选用屏蔽双绞线,屏蔽层应单点接大地;

2.当我们没有遇到信号反射问题时,尽量不要使用终端电阻;

3.如果使用终端电阻,我们可以通过上下拉电阻调节485总线在空闲状态的电压值,保证不处于门限电平(-200mV~+200mV或-200mV~-40mV)范围内;

4.当我们增加上下拉电阻时,上拉电阻(下拉电阻)与收发器输入阻抗的并联值应大于375Ω。

-

电阻

+关注

关注

86文章

5504浏览量

171883 -

总线

+关注

关注

10文章

2877浏览量

88049

发布评论请先 登录

相关推荐

【RS-485总线】详解RS-485上下拉电阻的选择

电路设计基础:上拉电阻、下拉电阻分析

上拉电阻和下拉电阻的用处和区别介绍

下拉电阻的作用有哪些

STM32cubemx在开漏和推挽输出模式下上拉电阻和下拉电阻有什么作用和区别?

上拉电阻和下拉电阻是什么

下拉电阻选择

下拉电阻选择

评论