(文章来源:cnBeta)

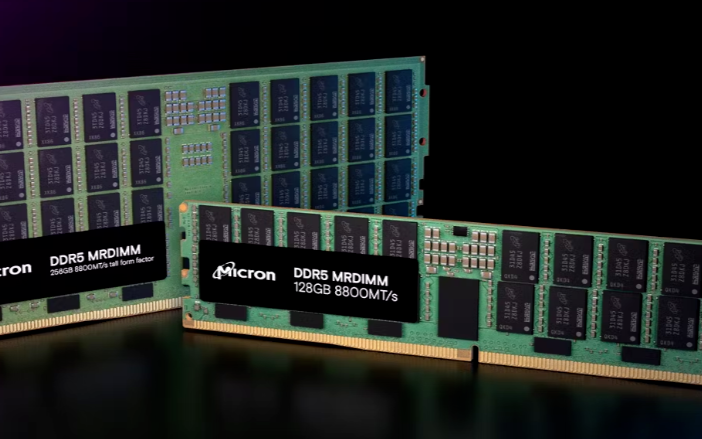

到2024年,美国数据中心市场营收预计将超过 690 亿美元。随着越来越多的企业和个人依赖数据中心的日常使用,软硬件的可靠性,将成为保持这些服务正常运行的关键。实现这一方面的主要目标,就是提高内存的性能。好消息是,美光刚刚宣布已向特定合作伙伴出样基于 DDR5 的 RDIMM 内存。

作为 DDR4 后续产品,DDR5 意味着“第五代双倍速率 SDRAM”,并且引入了重大的改进。以同频的 3200 MT/s 传输速率为例,DDR5 的有效带宽较 DDR4 提升了 1.36 倍。在更高的数据传输速率(4800 MT/s)下,DDR5 的性能更是较 DDR4 提升了 1.87 倍。

在快速扩张的数据和计算密集型应用中,以及随着处理器核心数量的爆发式增长,当前的 DRAM 技术已经面临严重的带宽短缺。不过美光的最新一代 DDR5 DRAM 技术,能够将内存性能提升 85%,为应对下一代服务器的工作负荷做好了充分的准备。

在一众新功能中,占空比调节器(DCA)电路可校正控制器接收的 DQ 和 DQS 信号中出现的小占空比。DQS 间隔振荡器电路允许控制器监视由于电压和温度的变化而导致的 DQS 时钟延迟变化。辅以改进的 READ 前置、命令和地址训练模式,芯片选择、以及写均衡训练模式。写入均衡使得系统能够补偿每个 DRAM 设备的 CK 路径与 DW 和 DWS 路径之间的模块时序差异。借助专用寄存器来读取训练模式,并且可获取命令和地址、芯片选择和 DQ 引脚内的参考电压。

现代数据中心还对存储等部件的可靠性、可用性、可维护性(RAS)提出了更高的要求,但这颗通过 DDR5 的多项功能来实现,比如片上错误校正码(ECC)。

在从 DDR5 器件输出数据之前,可先在 READ 命令期间执行校正,以减轻系统的错误校正负担。设计伊始,DDR5 就已经考虑到了 Hamming 代码的 EDD 实现。DDR5 SDRAM ECC 具有错误检查和清除(ECS)功能,可读取内部数据、并在发生错误时写回校正后的数据,而且支持手动或自动执行。打包后修复(PPR)功能也支持软(sPPR)或硬(HPPR)模式,分别对应永久性修复和临时性修复,且 PPR 具有跟踪资源可用性的能力。启动时,每个 DRAM 设备可确定各个存储体中 PPR 资源的可用性,然后设置一组模式寄存器来追踪信息。

综上所述,美光为 DDR5 SDRAM 产品组合提供了众多功能,旨在为数据中心客户带来更高的性能和更多的创新。

(责任编辑:fqj)

-

内存

+关注

关注

8文章

3010浏览量

73959 -

美光

+关注

关注

5文章

708浏览量

51415

发布评论请先 登录

相关推荐

DDR5内存的工作原理详解 DDR5和DDR4的主要区别

DDR5内存面临涨价潮,存储巨头转向HBM生产

Introspect DDR5/LPDDR5总线协议分析仪

DDR5 MRDIMM内存标准将发,存储厂商方案先行

0706线下活动 I DDR4/DDR5内存技术高速信号专题设计技术交流活动

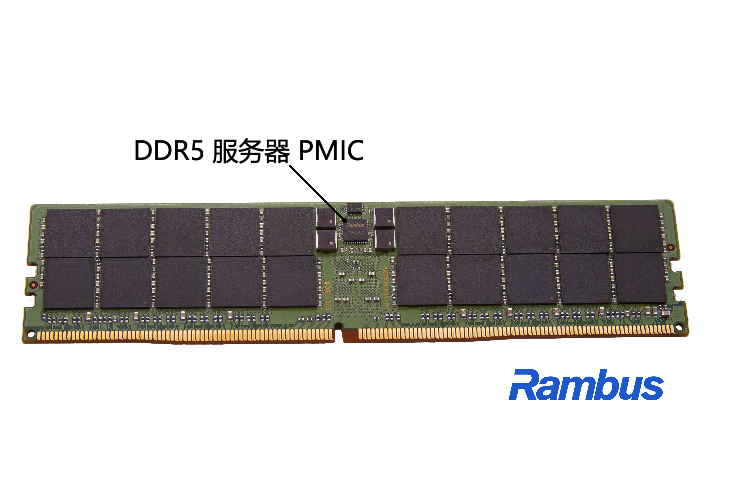

Rambus 通过 DDR5 服务器 PMIC 扩展适用于高级数据中心内存模块的芯片组

Rambus通过全新PMIC系列支持多代基于 DDR5 的高性能服务器

美光率先出货用于AI数据中心的关键内存产品

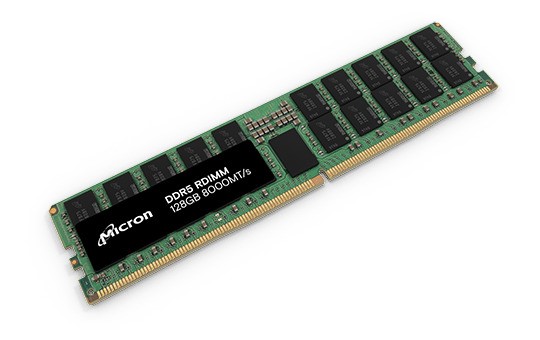

美光科技推出基于大容量32Gb单块DRAM芯片的128GB DDR5 RDIMM内存

美光率先出货用于 AI 数据中心的关键内存产品

美光DDR5技术可助力服务器的内存性能提升85%

美光DDR5技术可助力服务器的内存性能提升85%

评论