AMD近日正式发布了锐龙4000U、锐龙4000H系列移动APU(代号Renoir),采用7nm工艺、Zen 2架构,最多八个CPU核心、八个GPU计算单元(512SP),热设计功耗15/45W。

发布会后,AnandTech参观了AMD的展台,惊喜地发现了锐龙4000 APU的裸片,旁边还摆着64核心128线程撕裂者3990X的裸片,于是测量了一下它们的核心面积。

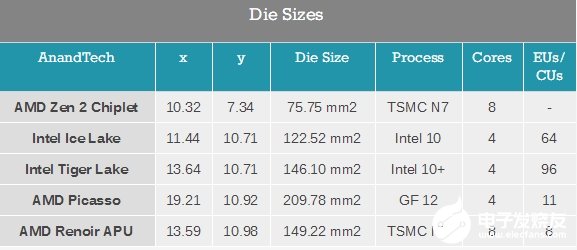

三代锐龙和三代撕裂者都采用了chiplet小芯片设计,每颗CPU Die内有八个核心,实测面积为10.32×7.24=75.75平方毫米(官方内核面积74平方毫米加一些额外填充)。

锐龙4000 APU内核实测长度13.59毫米、宽度10.98平方毫米,面积为149.27平方毫米。

这样的面积下,结合台积电7nm工艺每平方厘米0.09的缺陷指标,锐龙4000 APU的良品率就是90%左右,尽管这并未考虑制造良率,也是相当可观的。

另外,锐龙4000 APU发布之前,就有猜测AMD会如何设计,是四个CPU核心加更多GPU核心,还是八个CPU核心加较少GPU核心。

结果,AMD不但塞进去八个CPU核心、15W热设计功耗下加速频率达到4.3GHz的同时,还放入了八个GPU计算单元并号称性能比上代提升56%,非常精妙,也非常不容易。

顺带一提,GF 12nm工艺制造的锐龙3000 APU面积为209.78平方毫米,有四个CPU核心、11个GPU单元。

10nm+工艺的Intel Tiger Lake面积为146.10平方毫米,有四个CPU核心、96个GPU单元(当然AMD/Intel GPU单元没有直接可比性)。

责任编辑:wv

-

amd

+关注

关注

25文章

5466浏览量

134097 -

APU

+关注

关注

0文章

142浏览量

23719

发布评论请先 登录

相关推荐

16管能穿几根六类网线

用菊花链连接4片/8片/16片ADS1299,菊花链的前八个通道会出现杂波,怎么解决?

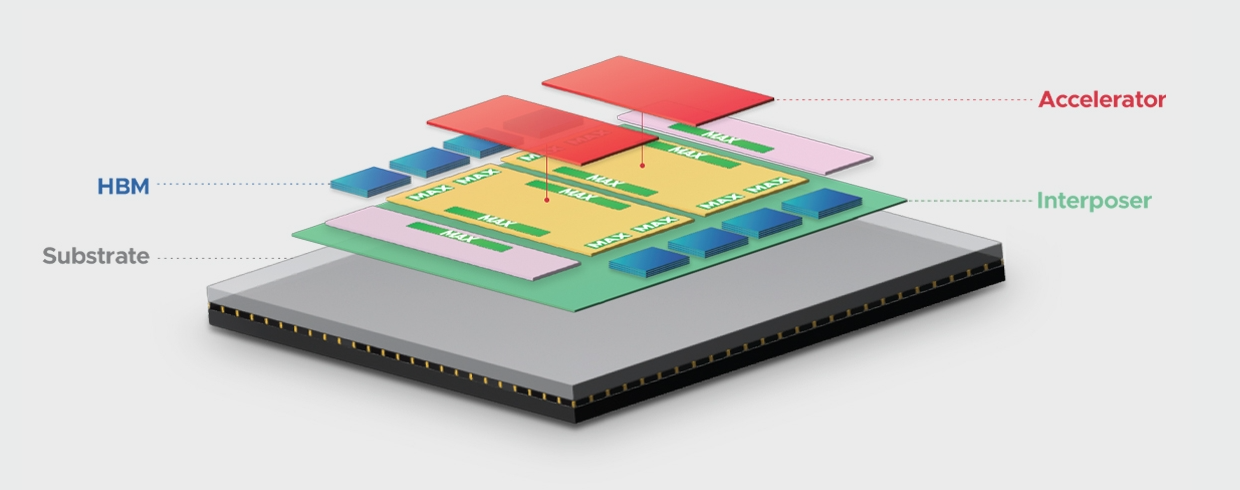

技术前沿探索:玻璃基板嵌入技术(GPE)与玻璃基板扇出封装(eGFO)

lm2902做的二阶低通滤波器,无论怎么调试C1的值,电路的波特图都保持不变,请问一下C1的作用到底有多大?

台积电新版CoWoS封装技术拓宽系统级封装尺寸

台积电将制造两倍于当今最大芯片尺寸的大型芯片,功率数千瓦

英特尔携手桑迪亚构建全球最庞大神经形态系统

探索电动车电池电缆超声金属焊接技术

锐龙4000 APU裸片到底有多大 149.27平方毫米面积竟塞下八个CPU核心

锐龙4000 APU裸片到底有多大 149.27平方毫米面积竟塞下八个CPU核心

评论