据IC Insights发布的最新2020 McClean报告显示,半导体行业研发的投入将在2024年出现明显成效——包括转向EUV光刻,低于3纳米制程技术,3D芯片堆叠技术和先进封装在内的技术挑战有望提升研发增长率。

半导体业务的定义是快速的技术变化以及需要在新材料的研发方面保持高水平的投资,用于日益复杂的芯片设计的创新制造工艺以及先进的IC封装技术。

根据新版提供的数据,尽管半导体行业的整合在过去五年中降低了研发支出的增长率,但长期趋势是自1980年代以来研发支出的年度增长放缓。于2020年1月IC Insights发布的《 McClean报告—集成电路产业的全面分析和预测》的内容。然而,技术挑战包括3D芯堆叠技术,先进工艺中的极紫外光刻技术的发展以及增长产品的复杂性预计将在2019-2024年期间将R&D预算提高一点点(图1)。

数据显示,研发支出趋势涵盖了集成设备制造商(IDM),无晶圆厂芯片供应商和纯晶圆代工厂的支出,并且不包括涉及半导体相关技术的其他公司和组织,例如生产设备和材料供应商,包装和制造商。测试服务提供商,大学,政府资助的实验室和行业合作社,例如比利时的IMEC,法国的CAE-Leti研究所,***的工业技术研究院(ITRI)和美国的Sematech财团, 2015年合并为纽约州立大学(SUNY)理工学院。

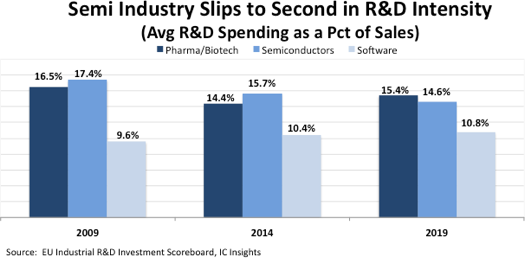

根据IC Insights收集的数据,自1990年代以来,半导体行业在研发强度方面一直领先于所有其他主要工业领域,每年在研发上的支出平均约占总销售额的15%。然而,在过去的三年中,半导体行业的研发销售额占总销售额的比例在2017年下滑至13.5%,在2018年下滑至13.0%,这主要是由于内存IC的收入增长非常快。该行业的研发/销售比例在2019年反弹至14.6%,当时内存IC收入下降了33%,整个半导体市场下降了12%。根据欧盟工业研发投资记分卡报告中的一项全球调查,制药和生物技术领域的研发/销售比率为15.4%,在2019年排名中名列第一(图2)。

在过去的41年中(1978-2019),R&D支出平均占半导体销售额的14.6%。自2000年以来,半导体研发支出占全球半导体销售额的百分比超过了四年(2000年,2010年,2017年和2018年)的历史平均水平。在这四年中,较低的研发与销售比率与收入增长的优势更多地联系在一起,而不是研发支出的劣势。

-

半导体

+关注

关注

334文章

27426浏览量

219221 -

3D芯片

+关注

关注

0文章

52浏览量

18425 -

EUV

+关注

关注

8文章

607浏览量

86046

发布评论请先 登录

相关推荐

到2024年,半导体研发将促EUV光刻、3纳米、3D芯片堆叠技术增长

到2024年,半导体研发将促EUV光刻、3纳米、3D芯片堆叠技术增长

评论