存储技术:不同存储技术的访问时间差异很大。速度较快的技术每字节的成本要比速度较慢的技术高,而且容量小。

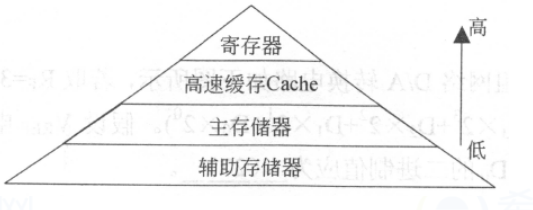

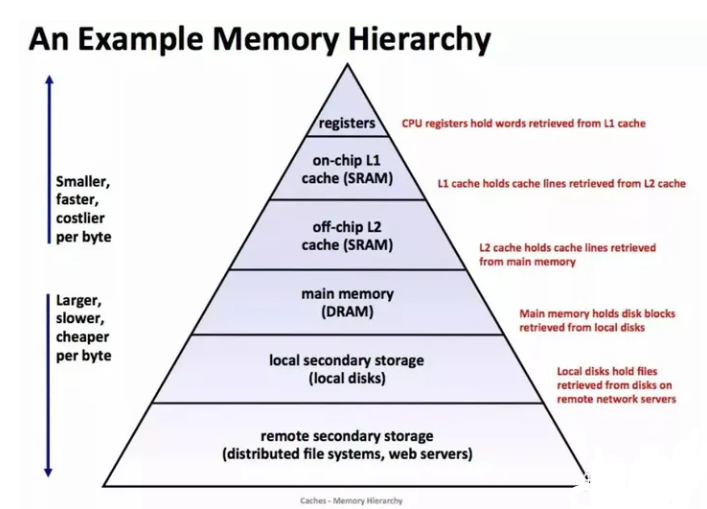

一种组织存储器系统的方法,成为存储器层次结构(memory hierarchy)。如下图所示,是一个典型的存储器层次结构。

一般而言,从高层往底层走,存储设备变得更慢、更便宜和更大。

L0是少量快速的CPU寄存器,CPU可以在一个时钟周期内访问它们。

L1、L2、L3是一个或多个小型到中型的基于SRAM的高速缓存存储器,CPU可以在几个时钟周期内访问它们。

L4是一个大的基于DRAM的主存,CPU可以在几十到几百个时钟周期内访问它们。

L5是慢速但是容量很大的本地磁盘。

L6是一层附加的远程服务器上的磁盘,需要通过网络来访问它们。

存储器层次结构的中心思想是:对于每个k,位于k层的更快更小的存储设备作为位于k+1层的更大更慢的存储设备的缓存。换句话说,层次结构中的每一层都缓存来自较低一层的数据对象。

例如,本地磁盘作为通过网络从远程磁盘取出的文件(如web页面)的缓存,主存作为本地磁盘上数据的缓存,以此类推,直到最小的缓存—CPU寄存器。

如上图所示,第k层的存储器被划分成较少的块的集合,每个块的大小与k+1层的块的大小一样。在任何时刻,第k层的缓存包含第k+1层块的一个子集的副本。

当程序需要第k+1层的某个数据对象d时,首先在当前存储在第k层的一个块中查找d。如果d刚好缓存在第k层,那么就是缓存命中(cache hit)。该程序直接从第k层读取d,根据存储器层次结构的性质,这要比从第k+1层读取d更快。另一方面,如果第k层没有缓存数据对象d,即缓存不命中(cache miss)。当发生缓存不命中时,第k层的缓存从第k+1层缓存中取出包含d的那个块,如果第k层缓存已经满了,就会覆盖现存的一个块。

概况来说,基于缓存的存储器层次结构行之有效,是因为较慢的存储设备比较快的存储设备更便宜,还因为程序倾向于展示局部性:

利用时间局部性:由于时间局部性,同一数据对象可能会被多次使用。一旦一个数据对象在第一次不命中时被复制到缓存中,我们就会期望后面对该目标有一系列的访问命中,从而提高访问速度。

利用空间局部性:块通常包含有多个数据对象,由于空间局部性,我们会期望后面对该块中其他对象的访问能够补偿不命中后复制该块的花费。

-

存储器

+关注

关注

38文章

7492浏览量

163854 -

cpu

+关注

关注

68文章

10863浏览量

211799 -

存储技术

+关注

关注

5文章

737浏览量

45802

发布评论请先 登录

相关推荐

全面解析存储器层次结构原理

存储器的层次结构是怎么样的

存储器的层次结构是怎么样的

评论