3月23日的GTC大会可能是NVIDIA正式揭晓新一代GPU架构的窗口时间。本周,名为KittyCorgi的爆料新人公布了不少Ampere(安培)核心的技术资料,虽说真实性还有待作证,但也不妨先瞧一瞧。

依据这份爆料,Ampere GPU核心面积高达826mm2,如果基于7nm打造的话,晶体管规模将相当恐怖。

具体到内部,对应RTX 3080 Ti的“GA103”核心分为6组GPC单元,每组GPC拥有10个SM单元,一共是60个SM单元,3840个CUDA(若是一个SM单元增加到128个CUDA,那就是7680,基于核心面积,后者可能性倒是更大),显存位宽320bit。此前,RTX 2080 Ti的TU102是72个SM单元,有效68个,总计4608个CUDA。

对应RTX 3080的“GA104”核心同样是6组GPC,每组GPC削减为8个SM单元,一共是48个SM,3072或6144个CUDA,256bit显存位宽,都支持PCIe 4.0。

回到SM单元内部,INT32单元不变,FP32规模翻倍,Tensor Core翻倍,L1增大,光追单元升级为RT Core Advanced。

期待老黄尽快揭晓Ampere、Hopper……

责任编辑:wv

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

相关推荐

雪崩晶体管(Avalanche Transistor)是一种具有特殊工作特性的晶体管,其核心在于其能够在特定条件下展现出雪崩倍增效应。以下是对雪崩晶

![的头像]() 发表于

发表于 09-23 18:03

•919次阅读

晶体管作为电子电路中的核心元件,其基本工作模式对于理解其工作原理和应用至关重要。晶体管的工作模式主要可以分为两大类:放大模式和开关模式。这两种模式基于晶体管内部PN结的特性,通过控制输

![的头像]() 发表于

发表于 09-13 16:40

•857次阅读

CMOS晶体管尺寸规则是一个复杂且关键的设计领域,它涉及到多个方面的考量,包括晶体管的性能、功耗、面积利用率以及制造工艺等。以下将从CMOS晶体管

![的头像]() 发表于

发表于 09-13 14:10

•1840次阅读

NMOS晶体管和PMOS晶体管是两种常见的金属氧化物半导体场效应晶体管(MOSFET)类型,它们在多个方面存在显著的差异。以下将从结构、工作原理、性能特点、应用场景等方面详细阐述NMOS晶体管

![的头像]() 发表于

发表于 09-13 14:10

•3371次阅读

一、引言 有关系。随着集成电路技术的飞速发展,芯片晶体管作为电子设备的核心元件,其性能的优化和制造技术的提升成为了行业关注的焦点。在晶体管的众多设计参数中,深度和宽度是两个至关重要的因

![的头像]() 发表于

发表于 07-18 17:23

•679次阅读

晶体管是一种半导体器件,广泛应用于电子电路中。晶体管的工作原理基于半导体材料的导电特性,通过控制基极电流来调节集电极电流,从而实现放大、开关等功能。晶体管的电流关系是其

![的头像]() 发表于

发表于 07-09 18:22

•1624次阅读

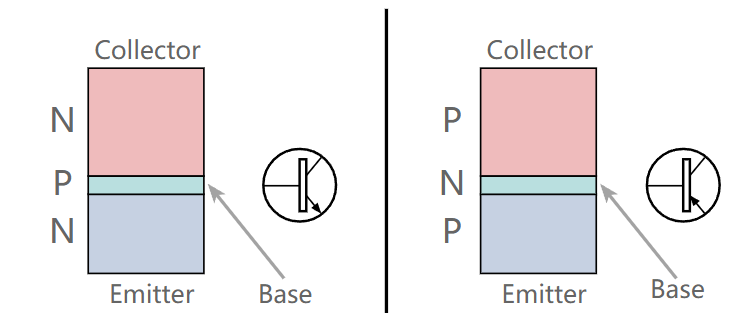

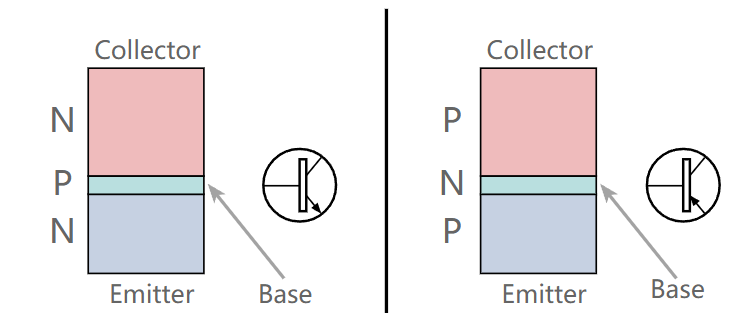

PNP晶体管是一种双极性晶体管,用于电子电路中放大、开关和控制电流的器件。与NPN晶体管相对应,PNP晶体管的结构特点在于其三个不同的半导体

![的头像]() 发表于

发表于 07-01 17:45

•2554次阅读

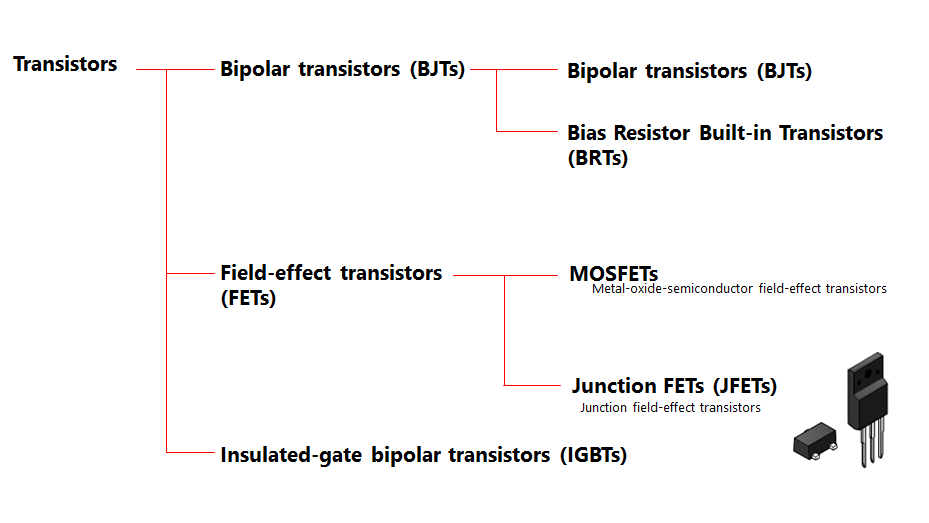

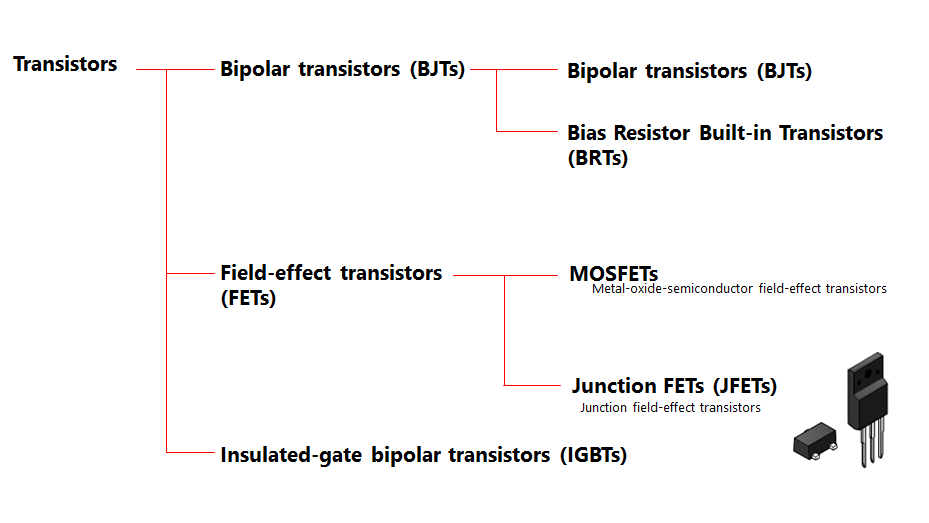

坚实的基础,更为后来的集成电路、大规模集成电路乃至超大规模集成电路的诞生和发展提供了可能。本文将详细探讨晶体管的分类及其作用,以期为读者提供一个全面且深入的理解。

![的头像]() 发表于

发表于 05-22 15:17

•979次阅读

,推理能力提升 15 倍

GB200由两个B200Blackwell GPU和一个基于Arm的Grace CPU组成,采用[台积电]4纳米工艺制程,共有2080亿个[晶体管],其AI性能为每秒20

发表于 05-13 17:16

陆行之表示,相比于其前身“Hopper”100的800亿晶体管,“Blackwell”100拥有的2080亿晶体管数量超过了前者1280亿。此外,尽管两款GPU均采用台积电的4纳米技术加工,但“Blackwell”100通过封装

![的头像]() 发表于

发表于 03-20 09:24

•733次阅读

苹果M3芯片的晶体管数量相当可观,相比前代产品有了显著的提升。这款芯片搭载了高达250亿个晶体管,比M2芯片多出50亿个,这样的设计使得M3

![的头像]() 发表于

发表于 03-11 16:45

•910次阅读

达林顿晶体管(Darlington Transistor)也称为达林顿对(Darlington Pair),是由两个或更多个双极性晶体管(或其他类似的集成电路或分立元件)组成的复合结构。通过这种结构,第一个双极性

![的头像]() 发表于

发表于 02-27 15:50

•5412次阅读

晶体管并联时,当需要非常大的电流时,可以将几个晶体管并联使用。因为存在VBE扩散现象,有必要在每一个晶体管的发射极上串联一个小电阻。电阻R用

发表于 01-26 23:07

管子多用于集成放大电路中的电流源电路。

请问对于这种多发射极或多集电极的晶体管时候该如何分析?按照我的理解,在含有多发射极或多集电极的晶体管电路时,如果多发射极或多集电极的每一极分别接到独立的电源回路中

发表于 01-21 13:47

尽管使用带有晶体管的分立电子元件会使用更多元件,但可以定制电路以提供所需的功能。因此,使用分立晶体管和一些附加电子元件的电路是电子电路设计的核心。

![的头像]() 发表于

发表于 01-09 15:21

•1568次阅读

曝NVIDIA新一代GPU晶体管规模将相当恐怖 核心面积高达826mm2

曝NVIDIA新一代GPU晶体管规模将相当恐怖 核心面积高达826mm2

评论