【嘉德点评】该项技术通过在编程期间估计多位快闪存储器的BER,从而改进所述快闪存储器的编程速度,大大提高其性能。

集微网消息,前不久铠侠(原称东芝存储)半导体公司已研发出采用堆叠112层的3D NAND Flash产品,与目前96层的3D NAND产品相比,此次新产品的单位面积记忆容量提高约20%,除了巩固和扩大SSD,PC,智能手机市场外,还将抢占5G、人工智能、自动驾驶等新市场需求。

NAND Flash是目前闪存中最主要的产品,具备非易失,高密度,低成本的优势,其阵列内部包含由晶体管构成的行列单元。在利用NAND进行读写,即对芯片内部编程操作时,需要将电压脉冲施加到正在编程的晶体管,并将电荷注入到晶体管的栅极内部。当使用最大电压脉冲数目后,实际获取的编程电压仍未达到要求电压,则对芯片编程失败。

为描述NAND Flash存储器的可靠性,需要提出一种方法高效而准确地估计存储器中与编程单元相关的位错误率(BER),从而提高存储器的性能,而现有的一些方法通过读取编程到装置中的数据与经编程数据进行比较来估计位错误率,由于此过程中需要消耗大量时间,因此效率极低。

早在2018年7月18日,东芝存储器(现称铠侠)就提出一项名为“用于估计NAND快闪存储器的位错误率的快闪存储器系统和方法”的发明专利(申请号:201810789084.X),申请人为东芝存储器株式会社。

此发明专利涉及提到一种快闪存储器系统和一种用于估计NAND快闪存储器的位错误率的方法,通过在编程期间估计多位快闪存储器的BER,从而改进所述快闪存储器的编程速度。

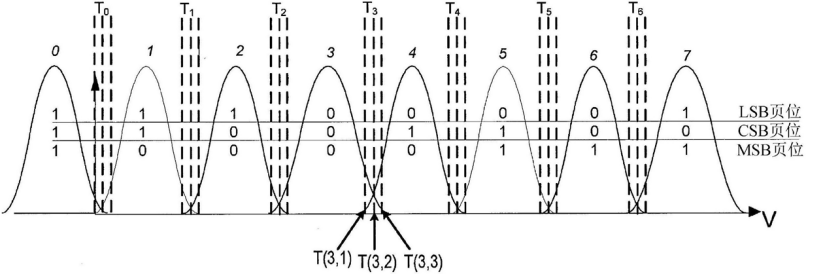

图1

图1是用于BER估计的三位每单元(bpc)快闪存储器装置的电压阈值分布示意图。通常来讲,NAND单元重复的编程和擦除会致使电荷在存储器单元中被捕获,这些电荷可减少单元编程时间,且可在编程和读取过程中引入错误,导致NAND快闪装置的位错误率(BER)增大。此专利提出,针对每一电压阈值设置三个相关的检验阈值,邻近检验阈值之间的差值可为约50mV到100mV,并根据恰好在编程之后(这时估计BER)的每一程序等级的预期电压阈值分布配置阈值差,利用这种增加每状态检验电压阈值的数目来改进所估计的BER的准确性。

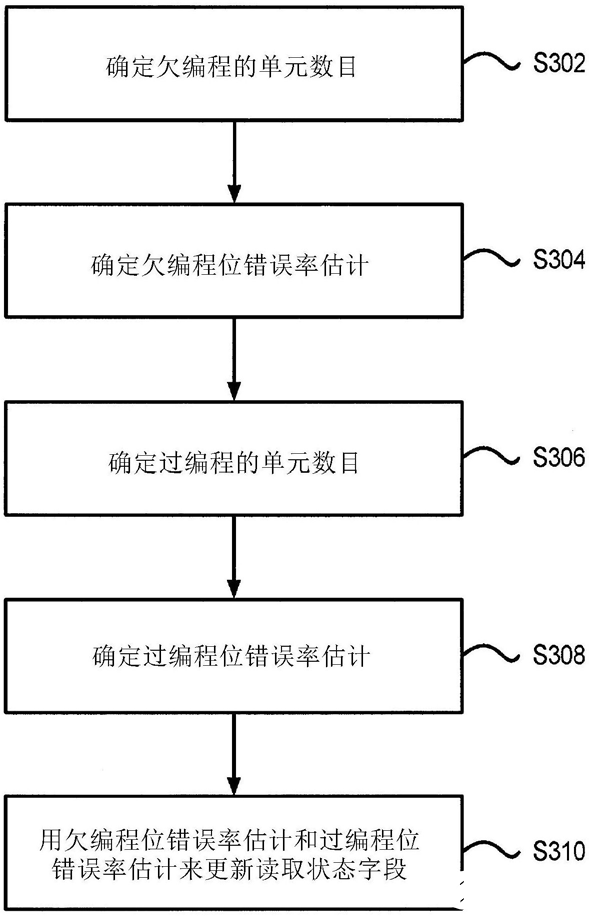

图2

图2是在图1基础上用于估计NAND快闪装置BER的具体方法,采用编程-检验逻辑执行,以在一或多个块的编程期间估计NAND快闪装置内的一或多个块的BER。首先步骤S302中确定与电压阈值相关联的欠编程单元数目,如图1所示,由于每状态有三个检验阈值状态,当单元被编程有第四状态时,内部逻辑可确定具有低于阈值电压的单元数目。在步骤S304中确定针对每一电压阈值的欠编程BER估计值passTHBER。接着在步骤S306中确定欠编程的单元的数目,具体表现为将块内每一单元处的电压电平与三个指定检验阈值水平进行比较,以确定具有高于这些阈值中的每一者的电压值的单元的数目。在步骤308中确定过编程的的BER估计,其值为与所有其它电压阈值相关联的BER值的最大值。最后在步骤S310中用所估计的欠编程的和过编程的BER估计来更新读取状态字段,并读取状态寄存器输出BER估计,并在寄存器中做指示。

NAND Flash作为目前应用极为广泛的非易失性存储器,其性能的提高与成本的降低对未来自动驾驶、人工智能市场有着极大的推动作用,也必将促进半导体市场的创新活力与发展。

-

闪存

+关注

关注

16文章

1814浏览量

115284 -

存储器

+关注

关注

38文章

7552浏览量

164808 -

东芝存储

+关注

关注

0文章

6浏览量

3837

发布评论请先 登录

相关推荐

预期提前,铠侠再次加速,3D NAND准备冲击1000层

【半导体存储】关于NAND Flash的一些小知识

铠侠预测2028年NAND Flash需求将激增2.7倍

铠侠投资360亿日元研发CXL省电存储器

铠侠将开发新型CXL接口存储器

铠侠北上市NAND闪存新工厂竣工,预计2025年秋投产

三星和铠侠持续加大对NAND Flash技术的投入与创新

铠侠瞄准2027年:挑战1000层堆叠的3D NAND闪存新高度

铠侠NAND闪存生产恢复

铠侠计划2030-2031年推出千层级3D NAND闪存,并开发存储级内存(SCM)

NAND存储种类和优势

铠侠半导体估计NAND快闪存储器位错误率的专利

铠侠半导体估计NAND快闪存储器位错误率的专利

评论