3月3日消息,台积电今日宣布,将与博通公司合作强化CoWoS平台。

台积电

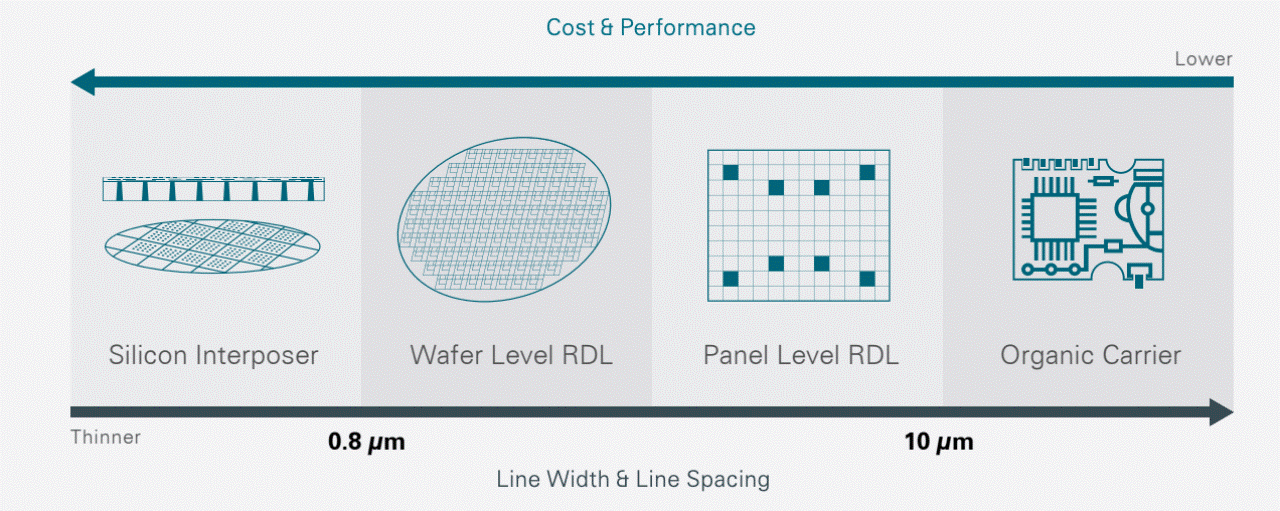

CoWoS全称为Chip-on-Wafer-on-Substrate,是台积电晶圆级系统整合组合(WLSI)的解决方案之一。

台积电和博通将支援业界首创且最大的两倍光罩尺寸(2X reticle size)之中介层,面积约1,700平方毫米。此项新世代CoWoS中介层由两张全幅光罩拼接构成,能够大幅提升运算能力,借由更多的系统单晶片来支援先进的高效能运算系统,并且也准备就绪以支持台积电下一世代的5nm制程技术。

台积电表示,此项新世代CoWoS技术能够容纳多个逻辑系统单晶片(SoC)、以及多达六个高频宽记忆体(HBM)立方体,提供高达96GB的记忆体容量;此外,此技术提供每秒高达2.7兆位元的频宽,相较于台积电2016年推出的CoWoS解决方案,速度增快2.7倍。

CoWoS解决方案具备支援更高记忆体容量与频宽的优势,非常适用于记忆体密集型之处理工作,例如深度学习、5G网络、具有节能效益的数据中心、以及其他更多应用。除了提供更多的空间来提升运算能力、输入/输出、以及HBM整合,强化版的CoWoS技术也提供更大的设计灵活性及更好的良率,支援先进制程上的复杂特殊应用晶片设计。

在台积电与博通公司合作的CoWoS平台之中,博通定义了复杂的上层晶片、中介层、以及HBM结构,台积电则是开发生产制程来充分提升良率与效能,以满足两倍光罩尺寸中介层带来的特有挑战。透过数个世代以来开发CoWoS平台的经验,台积电开发出独特的光罩接合制程,能够将CoWoS平台扩充超过单一光罩尺寸的整合面积,并将此强化的成果导入量产。

CoWoS能够与电晶体微缩互补且在电晶体微缩之外进行系统级微缩。除了CoWoS之外,台积电三维集成电路技术平台,例如整合型扇出(InFO)及系统整合晶片(SoIC),透过小晶片分割与系统整合来实现创新,达到更强大的功能与强化的系统效能。

台积电成立于1987年,是全球最大的晶圆代工半导体制造厂,客户包括苹果、高通、华为等等。其总部位于***新竹的新竹科学工业园区。台积电公司股票在***证券交易所上市,股票代码为2330,另有美国存托凭证在美国纽约证券交易所挂牌交易,股票代号为TSM。

周一收盘,台积电(NYSE:TSM)股价上涨3.97%至55.98美元,总市值约2903.17亿美元。

-

台积电

+关注

关注

44文章

5637浏览量

166513 -

晶圆

+关注

关注

52文章

4912浏览量

127992 -

博通

+关注

关注

35文章

4325浏览量

106917

发布评论请先 登录

相关推荐

台积电进入“晶圆代工2.0”,市场规模翻倍,押注先进封测技术

台积电将与博通合作强化晶圆级封装平台

台积电将与博通合作强化晶圆级封装平台

评论