(文章来源:WikiChip Fuse)

据外媒报道,近日IBM大型商用服务器z15的物理设计(physical design)团队负责人Christopher Berry表示,通过对缓存位线、字线、阵列、供电等方面的调整,他们将z15 SC芯片的总有效缓存密度提高了80%。

2019年下半年,IBM推出了最新的z15大型商用服务器。z15的SC芯片在制程工艺没有改变,核心面积没有增加的情况下,实现了14%的单核性能提升和20%的核心数量增加,同时,芯片的L2缓存增加33%,L3缓存翻倍,L4缓存增加43%。在2020年2月举行的ISSCC会议上,z15物理设计团队负责人Christopher Berry分享了有关缓存性能优化的一些细节问题。

z15中单个SC芯片的L4缓存为960 MiB,相比z14增加了43%,L3缓存从128 MiB翻倍至256 MiB,L2缓存也提升到4 MiB。但最值得注意的是,IBM是在保持相同芯片面积和制程工艺的前提下实现了这些性能的提升。与z14一样,z15采用与格罗方德(GlobalFoundries)共同定制的14纳米FinFET on SOI工艺制成。通过该工艺IBM可以生产出超高密度的DTC eDRAM,这也是IBM十几年来的秘密武器。

该工艺具有超高密度DTC eDRAM。十多年来,eDRAM一直是IBM的秘密武器。即使采用的是14纳米工艺,eDRAM的单元尺寸也达到了0.0174μm。目前,台积电使用尚未量产的5纳米工艺所能制成的最密集的SRAM单元,其尺寸为0.021μm 。

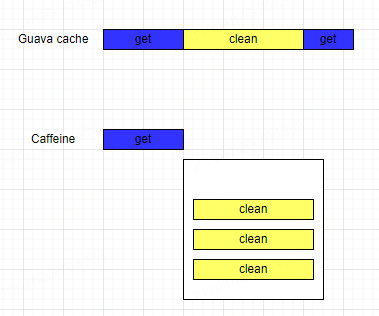

这意味着IBM的14纳米eDRAM单元的密度比迄今为止最密集的5纳米SRAM单元还要高大约20%。IBM物理设计团队通过对z14进行改进,使得z15可以在相同面积内,将位线和字线(bitlines and wordlines)的长度加倍。z14用于L3和L4缓存的原始eDRAM宏块为1 MiB,由16个子阵列组成。每个子阵列包含128个字线和592个位线。而z15的原始eDRAM宏块为2MiB,由8个子阵列组成,每个子阵列具有256个字线和1184个位线。

位线加倍会使电容加倍,从而削弱位线信号。为此,设计团队降低了nFET阈值电压,并引入了偏置电路以改善信号值。为了进一步节省空间,IBM调整了缓存的电源传输网络。z14的高压产生电路是集成在芯片上。而在z15上,他们将这些电路置于片外。

位线和字线的加倍以及子阵列的数量减半意味着可以在阵列内减少相当多的I / O接口。团队预计这些调整大约带来了30%的密度提升,而与供电相关的变化又使密度提升了约38%。总体而言,物理设计团队设法将总有效缓存密度提高了80%。

(责任编辑:fqj)

-

IBM

+关注

关注

3文章

1758浏览量

74725 -

缓存

+关注

关注

1文章

240浏览量

26699

发布评论请先 登录

相关推荐

HTTP缓存头的使用 本地缓存与远程缓存的区别

蓝牙AOA定位系统如何做到高精准度?

同样是函数,在C和C++中有什么区别

两个高速ADC的CLK时钟如何做到同步无相位差?

缓存之美——如何选择合适的本地缓存?

揭秘同样是14nm,缓存翻倍是如何做到的

揭秘同样是14nm,缓存翻倍是如何做到的

评论