Intel之前已经宣布在2021年推出7nm工艺,首发产品是数据中心使用的Ponte Vecchio加速卡。7nm之后的5nm工艺更加重要了,因为Intel在这个节点会放弃FinFET晶体管转向GAA晶体管。

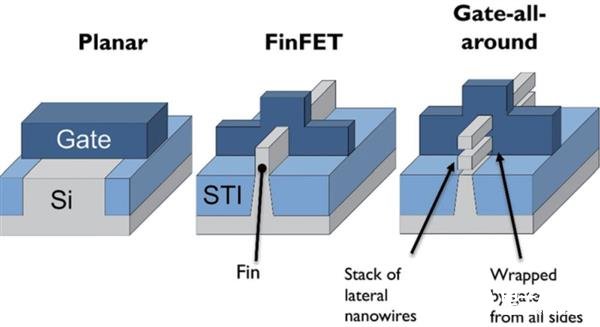

随着制程工艺的升级,晶体管的制作也面临着困难,Intel最早在22nm节点上首发了FinFET工艺,当时叫做3D晶体管,就是将原本平面的晶体管变成立体的FinFET晶体管,提高了性能,降低了功耗。

FinFET晶体管随后也成为全球主要晶圆厂的选择,一直用到现在的7nm及5nm工艺。

Intel之前已经提到5nm工艺正在研发中,但没有公布详情,最新爆料称他们的5nm工艺会放弃FinFET晶体管,转向GAA环绕栅极晶体管。

GAA晶体管也有多种技术路线,之前三星提到他们的GAA工艺能够提升35%的性能、降低50%的功耗和45%的芯片面积,不过这是跟他们的7nm工艺相比的,而且是初期数据。

考虑到Intel在工艺技术上的实力,他们的GAA工艺性能提升应该会更明显。

如果能在5nm节点跟进GAA工艺,Intel官方承诺的“5nm工艺重新夺回领导地位”就不难理解了,因为GAA工艺上他们也是比较早跟进的。

至于5nm工艺的问世时间,目前还没明确的时间表,但Intel之前提到7nm之后工艺周期会回归以往的2年升级的节奏,那就是说最快2023年就能见到Intel的5nm工艺。

责任编辑:wv

-

intel

+关注

关注

19文章

3486浏览量

186776 -

晶体管

+关注

关注

77文章

9829浏览量

139357 -

FinFET

+关注

关注

12文章

253浏览量

90507

发布评论请先 登录

相关推荐

IBM与Rapidus在多阈值电压GAA晶体管技术的新突破

如何测试晶体管的性能 常见晶体管品牌及其优势比较

晶体管与场效应管的区别 晶体管的封装类型及其特点

晶体管的输出特性是什么

晶体管的基本工作模式

CMOS晶体管的尺寸规则

NMOS晶体管和PMOS晶体管的区别

CMOS晶体管和MOSFET晶体管的区别

什么是单极型晶体管?它有哪些优势?

GaN晶体管和SiC晶体管有什么不同

GaN晶体管的基本结构和性能优势

芯片晶体管的深度和宽度有关系吗

PNP晶体管符号和结构 晶体管测试仪电路图

Intel放弃FinFET晶体管转向GAA晶体管 GAA工艺性能提升或更明显

Intel放弃FinFET晶体管转向GAA晶体管 GAA工艺性能提升或更明显

评论